正在加载图片...

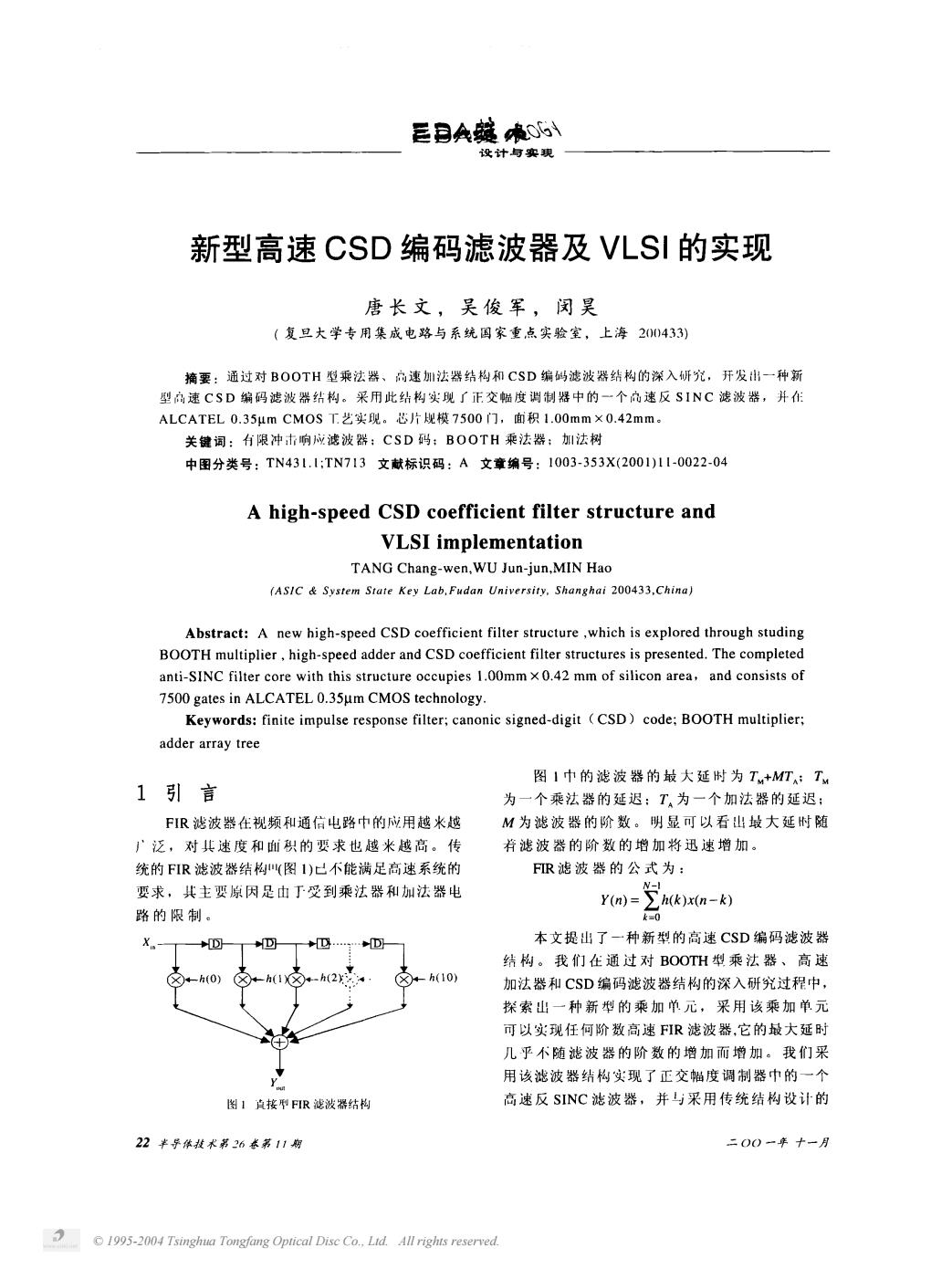

三日A 设计与实现 新型高速CSD编码滤波器及VLSI的实现 唐长文,吴俊军,闵昊 (复旦大学专用集成电路与系统国家重点实验室,上海200433) 摘要:通过对BOOTH型乘法器、速加法器结构和CSD编码滤波器结构的深入研究,开发出一种新 型高速CSD编码滤波器结构。采用此结构实现了正交幅度调制器中的一个速反SINC滤波器,并在 ALCATEL0.35 um CMOS T艺实现。芯片规模7500门,面积1.00mm×0.42mm。 关键词:有限冲击响应滤波器:CSD码:BOOTH乘法器;加法树 中图分类号:TN431.I;TN713文献标识码:A文章编号:1003-353X(2001)11-0022-04 A high-speed CSD coefficient filter structure and VLSI implementation TANG Chang-wen,WU Jun-jun,MIN Hao (ASIC System State Key Lab,Fudan University,Shanghai 200433,China) Abstract:A new high-speed CSD coefficient filter structure which is explored through studing BOOTH multiplier,high-speed adder and CSD coefficient filter structures is presented.The completed anti-SINC filter core with this structure occupies 1.00mm x0.42 mm of silicon area,and consists of 7500 gates in ALCATEL 0.35um CMOS technology. Keywords:finite impulse response filter;canonic signed-digit CSD)code;BOOTH multiplier; adder array tree 图1巾的滤波器的最大延时为TM+MTA;TM 1引言 为一个乘法器的延迟:T为一个加法器的延迟; FIR滤波器在视频和通信电路中的应用越米越 M为滤波器的阶数。明显可以看出坡大延时随 广泛,对其速度和面积的要求也越来越高。传 着滤波器的阶数的增加将迅速增加。 统的FIR滤波器结构(图1)已不能满足高速系统的 FIR滤波器的公式为: 要求,其主要原因是由于受到乘法器和加法器电 N-1 Y(n)=h(k)x(n-k) 路的限制。 k=0 X→回→→巴→D 本文提出了一种新型的高速CSD编码滤波器 结构。我们在通过对BOOTH型乘法器、高速 4-h0) -(10-h(2-h(10) 加法器和CSD编码滤波器结构的深入研究过程中, 探索出一种新型的乘加单元,采用该乘加单元 可以实现任何阶数高速FIR滤波器,它的最大延时 几乎不随滤波器的阶数的增加而增加。我们采 用该滤波器结构实现了正交幅度调制器巾的一个 图1直接型FR滤波器结构 高速反SINC滤波器,并与采用传统结构设计的 22半导体技术第26参第11期 二0O一年十一月 1995-2004 Tsinghua Tongfang Optical Disc Co.,Lid.All rights reserved.© 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved