正在加载图片...

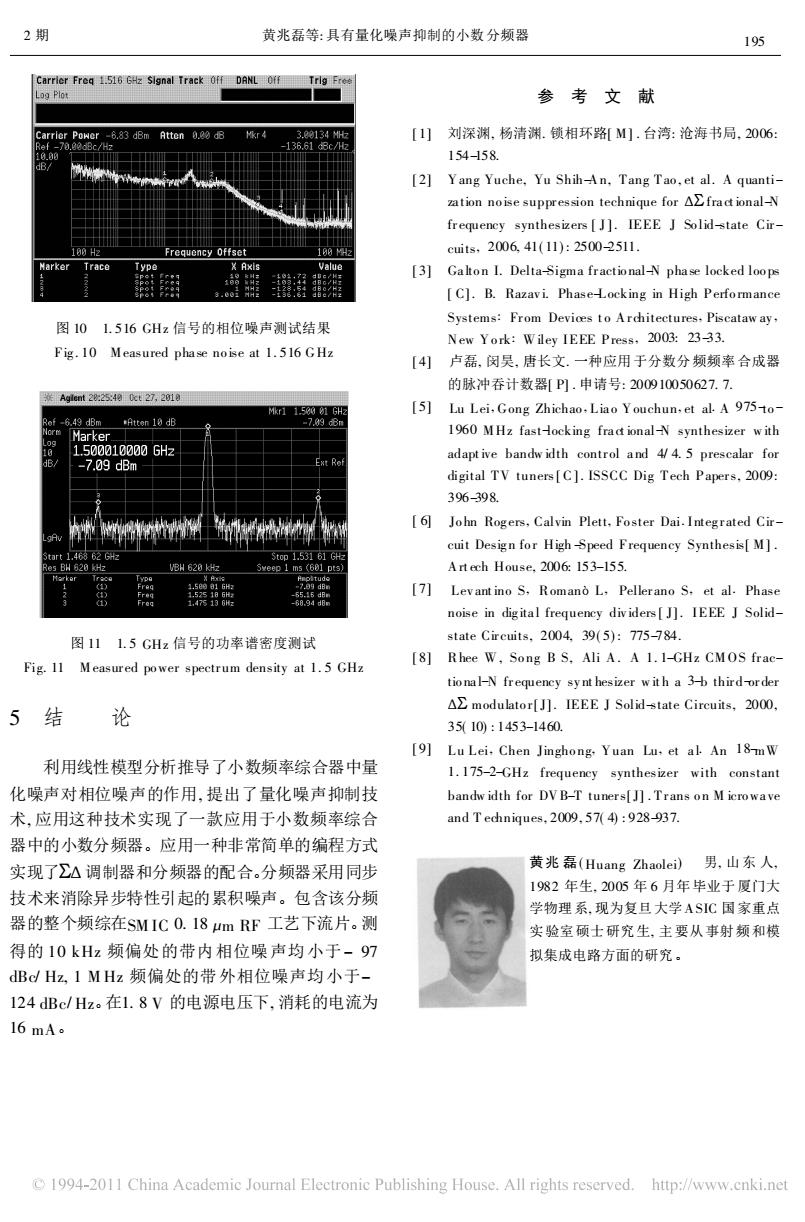

2期 黄兆磊等:具有量化噪声抑制的小数分频器 195 Carrier Freq 1.516 GHz SIgnal Track off DANL Off Trlg Free Log Plot 参考文献 -6.83 dBm Atten 0.00 dB r4 [1]刘深渊,杨清渊.锁相环路M].台湾:沧海书局,2006: 45d 154-158. [2]Yang Yuche,Yu Shih-An,Tang Tao,et al.A quanti- zation noise suppression technique for Afract ional-N frequency synthesizers [J].IEEE J Solid-state Cir- 10H形 Frequency offset cits,2006,41(11):2500-2511. Marker Trace T书e XAxis Value 8:州 [3]Galton I.Delta-Sigma fractional-N phase locked loops C].B.Razavi.Phase-Locking in High Performance 图101.516GHz信号的相位噪声测试结果 Systems:From Devices to Architectures.Piscataw ay, New York:Wiley IEEE Press,2003:23-33. Fig.10 Measured phase noise at 1.516 GHz [4]卢磊,闵吴,唐长文.一种应用于分数分频颜率合成器 的脉冲吞计数器[P].申请号:200910050627.7. ¥Ag1emt2:25:400ct27,2018☐ Mr11509016H [5]Lu Lei.Gong Zhichao.Liao Youchun,et al.A 975-to- Rof -6.49 dBm Atten 10 dB -7.89c8m Marker_ 1960 MHz fast-ocking frac ional-N synthesizer with 1.5000100006H2 adapt ive bandw idth control and 4/4.5 prescalar for -7.09dBm Ext Rof digital TV tuners[C].ISSCC Dig Tech Papers,2009: 396-398. [6]John Rogers,Calvin Plett,Foster Dai.Integrated Cir- cuit Design for High-Speed Frequency Synthesis[M]. tart 1.468 62 GHz Stop 1.531 61 GHz 5BH20H日 BH62 ep1ms(601pts】 Art ech House,2006:153-155. 1.59816 7.9d8 [7]Levant ino S,Roman L,Pellerano S,et al.Phase 1,4751302 noise in digital frequency dividers[J].IEEE J Solid- 图111.5GHz信号的功率谱密度测试 state Circuits,.2004,39(5):775-784. [8]Rhee W,Song B S.Ali A.A 1.1-GHz CMOS frac- Fig.11 Measured power spectrum density at 1.5 GHz tional-N frequency synt hesizer with a 3b third-order 论 AZ modulator[J].IEEE J Solid-state Circuits,2000, 5 结 3510:1453-1460 [9]Lu Lei.Chen Jinghong.Yuan Lu.et al.An 18mW 利用线性模型分析推导了小数频率综合器中量 1.175-2-GHz frequency synthesizer with constant 化噪声对相位噪声的作用,提出了量化噪声抑制技 bandw idth for DV B-T tuners[J].Trans on M icrowave 术,应用这种技术实现了一款应用于小数频率综合 nd T echniques..2009.57(4:928937. 器中的小数分频器。应用一种非常简单的编程方式 实现了∑△调制器和分频器的配合。分频器采用同步 黄兆磊(Huang Zhaolei)男,山东人, 1982年生,2005年6月年毕业于厦门大 技术来消除异步特性引起的累积噪声。包含该分频 学物理系,现为复旦大学ASC国家重点 器的整个频综在SMIC0.18μmRF工艺下流片。测 实验室硕士研究生,主要从事射频和模 得的10kHz频偏处的带内相位噪声均小于-97 拟集成电路方面的研究。 dBc/Hz,1MHz频偏处的带外相位噪声均小于- 124dBc/Hz。在1.8V的电源电压下,消耗的电流为 16mA。 C1994-201I China Academic Journal Electronic Publishing House.All rights reserved.http://www.cnki.net图 10 1. 516 GHz 信号的相位噪声测试结果 Fig . 10 Measured pha se no ise at 1. 516 GHz 图 11 1. 5 GHz 信号的功率谱密度测试 Fig. 11 Measur ed power spectr um density at 1. 5 GHz 5 结 论 利用线性模型分析推导了小数频率综合器中量 化噪声对相位噪声的作用, 提出了量化噪声抑制技 术, 应用这种技术实现了一款应用于小数频率综合 器中的小数分频器。应用一种非常简单的编程方式 实现了 调制器和分频器的配合。分频器采用同步 技术来消除异步特性引起的累积噪声。包含该分频 器的整个频综在SM IC 0. 18 m RF 工艺下流片。测 得的 10 kHz 频偏处的带内相位噪声均小于- 97 dBc/ Hz, 1 M Hz 频偏处的带外相位噪声均小于- 124 dBc/ Hz。在1. 8 V 的电源电压下, 消耗的电流为 16 mA。 参 考 文 献 [ 1] 刘深渊, 杨清渊. 锁相环路[ M] . 台湾: 沧海书局, 2006: 154-158. [ 2] Yang Yuche, Yu Shih-An, Tang Tao , et al. A quantiza tion no ise suppr ession technique for fra ct ional-N fr equency synthesizers [ J] . IEEE J So lid-state Circuits, 2006, 41( 11) : 2500-2511. [ 3] Ga lto n I. Delta-Sigma fr actio nal-N pha se locked loo ps [ C] . B. Razav i. Phase-Locking in High Perfo rmance Systems: Fr om Devices t o Ar chitectures, Piscataw ay , New Yo rk: Wiley IEEE Press, 2003: 23-33. [ 4] 卢磊, 闵昊, 唐长文. 一种应用于分数分频频率合成器 的脉冲吞计数器[ P] . 申请号: 200910050627. 7. [ 5] Lu Lei, Gong Zhichao , Lia o Youchun, et al. A 975-to- 1960 MHz fast-locking fra ct ional-N synthesizer w ith adapt ive bandw idth contr ol a nd 4/ 4. 5 prescalar for digital TV tuners[ C ] . ISSCC Dig Tech Papers, 2009: 396-398. [ 6] Jo hn Rog ers, Calvin Plett, Fo ster Dai. I nteg r ated Circuit Desig n fo r High -Speed Frequency Synthesis[ M] . Art ech House, 2006: 153-155. [ 7] Lev ant ino S, Roman L, Peller ano S, et al. Phase noise in dig ita l frequency div iders[ J] . IEEE J Solidstate Cir cuits, 2004, 39( 5) : 775-784. [ 8] Rhee W, So ng B S, Ali A. A 1. 1-GHz CMOS fr actio na l-N fr equency sy nt hesizer w it h a 3-b thir d-or der modulato r[J] . IEEE J Solid-state Circuits, 2000, 35( 10) : 1453-1460. [ 9] Lu Lei, Chen Jingho ng, Yuan Lu, et a l. An 18-mW 1. 175-2-GHz frequency synthesizer with constant bandw idth for DVB-T tuners[J] . Tr ans o n M icrowa ve and T echniques, 2009, 57( 4) : 928-937. 黄兆 磊( Huang Zhaolei) 男, 山东 人, 1982 年生, 2005 年 6 月年毕业于厦门大 学物理系, 现为复旦大学ASIC 国家重点 实验室硕士研究生, 主要从事射频和模 拟集成电路方面的研究。 195 2 期 黄兆磊等: 具有量化噪声抑制的小数分频器���