正在加载图片...

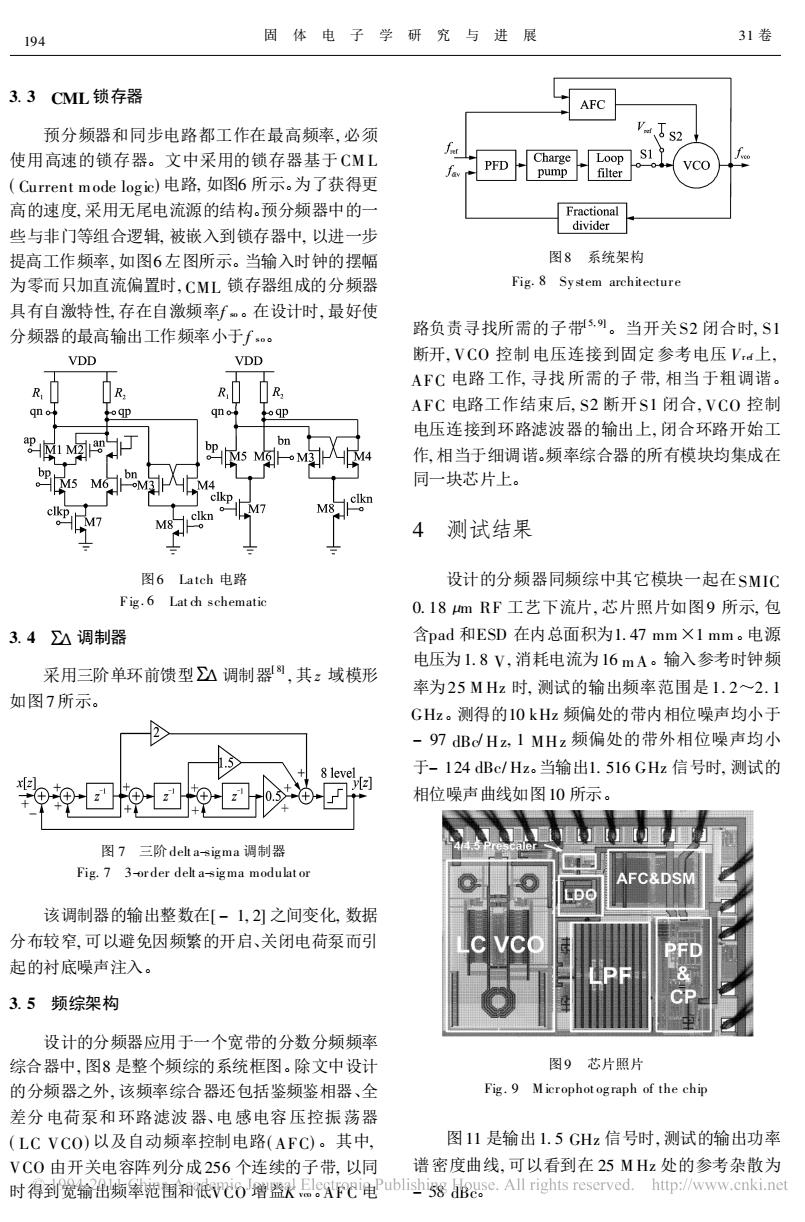

194 固体电子学研究与进展 31卷 3.3CML锁存器 AFC 预分频器和同步电路都工作在最高频率,必须 使用高速的锁存器。文中采用的锁存器基于CML s19 PFD Charge Loop filter VCO pump (Current mode logic))电路,如图6所示。为了获得更 高的速度,采用无尾电流源的结构。预分频器中的一 Fractional 些与非门等组合逻辑,被嵌入到锁存器中,以进一步 divider 提高工作频率,如图6左图所示。当输入时钟的摆幅 图8系统架构 为零而只加直流偏置时,CML锁存器组成的分频器 Fig.8 System architecture 具有自激特性,存在自激频率fm。在设计时,最好使 分频器的最高输出工作频率小于f。 路负贵寻找所需的子带5。当开关S2闭合时,S1 VDD VDD 断开,VCO控制电压连接到固定参考电压Vd上, AFC电路工作,寻找所需的子带,相当于粗调谐。 R R. AFC电路工作结束后,S2断开S1闭合,VCO控制 电压连接到环路滤波器的输出上,闭合环路开始工 bn 作,相当于细调谐.频率综合器的所有模块均集成在 95M6 -oM3 M4 同一块芯片上。 clkp clkp 4 测试结果 图6 Latch电路 设计的分频器同频综中其它模块一起在SMIC Fig.6 Lat ch schematic 0.18mRF工艺下流片,芯片照片如图9所示,包 3.44调制器 含pad和ESD在内总面积为l.47mm×1mm。电源 电压为1.8V,消耗电流为16mA。输入参考时钟频 采用三阶单环前馈型∑△调制器,其:域模形 率为25MHz时,测试的输出频率范围是1.2~2.1 如图7所示。 GHz。测得的10kHz频偏处的带内相位噪声均小于 -97 dBc/Hz,1MHz频偏处的带外相位噪声均小 8 level 于-124dBc/Hz。当输出1.516GHz信号时,测试的 99回9回9回8 z 相位噪声曲线如图10所示。 图7三阶delt a-sigma调制器 Fig.7 3-order delt a-sigma modulat or 该调制器的输出整数在[-1,2]之间变化,数据 分布较窄,可以避免因频繁的开启、关闭电荷泵而引 起的衬底噪声注入。 3.5频综架构 设计的分频器应用于一个宽带的分数分频频率 综合器中,图8是整个频综的系统框图。除文中设计 图9芯片照片 的分频器之外,该频率综合器还包括鉴频鉴相器、全 Fig.9 Microphotograph of the chip 差分电荷泵和环路滤波器、电感电容压控振荡器 (LC VCO)以及自动频率控制电路(AFC)。其中, 图11是输出1.5GHz信号时,测试的输出功率 VC0由开关电容阵列分成256个连续的子带,以同 谱密度曲线,可以看到在25MHz处的参考杂散为 时得到宽输出频率范围和低VCO增益K,XF代电°ubli8Bse.All rights reserved,http://www.cnki.net3. 3 CML 锁存器 预分频器和同步电路都工作在最高频率, 必须 使用高速的锁存器。文中采用的锁存器基于CM L ( Current mode log ic) 电路, 如图6 所示。为了获得更 高的速度, 采用无尾电流源的结构。预分频器中的一 些与非门等组合逻辑, 被嵌入到锁存器中, 以进一步 提高工作频率, 如图6 左图所示。当输入时钟的摆幅 为零而只加直流偏置时, CML 锁存器组成的分频器 具有自激特性, 存在自激频率f so。在设计时, 最好使 分频器的最高输出工作频率小于f s o。 图6 La tch 电路 Fig . 6 Lat ch schematic 3. 4 调制器 采用三阶单环前馈型 调制器 [ 8] , 其z 域模形 如图7 所示。 图 7 三阶delt a-sigma 调制器 Fig. 7 3-or der delt a-sigma modulat or 该调制器的输出整数在[ - 1, 2] 之间变化, 数据 分布较窄, 可以避免因频繁的开启、关闭电荷泵而引 起的衬底噪声注入。 3. 5 频综架构 设计的分频器应用于一个宽带的分数分频频率 综合器中, 图8 是整个频综的系统框图。除文中设计 的分频器之外, 该频率综合器还包括鉴频鉴相器、全 差分电荷泵和环路滤波器、电感电容压控振荡器 ( LC VCO) 以及自动频率控制电路( AFC) 。其中, VCO 由开关电容阵列分成256 个连续的子带, 以同 时得到宽输出频率范围和低VCO 增益K vco。AFC 电 图8 系统架构 Fig. 8 Sy stem architectur e 路负责寻找所需的子带[ 5, 9]。当开关S2 闭合时, S1 断开, VCO 控制电压连接到固定参考电压 Vr ef上, AFC 电路工作, 寻找所需的子带, 相当于粗调谐。 AFC 电路工作结束后, S2 断开S1 闭合, VCO 控制 电压连接到环路滤波器的输出上, 闭合环路开始工 作, 相当于细调谐。频率综合器的所有模块均集成在 同一块芯片上。 4 测试结果 设计的分频器同频综中其它模块一起在SMIC 0. 18 m RF 工艺下流片, 芯片照片如图9 所示, 包 含pad 和ESD 在内总面积为1. 47 mm×1 mm。电源 电压为1. 8 V, 消耗电流为16 mA。输入参考时钟频 率为25 M Hz 时, 测试的输出频率范围是1. 2~2. 1 GHz。测得的10 kHz 频偏处的带内相位噪声均小于 - 97 dBc/ Hz, 1 MHz 频偏处的带外相位噪声均小 于- 124 dBc/ Hz。当输出1. 516 GHz 信号时, 测试的 相位噪声曲线如图10 所示。 图9 芯片照片 Fig . 9 Micr ophot og raph of the chip 图11 是输出1. 5 GHz 信号时, 测试的输出功率 谱密度曲线, 可以看到在 25 M Hz 处的参考杂散为 - 58 dBc。 194 固 体 电 子 学 研 究 与 进 展 31 卷��