正在加载图片...

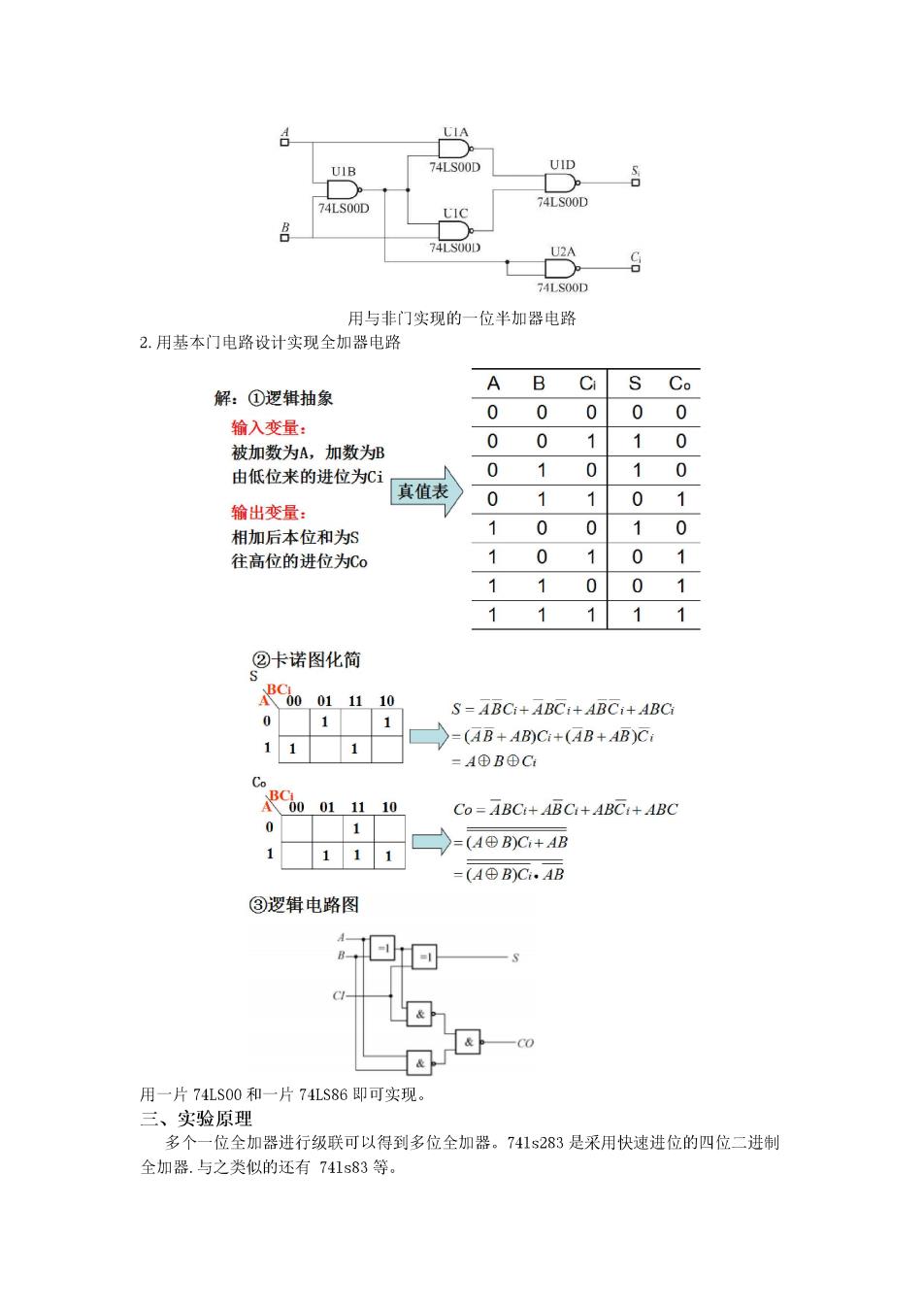

A 74LS00D 74LS00 74LSOOD 用与非门实现的一位半加器电路 2.用基本门电路设计实现全加器电路 解:①逻辑抽象 A B Ci S Co 000 00 输入变量: 被加数为A,加数为 00 1 10 由低位来的进位为Ci 01 0 10 真值表 01 101 输出变量: 相加后本位和於 0 0 10 往高位的进位为C: 0 1 01 1 1 0 01 1 1 1 11 ②卡诺图化简 60011110 S=ABC:+ABC:+ABC+ABC 01 111 -(AB+ABC+(AB+AB)C, =A④BC C001110 Co=ABCi+ABCi+ABCi+ABC 0 =4⊕B)C+AB 1111 (d⊕B)C.AB ③逻辑电路图 —c0 用一片74LS00和一片74LS86即可实现 三、实验原理 多个一位全加器进行级联可以得到多位全加器。7415283是采用快速进位的四位二进制 全加器.与之类似的还有741s83等