正在加载图片...

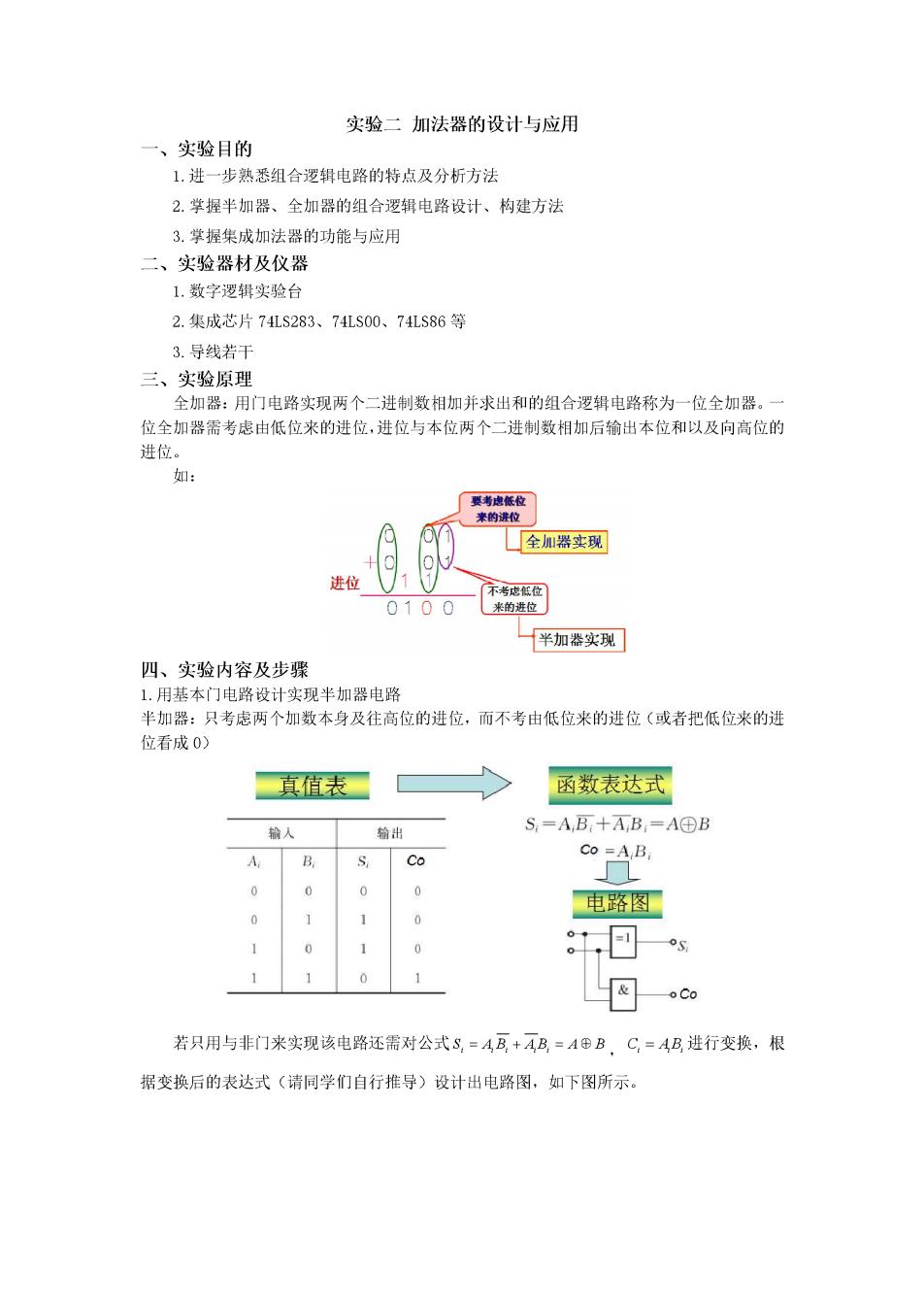

实验二加法器的设计与应用 一、实验目的 1,进一步熟悉组合逻辑电路的特点及分析方法 2.学握半加器、全加器的组合逻辑电路设计、构建方法 3.学握集成加法器的功能与应用 二、实验器材及仪器 1.数字逻辑实验台 2.集成芯片74LS283、74LS00、7LS86等 3.导线若干 三、实验原理 全加器:用门电路实现两个二进制数相加并求出和的组合逻辑电路称为一位全加器。 位全加器需考虑由低位来的进位,进位与本位两个二进制数相加后输出本位和以及向高位的 进位 如 要考虑低位 全器实现 进位 0100 不 半加春实现 四、实验内容及步骤 用基本门电路设计实现半加器电路 半加器:只考虑两个加数本身及往高位的进位,而不考由低位来的进位(或者把低位来的进 位看成0) 真值表 函数表达式 输人 输出 S,=AB,+A,B,=A©B 电路图 0 1可s 1 1 0 1 若只用与非门来实现该电路还需对公式S=4B+AB=A©B,C=AB进行变换,根 据变换后的表达式(请同学们自行推导)设计出电路图,如下图所示