电子与信息工程学院 讲稿 课程名称:《数字电子技术实验》 课程代码: 32080941 授课班级: 授课教师: 李积英 系 别:电工电子实验中心 授课时间:

目录 课程介绍 3 实验一基本门电路逻辑功能测试 4 实验二加法器的设计与应用 7 实验三译码器和数据选择器的设计及应用 11 实验四优先编码器的设计(EWB) 15 实验五触发器的设计及应用 17 实验六计数器的设计.. 21 实验七555

课程介绍 ·、教材与参老书目 敦材:电子技术实验, 王紫螃,中国铁道出版社,2009 参考书: 1.电子技术基础(数字部分),康华光 2.加ltisiml0电路仿真设计相关书籍 3.数字电路设计相关书第 课程内容-必做部分 名称 学时 类型 实验一组合逻线电路功能测试及设计 2 设计型(必做】 实验二加法器的设计与应用 设计型(必做) 实验三译码器和数据选择器的设计及应用 设计型(必做) 实验四触发器的设计及应用 设计型(必做 实险五计数器的设计及应用 设十行型(必拉 实验六555定时器 设计型(必做) 实验七综合实验 设计型(必做) 实验考试 2 设计型(必做) 课程内容-选作部分 名称 学时 类型 设计一D/A转换电路及其应用 设计型(选做) 设计二A/D转换电路及其应用 设计型(选做 设计三流水灯的设计 设计型(选做》 设计四交通灯的设计 设计型(选做】 设计五简易数字钟 设计型(选做 设计六综合设计(学生自主选题) 综合型(选做) 三、课程要求与考核 1.课前预习,课堂讲解和实际操作,课后完成报告 2.实验报告撰写要求: 预习 设计好电路图 ,要求完成实验报告的1 2、3、5部分 ,每节课用到的芯片引脚 图画在实验原理部分:设计的电路图写在实验电路部分;设计过程写在实验数据部分:实验 结束后完成报告的其余部分。 3.成绩考核按照:“考试成绩(50%)+平时成绩(25%)+报告成绩(25%)”给出,实行一票 否决制 四、注意事项 1.注意用电安全 2.实验过程中不可随意插拔实验台上的芯片。芯片损坏需要更换时,请向老师举手示意。 3.请同学们自觉维护实验室卫生。 五、课程性质与教学目标 .2 课程性质:本课程是电类各专业的主要技术基础课程之一 是电类各专业的主干课程, 教学目标 本课程的 学目标是在学生茅握数字逻辑电路与系统的基 体知识、基本分 方法的基础上,通过实践强化基本应用技能,使学生能够对各种基本逻辑单元进行分析和设 计,学会使用标准的集成电路和可编程逻辑器件,并初步具备根据实际要求应用这些单元和 器件构成简单数字电子系统的能力,为后续专业课程的学习奠定坚实的基础

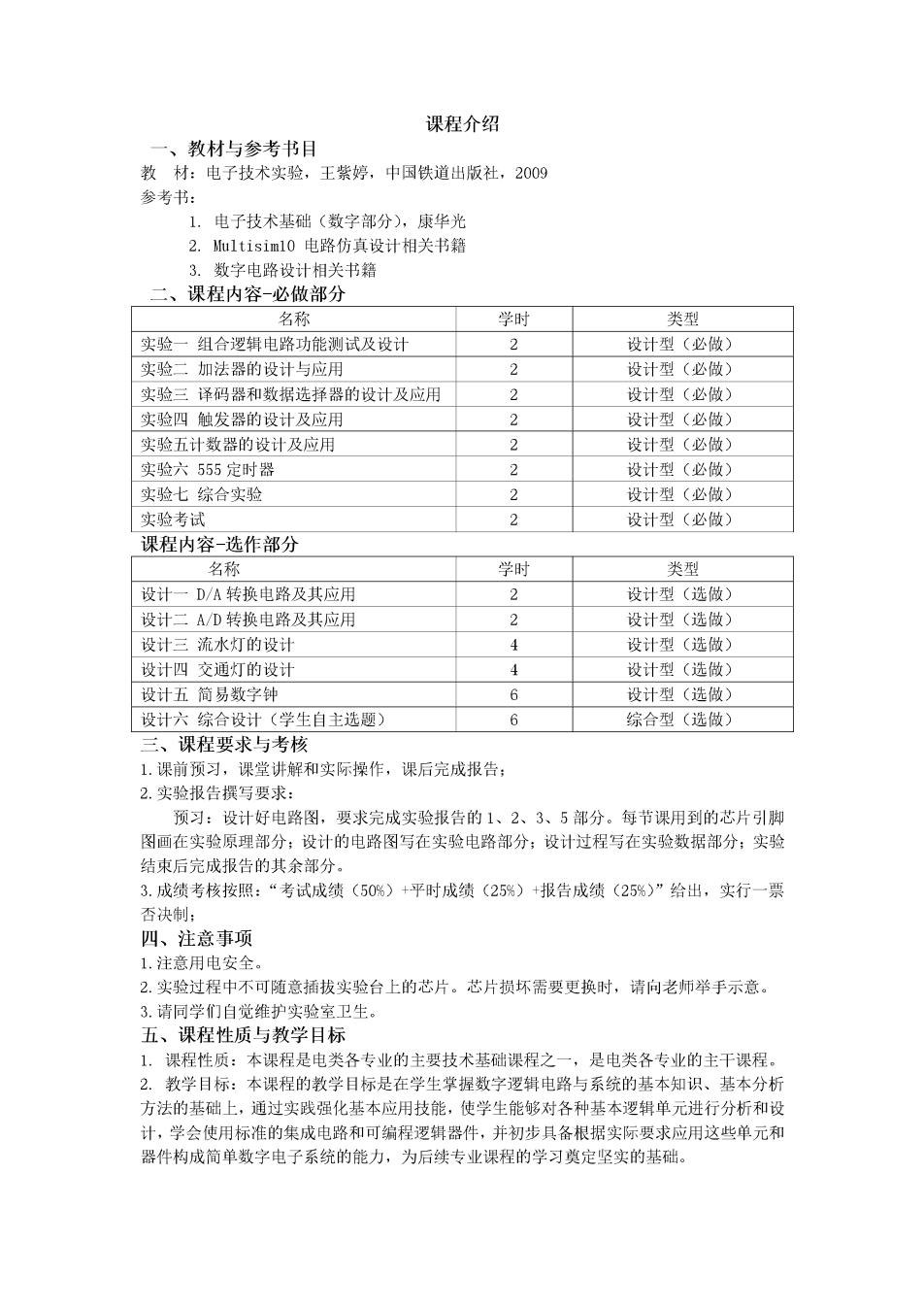

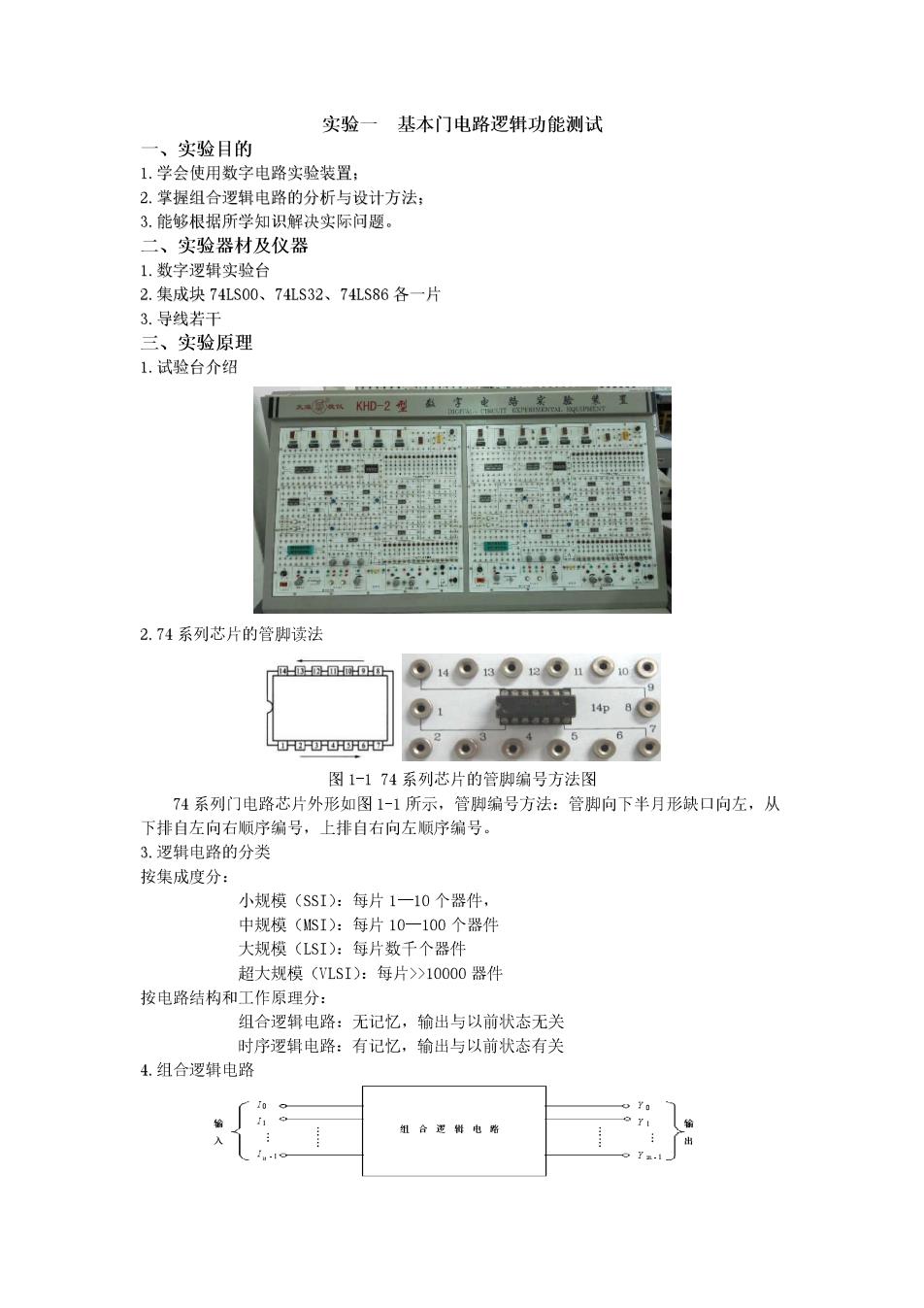

实验一基本门电路逻辑功能测试 一、实验目的 1,学会使用数字电路实验装置 2.掌握组合逻辑电路的分析与设计方法: 3.能够根据所学知识解决实际问题。 二、实验器材及仪器 L数字罗辑实验台 2.集成块74LS00、74S32、74LS86各一片 3.导线若干 三、实验原理 1.试验台介绍 2.74系列芯片的管脚读法 ©1 O-P-0-00-O-U 图1-174系列芯片的管脚编号方法图 74系列门电路芯片外形如图1-1所 管脚编号方法:管脚向下半月形缺口向左,从 下排自左向右顺序编号, 上排自右向左颗序编号 3.逻辑电路的分类 按集成度分: 小规模(SSI):每片1一10个器件, 中规模(SI):每片10一100个署件 大规模(LSI):每片数千个器件 超大规模(LSI):每片>10000器件 按电路结构和工作原理分: 组合逻辑电路:无记忆,输出与以前状态无关 时序罗辑电路:有记忆,偷出与以前状态有关 4.组合逻辑电路 创合电

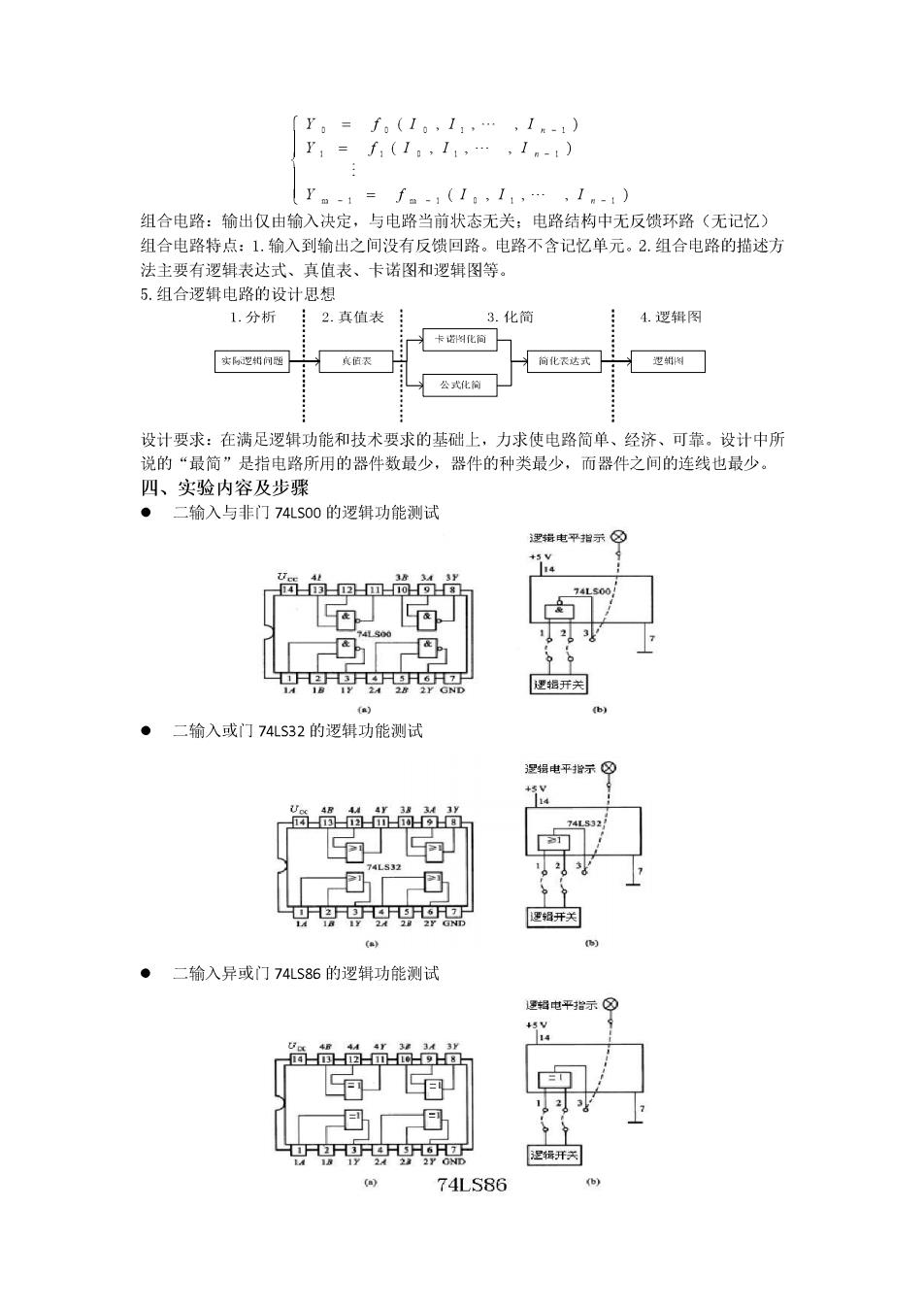

「r,=f。(1。,1,,…,1,1) =f:(11…1。-1) y。-1=f。(11 组合电路:输出仅由输入决定,与电路当前状态无关;电路结构中无反馈环路(无记忆) 组合电路特点:1.输入到输出之间没有反馈回路。电路不含记忆单元。2.组合电路的描述方 法主要有罗辑表达式、直值表、卡诺图和逻辑图等。 5组合罗辑由路的设思知 ,分析 2.真值表 3.化简 4.逻辑网 一卡化 间化不达式 地N☐ 设计要求:在满足逻辑功能和技术要求的基础 力求使电路简单、经济、可靠。设计中所 说的“最简 是指电路所用的器件数最少,器件的种类最少,而器件之间的连线也最少 四、实验内容及步骤 ·二输入与非门74LS00的逻辑功能测试 ● 二输入或门74LS32的逻辑功能测试 尚尚品总尚 53: 二输入异或门74LS86的逻辑功能测试 色的的总总益。 回 74LS86

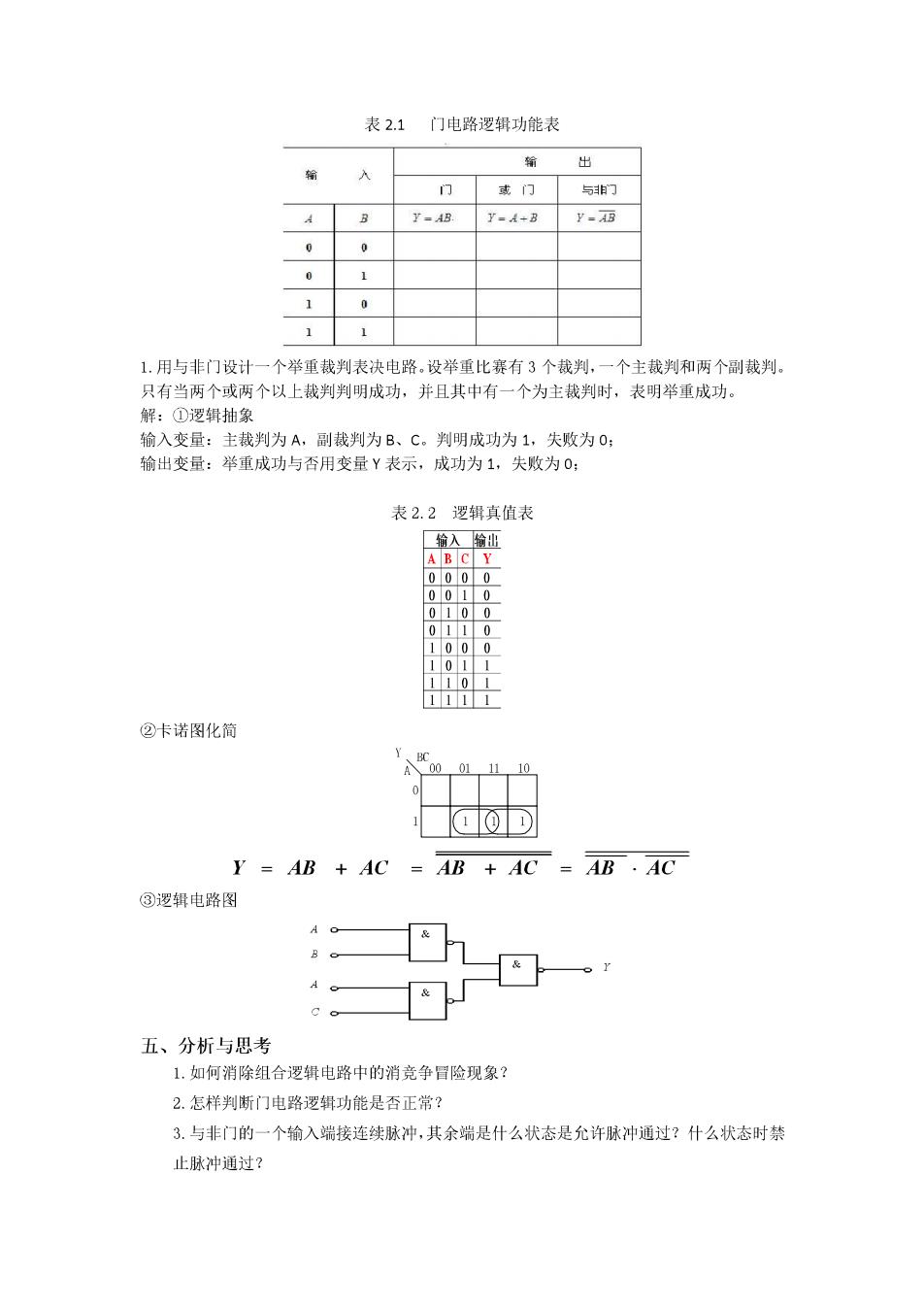

表2.1门电路逻辑功能表 出 入 减门 与门 Y-4-8 1 1.用与非门设计一个举重裁判表决电路。设举重比赛有3个裁判,一个主裁判和两个副裁判。 只有当两个或两个以上裁判判明成功,并且其中有一个为主裁判时,表明举重成功。 解:①逻锅抽象 输入变量:主判为A 副裁判为B、C。判明成功为1,失败为0; 输出变量:举重成功与否用变量Y表示,成功为1,失收为0: 表2.2逻辑真值表 0i00 ②卡诺图化简 CO O1 11 Y=AB+AC=AB+AC=AB·AC ③逻辑电路图 五、分析与思考 1.如何消除组合逻辑电路中的消竞争冒险现象 2.怎样判断门电路逻辑功能是否正常? 3.与非门的一个输入端接连续脉冲,其余端是什么状态是允许脉冲通过?什么状态时禁 止脉冲通过?

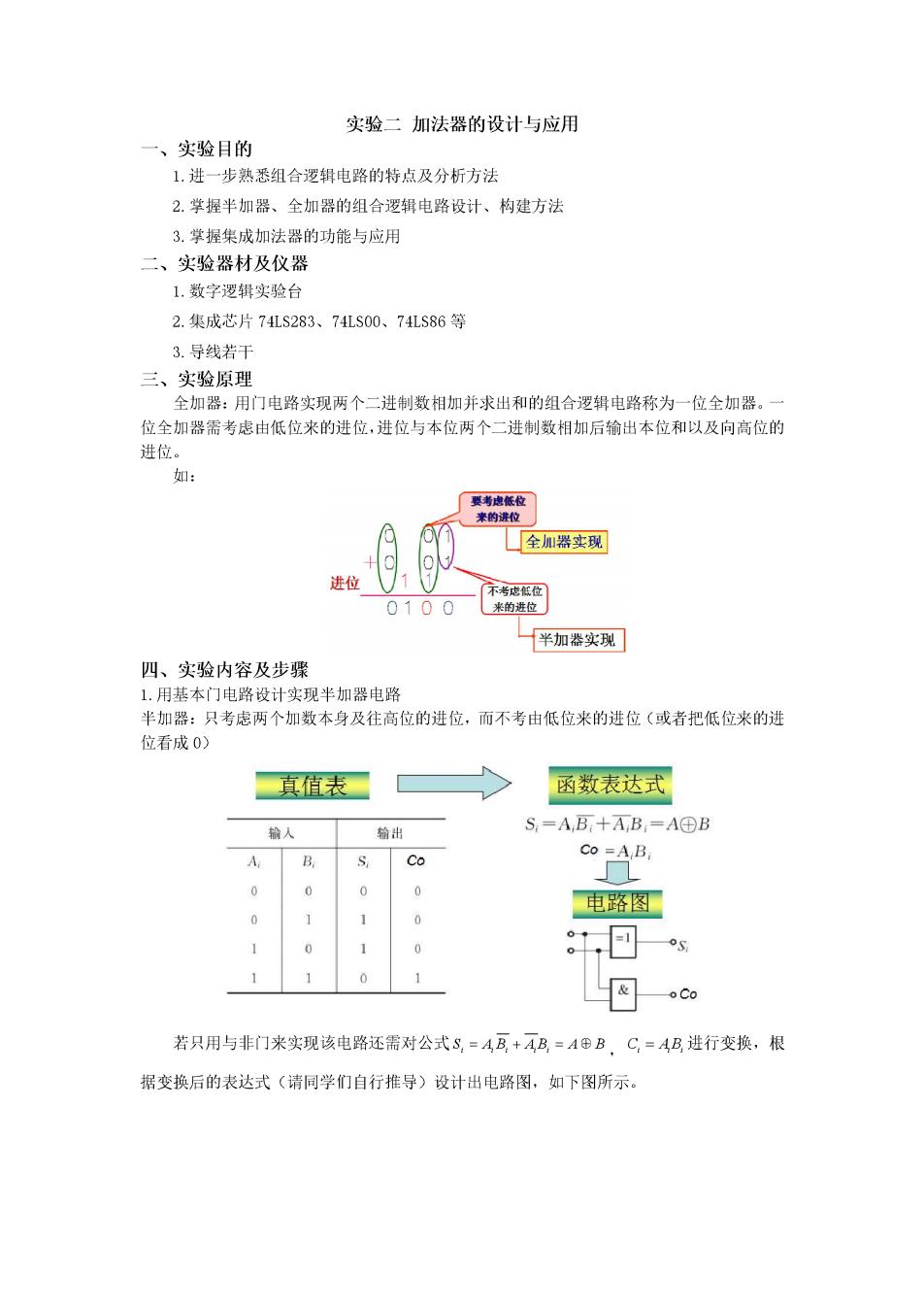

实验二加法器的设计与应用 一、实验目的 1,进一步熟悉组合逻辑电路的特点及分析方法 2.学握半加器、全加器的组合逻辑电路设计、构建方法 3.学握集成加法器的功能与应用 二、实验器材及仪器 1.数字逻辑实验台 2.集成芯片74LS283、74LS00、7LS86等 3.导线若干 三、实验原理 全加器:用门电路实现两个二进制数相加并求出和的组合逻辑电路称为一位全加器。 位全加器需考虑由低位来的进位,进位与本位两个二进制数相加后输出本位和以及向高位的 进位 如 要考虑低位 全器实现 进位 0100 不 半加春实现 四、实验内容及步骤 用基本门电路设计实现半加器电路 半加器:只考虑两个加数本身及往高位的进位,而不考由低位来的进位(或者把低位来的进 位看成0) 真值表 函数表达式 输人 输出 S,=AB,+A,B,=A©B 电路图 0 1可s 1 1 0 1 若只用与非门来实现该电路还需对公式S=4B+AB=A©B,C=AB进行变换,根 据变换后的表达式(请同学们自行推导)设计出电路图,如下图所示

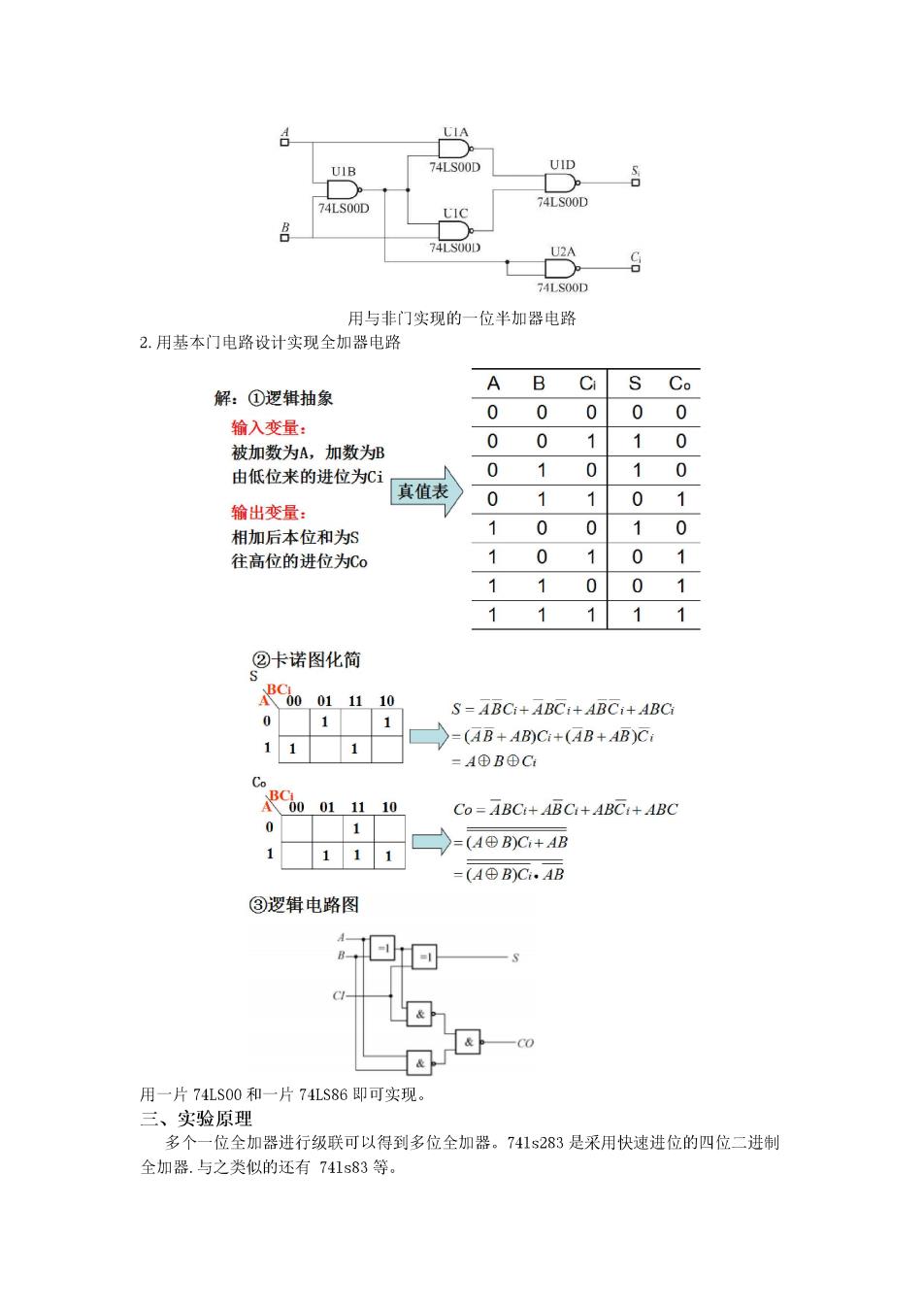

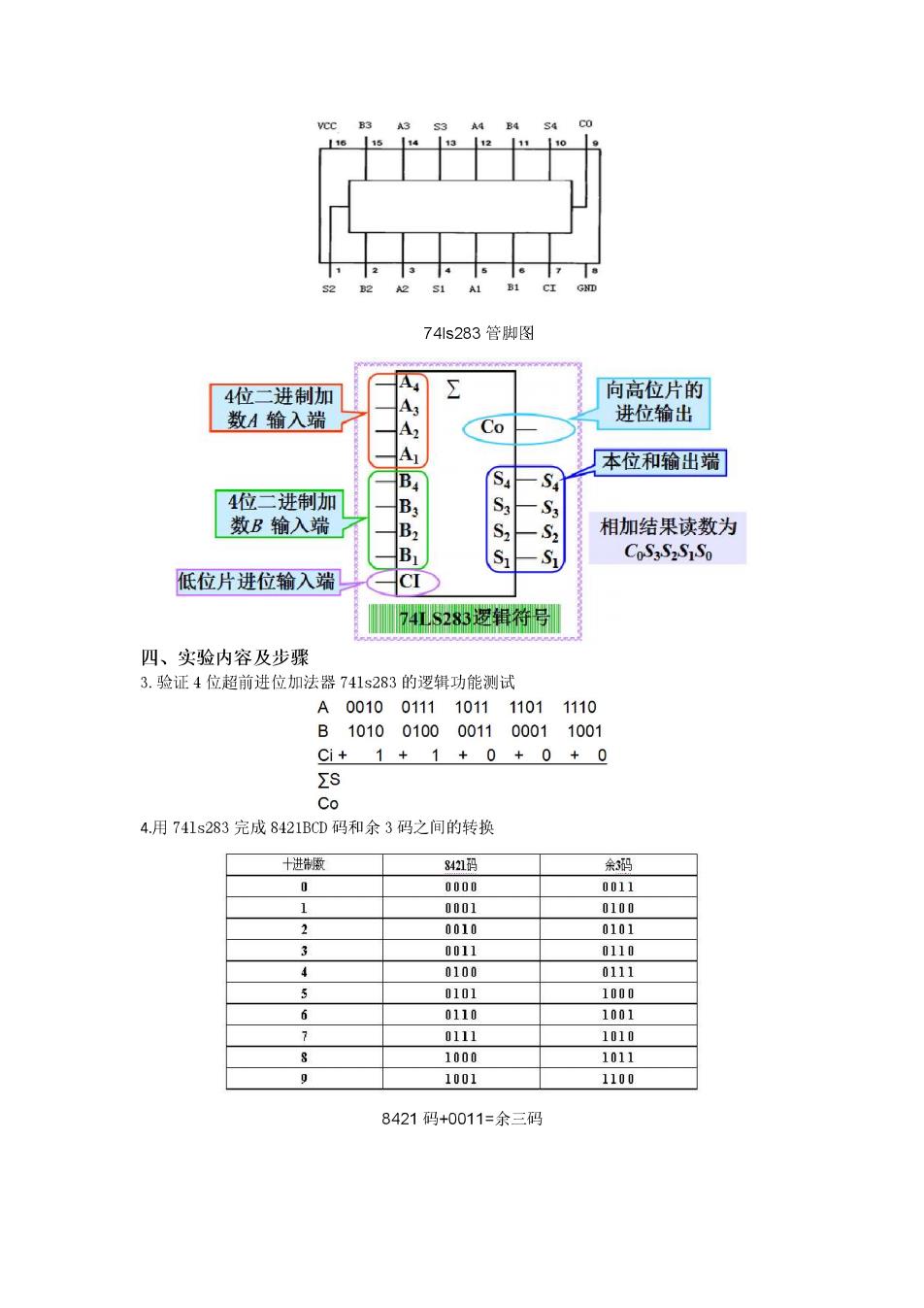

A 74LS00D 74LS00 74LSOOD 用与非门实现的一位半加器电路 2.用基本门电路设计实现全加器电路 解:①逻辑抽象 A B Ci S Co 000 00 输入变量: 被加数为A,加数为 00 1 10 由低位来的进位为Ci 01 0 10 真值表 01 101 输出变量: 相加后本位和於 0 0 10 往高位的进位为C: 0 1 01 1 1 0 01 1 1 1 11 ②卡诺图化简 60011110 S=ABC:+ABC:+ABC+ABC 01 111 -(AB+ABC+(AB+AB)C, =A④BC C001110 Co=ABCi+ABCi+ABCi+ABC 0 =4⊕B)C+AB 1111 (d⊕B)C.AB ③逻辑电路图 —c0 用一片74LS00和一片74LS86即可实现 三、实验原理 多个一位全加器进行级联可以得到多位全加器。7415283是采用快速进位的四位二进制 全加器.与之类似的还有741s83等

。。 251 741s283管脚图 4位二进制加 向高位片的 数A输入端· Co 进位输出 本位和输出端 S. 4位二进制加 数B输入端 9 B 相加结果读数为 B 5 低位片进位输入端 7415283逻辑符号 四、实验内容及步骤 3.验证4位超前进位加法器741s283的逻辑功能测试 0010 0111 10111101 1110 B 10100100001100011001 Ci+1+1+0+0+0 SS Co 4.用741s283完成8421BCD码和余3码之间的转换 十进 3421码 000 0011 001 001 0110 1001 0111 1010 1000 1011 1001 1100 8421码+0011=余三码

13 Y2 Y1 Yo 余3码 S3 S2 S1 So co 74LS283C A3 A2 A:Ao B3 B2 B Bo 8421BCD码 0011 由74LS283构成的代码转换电路 5.用四位超前进位加法器741s283设计一个加/减运算电路,当M0时,实现加法:当W=1时 实现减法。 对于A-B,可以表示为补码运算式:A+()=A+B+1,B的反码可以用异或门来实现。 这样“A”可以直接输入到一组四位二进制的数,“1”可以直接由最低位进位C!端输入高电 平“1”,从而实现了把减法变成加法。 N厦=(2"-1)-N原 N补-2”-N原;N补-N友1 A-B=A+B-2"=A+BE+1-2” Sa S3 S:So 74LS283 NDA:A:Ao B3 B3 B:Bo 五、分析与思考 1.74S283如何实现级联? 2.如何将余3码转换成BCD码? 3.将实验内容4中的条件改为“当1时,实现加法:当M0时,实现减法”时应该如 何设计电路?