数字电子技术实验课程教学课件 @ 葡州克通大警 实验三译码器和数据选择器的设计及 应用 国家级电工电子实验教学示范中心

实验三 译码器和数据选择器的设计及 应用 数字电子技术实验课程教学课件 国家级电工电子实验教学示范中心

纲要 葡州克通大率 一、实验目的 二、实验器材及仪器 三、实验原理 四、应用举例 五、实验内容及步骤 六、分析与思考

纲要 一、实验目的 二、实验器材及仪器 三、实验原理 五、实验内容及步骤 六、分析与思考 四、应用举例

一、 实验目的 菌州发通大警 1.掌握译码器的工作原理和逻辑功能; 2.掌握数据选择器的逻辑功能及特点; 3.熟悉译码器的应用; 4.掌握用数据选择器实现组合逻辑函数的方法

一、实验目的 1.掌握译码器的工作原理和逻辑功能; 2.掌握数据选择器的逻辑功能及特点; 3.熟悉译码器的应用; 4.掌握用数据选择器实现组合逻辑函数的方法

二、实验器材及仪器 前州充通大粤 1.数字逻辑实验台; 2.集成块74LS151、74LS138、74LS20、74LS00: 3.导线若干

二、实验器材及仪器 1.数字逻辑实验台; 2.集成块74LS151、74LS138、74LS20、74LS00; 3.导线若干

三、实验原理 菌州克通大努 1.译码器的工作原理 译码就是将二进制代码翻译成原来信号的 过程,是编码的逆过程,能完成这一任务 的电路称为译码器。 0 译码器可分为二进制译码器、BCD译码器 和数码显示译码器三种。 应用:1在计算机系统中用作地址译码器; 2.用译码器实现数据分配

三、实验原理 • 译码就是将二进制代码翻译成原来信号的 过程,是编码的逆过程,能完成这一任务 的电路称为译码器。 • 译码器可分为二进制译码器、BCD译码器 和数码显示译码器三种。 • 应用:1.在计算机系统中用作地址译码器; 2.用译码器实现数据分配。 1.译码器的工作原理

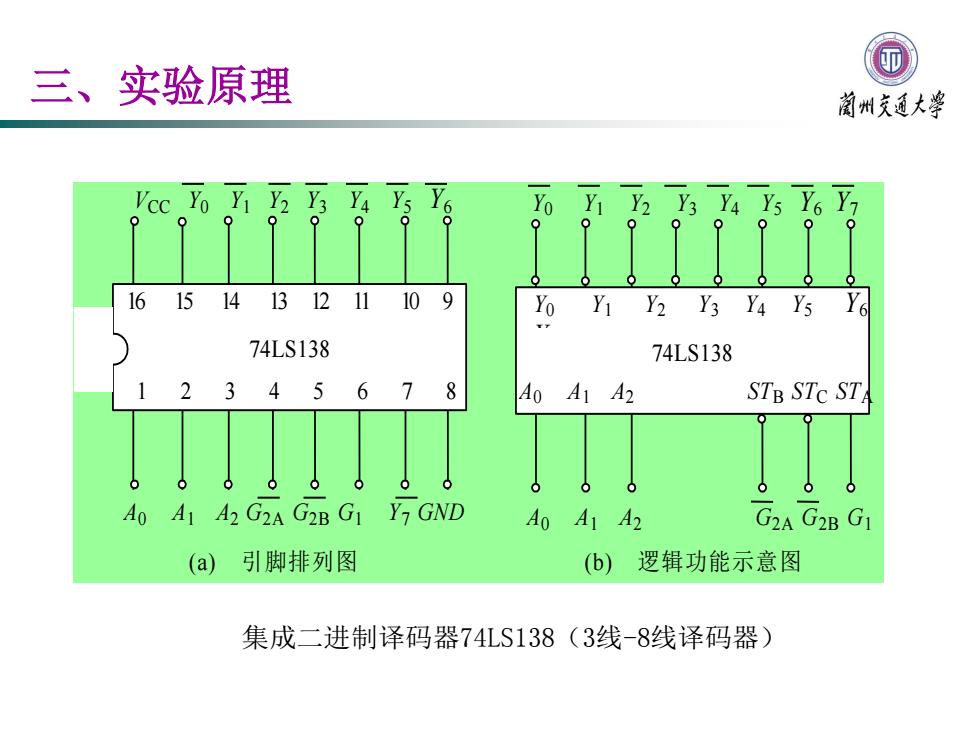

三、实验原理 菌州克通大警 Vcc Yo Y1 Y2 Y3 Y4 Y5 Yo Y1 Y2 Y3 Y4 Y5 Y6 Y7 ● 161514131211109 Yo Y1 Y2 Y3 Y4 Y5 Yo 74LS138 74LS138 1 234 567 Ao A1 A2 STB STC STA A )A1 A2 G2A G2B G1 Y7 GND A0 A1 A2 G2A G2B G1 (a)引脚排列图 (b)逻辑功能示意图 集成二进制译码器74LS138(3线-8线译码器)

三、实验原理 16 15 14 13 12 11 10 9 74LS138 1 2 3 4 5 6 7 8 VCC Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 G2 A G2 B G1 Y7 GND 74LS138 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 A0 A1 A2 G2 A G2 B G1 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 A0 A1 A2 S TB S TC S TA (a) 引脚排列图 (b) 逻辑功能示意图 集成二进制译码器74LS138(3线-8线译码器)

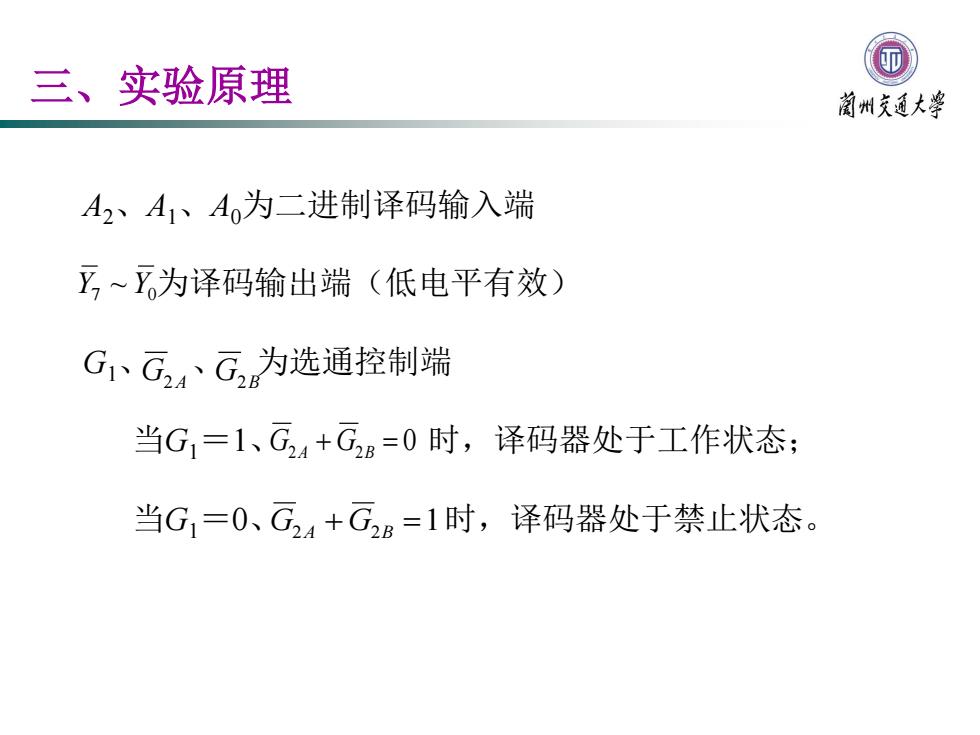

三、实验原理 菌州克通大努 A2、A1、A为二进制译码输入端 亚,~为译码输出端(低电平有效) G1G,4G为选通控制端 当G1=1、G,4+G,B=0时,译码器处于工作状态; 当G1=0、G24+G2B=1时,译码器处于禁止状态

三、实验原理 A2、A1、A0为二进制译码输入端 为译码输出端(低电平有效) G1、 、 为选通控制端 当G1 =1、 时,译码器处于工作状态; 当G1 =0、 时,译码器处于禁止状态。 Y7 ~ Y0 G2A G2B 0 G2A G2B G2A G2B 1

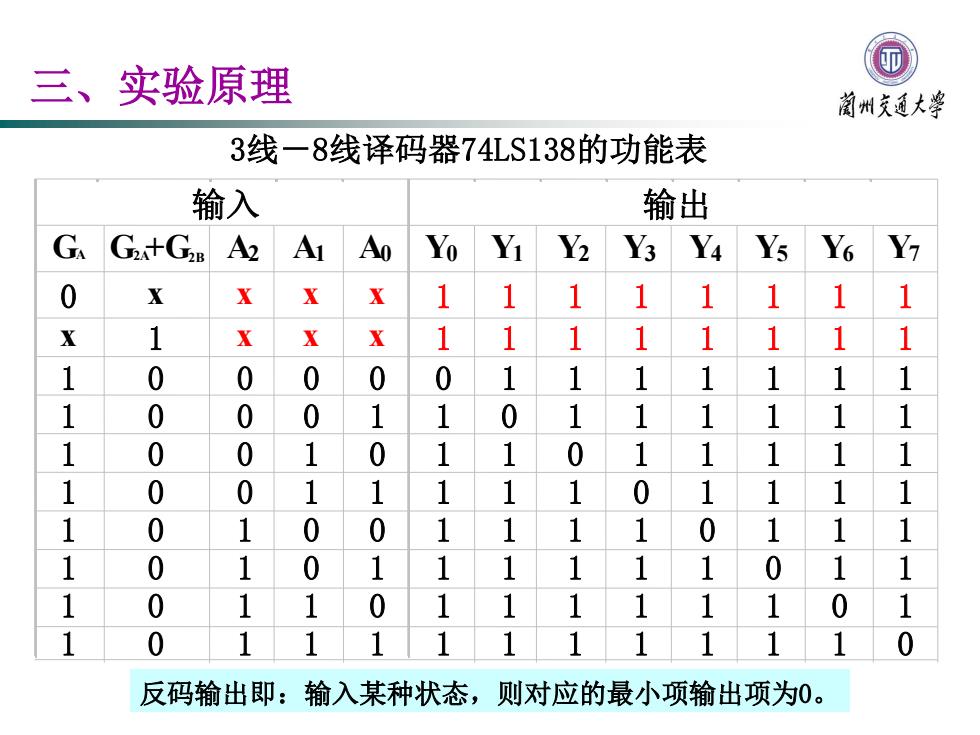

三、实验原理 蔺州克通大 3线一8线译码器74LS138的功能表 输入 输出 G G2+G2E A2 A Yo Y2 Y3 Y4 Y5 Y6 Y7 0 X 1 0 0 1 0 0 1 0 0 1 0 1 0 1 1 1 0 1 0 0 0 1 0 1 1 0 反码输出即:输入某种状态,则对应的最小项输出项为0

三、实验原理 3线-8线译码器74LS138的功能表 反码输出即:输入某种状态,则对应的最小项输出项为0。 GA G2A+G2B A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 0 x x x x 1 1 1 1 1 1 1 1 x 1 x x x 1 1 1 1 1 1 1 1 1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 0 输入 输出

三、实验原理 菌州克通大努 2.数据选择器的工作原理 数据选择器又称多路选择器,它能从多 个输入数据中选择一个数据输出,数据 选择器有四选一、八选一、十六选一等 多种类型。 应用:1.实现组合逻辑电路;2.与数据 分配器结合实现时分多路数据通信:3 实现数据并/串转换

三、实验原理 2.数据选择器的工作原理 • 数据选择器又称多路选择器,它能从多 个输入数据中选择一个数据输出,数据 选择器有四选一、八选一、十六选一等 多种类型。 • 应用:1.实现组合逻辑电路;2.与数据 分配器结合实现时分多路数据通信;3. 实现数据并/串转换

三、实验原理 菌州克通大粤 筒扇高扁尚品高高 Y A2 74LS151 74LS151 A Ao Do DI D2 D3 D4 Ds D6 D7 Lu234568 Z E GND 74LS151管脚图 74LS151逻辑符号 三个地址输入端A2、A1、A0, 八个数据输入端Do~D7, 两个互补输出的数据输出端Y和Y, 一个控制输入端

三、实验原理 74LS151 74LS151管脚图 74LS151逻辑符号 三个地址输入端A2、A1、A0, 八个数据输入端D0~D7, 两个互补输出的数据输出端Y和Y, 一个控制输入端S