EDA方法(设计)及实验 国家级电工电子实验教学示范中心

EDA方法(设计)及实验 国家级电工电子实验教学示范中心

第2章 FPGA/CPLD结构与应用 ⑩ 菌州克通大粤

第2章 FPGA/CPLD结构与应用

2.1 FPGA/CPLD的定义 FPGA-Field Programmable Gate Array CPLD-Complex Programmable Logic Device 菌州克通大粤

FPGA - Field Programmable Gate Array CPLD - Complex Programmable Logic Device 2.1 FPGA/CPLD的定义

2.2可编程逻辑器件的分类 1:按集成密度分:低密度(700门/片) 可编程逻辑器件(PLD) 简单PLD 复杂PLD PROM PLA PAL GAL CPLD FPGA ⑩ 菌州支通大学

2.2 可编程逻辑器件的分类 可编程逻辑器件(PLD) 简单 PLD 复杂 PLD PROM PLA PAL GAL CPLD FPGA 1:按集成密度分:低密度 (700门/片)

可编程逻辑器件的分类 2:按可编程逻辑器件的编程方式分: 一次性编程OTP器件 多次编程MTP器件 EPROM、E2PROM、 快闪存储器件的 优点是系统断电后编程信息不丢失,其中 EEPROM、快闪存储器件可编程100次, 只读存储器还设有保密位可以防止非法炮制 菌州克通大学

可编程逻辑器件的分类 2:按可编程逻辑器件的编程方式分: 一次性编程OTP器件 多次编程MTP器件 EPROM 、 、 快闪存储器件的 优点是系统断电后编程信息不丢失 ,其中 EEPROM、快闪存储器件可编程100次, 只读存储器还设有保密位可以防止非法炮制 E PROM 2

可编程逻辑器件的分类 3:按结构分:阵列型和门阵列型 阵列型PLD的基本结构由与阵列和或阵列组成。 简单PLD、EPLD、CPLD均属此类。(其中EPLD、 CPLD是从PAL、GAL发展起来的阵列型高密度PLD 器件,多数粟OM 和快闪存储器等编程技术 ,具有高密、高速、低耗等特点 现场可编程门阵列的结构由许多可编程单元(或 逻辑功能块)排成阵列组成。FPGA属此类。它类 似于掩膜可编程门阵列(MPGA),用户可通过编程将 这些模块连接起来实现不同的设计,它兼容了( MPGA),PLD的优点具有集成度高、更强的逻辑实现 能力、更好的设计灵活性。 菌州克通大粤

可编程逻辑器件的分类 3:按结构分:阵列型和门阵列型 阵列型PLD的基本结构由与阵列 和或阵列组成。 简单PLD、EPLD、CPLD均属此类。(其中EPLD、 CPLD是 从PAL、GAL发展起来的阵列型高密度PLD 器件,多数采用 和快闪存储器等编程技术 ,具有高密、高速、低耗等特点 现场可编程门阵列的结构由许多可编程单元(或 逻辑功能块 ) 排成阵列组成 。FPGA属此类 。它类 似于掩膜可编程门阵列(MPGA),用户可通过编程将 这些模块连接起来实现不同的设计,它兼容了( MPGA), PLD的优点具有集成度高、更强的逻辑实现 能力、更好的设计灵活性。 E PROM 2

2.3在系统可编程(ISP)技术 指对器件、电路板、整个电子系统的逻辑功能可随时进 行修改或重构的能力。是一种先进的编程方式。不需要 编程器,只需要通过计算机接口和编程电缆直接在对目 标系统编程。 支持SP技术的可编程逻辑器件成为在系统可编程器件 。采用ISP技术,使系统内硬件的功能就可以向软件一 样,通过编程很方便的被配置、重构、和升级。 多芯片SP编程方式,成为菊花链结构,各片共用一套 ISP编程接口,每片的SD输入端与前一片的SDO输出 端相连,最前面一片的SD端和最后一片的SDO端与 1SP编程口相连,构成链型结构。它只许5根线0 菌州克通大学

2.3 在系统可编程(ISP)技术 • 指对器件、电路板、整个电子系统的逻辑功能可随时进 行修改或重构的能力。是一种先进的编程方式。不需要 编程器,只需要通过计算机接口和编程电缆直接在对目 标系统编程。 • 支持ISP技术的可编程逻辑器件成为在系统可编程器件 。采用ISP技术,使系统内硬件的功能就可以向软件一 样,通过编程很方便的被配置、重构、和升级。 • 多芯片ISP编程方式,成为菊花链结构,各片共用一套 ISP编程接口,每片的SDI输入端与前一片的SDO输出 端相连,最前面一片的SDI端和最后一片的SDO端 与 ISP编程口相连,构成链型结构。它只许5根线()

2.4边界扫描技术JTAG (国际测试组织IEEE标准 ) 边界扫描测试是针对期间密度及/O接口数量 的增加,信号注入和测取难度越来越大而提出 的一种新的测试技术,他必须它不需要使用外 部物理测试探针来获得功能数据,JTAG技术 在器件正常工作时,器件的边界扫描单元能够 追踪引脚信号或是从器件逻辑信号中捕捉数据 ,在串行移出,与预期结果比较。通过JTAG测 试端口实现对SP器件的在系统编程,很容易 完成电路测试。它只需4根线(TDI测试数据入 、TDO出、TMS测试模式选择、TCK测试时钟 输入) 菌州克通大粤

2.4 边界扫描技术JTAG (国际测试组织IEEE标准) • 边界扫描测试是针对期间密度及I/O 接口数量 的增加,信号注入和测取难度越来越大而提出 的一种新的测试技术,他必须它不需要使用外 部物理测试探针来获得功能数据, JTAG技术 在器件正常工作时,器件的边界扫描单元能够 追踪引脚信号或是从器件逻辑信号中捕捉数据 ,在串行移出,与预期结果比较。通过JTAG测 试端口实现对ISP器件的在系统编程,很容易 完成电路测试。它只需4根线(TDI测试数据入 、TDO出、TMS测试模式选择、TCK测试时钟 输入)

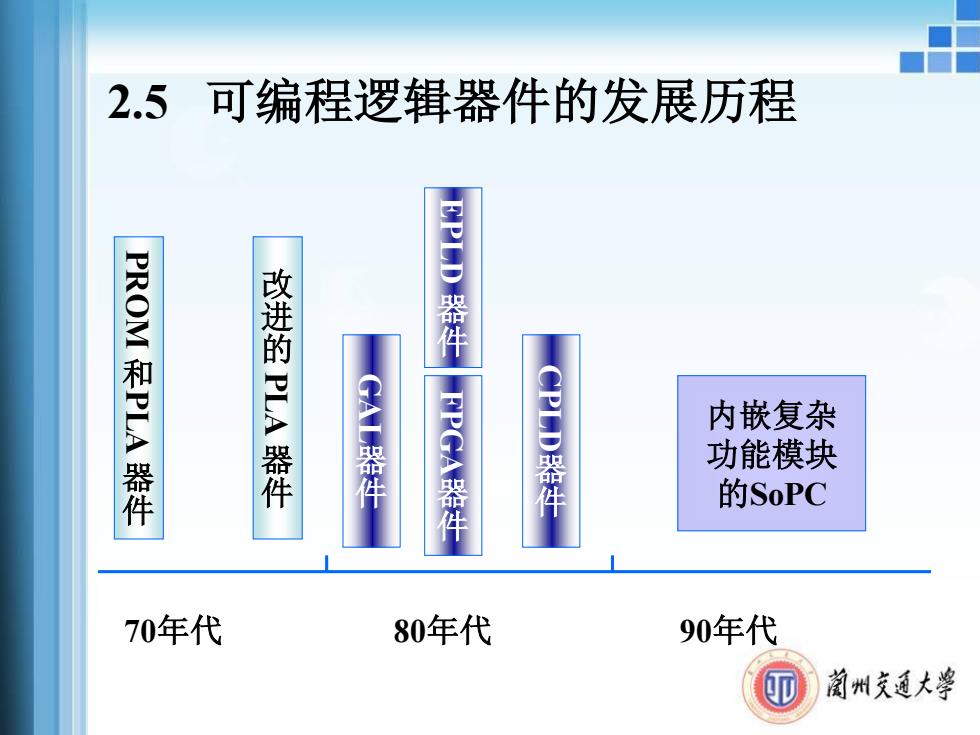

2.5可编程逻辑器件的发展历程 RPLD器 PROM村PL/器件 改进的/器件 器件 CPLD器件 内嵌复杂 功能模块 的SoPC 70年代 80年代 90年代 南葡州发通大粤

2.5 可编程逻辑器件的发展历程 70年代 80年代 90年代 PROM 和PLA 器 件 改 进 的PLA 器 件 GAL 器 件 FPGA 器 件EPLD 器 件 CPLD 器 件 内嵌复杂 功能模块 的SoPC

2.6EDA技术实现目标 1.超大规模可编程逻辑器件 2.半定制或全定制ASIC 3.混合ASIC ⑩ 菌州克通大婆

1. 超大规模可编程逻辑器件 2. 半定制或全定制ASIC 3. 混合ASIC 2.6 EDA技术实现目标 1. 超大规模可编程逻辑器件 2. 半定制或全定制ASIC 3. 混合ASIC