正在加载图片...

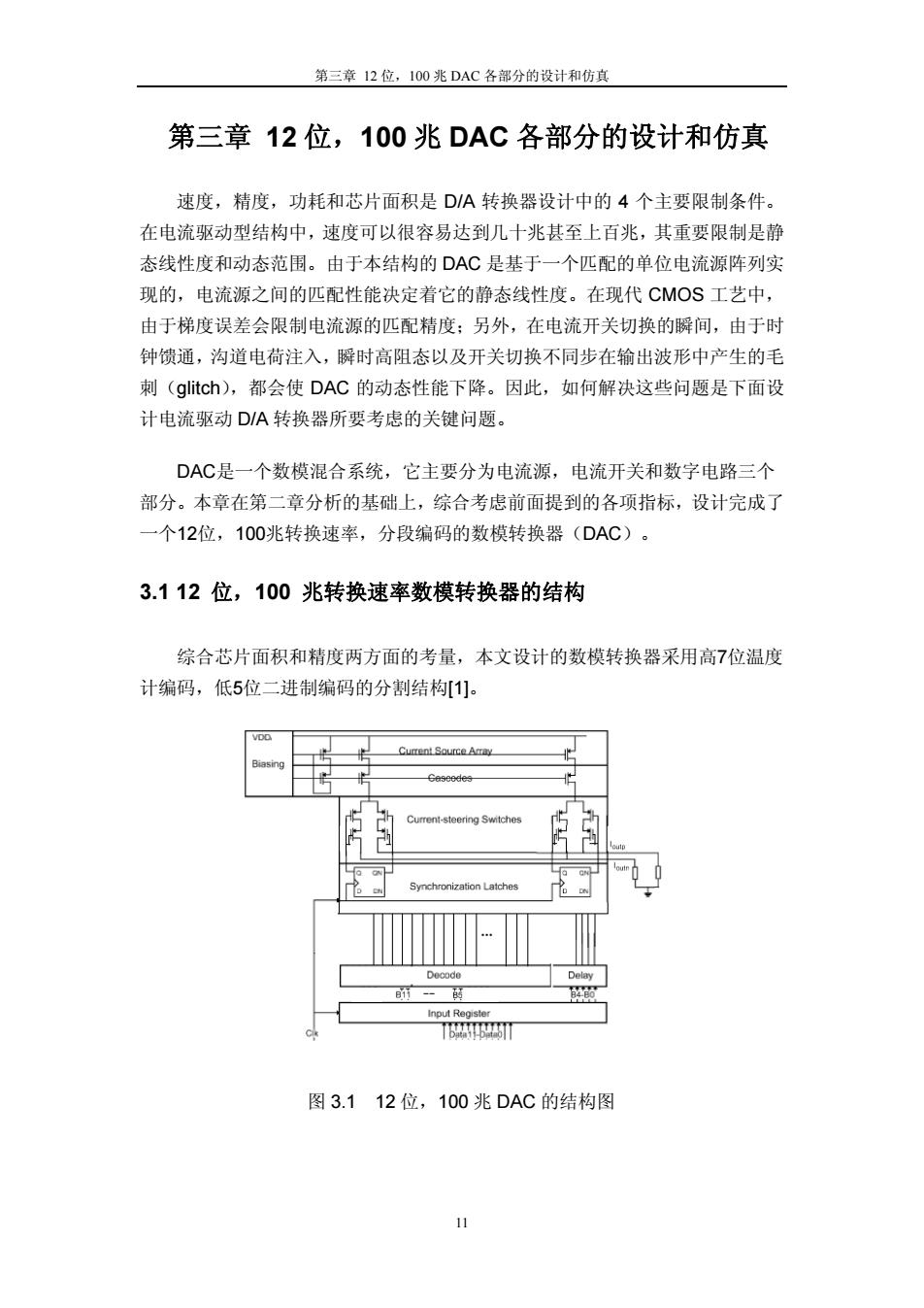

第三章12位,1O0兆DAC各部分的设计和仿真 第三章12位,100兆DAC各部分的设计和仿真 速度,精度,功耗和芯片面积是DA转换器设计中的4个主要限制条件。 在电流驱动型结构中,速度可以很容易达到几十兆甚至上百兆,其重要限制是静 态线性度和动态范围。由于本结构的DAC是基于一个匹配的单位电流源阵列实 现的,电流源之间的匹配性能决定着它的静态线性度。在现代CMOS工艺中, 由于梯度误差会限制电流源的匹配精度:另外,在电流开关切换的瞬间,由于时 钟馈通,沟道电荷注入,瞬时高阻态以及开关切换不同步在输出波形中产生的毛 刺(glitch),都会使DAC的动态性能下降。因此,如何解决这些问题是下面设 计电流驱动D/A转换器所要考虑的关键问题。 DAC是一个数模混合系统,它主要分为电流源,电流开关和数字电路三个 部分。本章在第二章分析的基础上,综合考虑前面提到的各项指标,设计完成了 一个12位,100兆转换速率,分段编码的数模转换器(DAC)。 3.112位,100兆转换速率数模转换器的结构 综合芯片面积和精度两方面的考量,本文设计的数模转换器采用高7位温度 计编码,低5位二进制编码的分割结构1]。 VDD Biasing Current-steering Switches Synchronization Latches Decode Input Register 1B41B811 图3.112位,100兆DAC的结构图 11第三章 12 位,100 兆 DAC 各部分的设计和仿真 11 第三章 12 位,100 兆 DAC 各部分的设计和仿真 速度,精度,功耗和芯片面积是 D/A 转换器设计中的 4 个主要限制条件。 在电流驱动型结构中,速度可以很容易达到几十兆甚至上百兆,其重要限制是静 态线性度和动态范围。由于本结构的 DAC 是基于一个匹配的单位电流源阵列实 现的,电流源之间的匹配性能决定着它的静态线性度。在现代 CMOS 工艺中, 由于梯度误差会限制电流源的匹配精度;另外,在电流开关切换的瞬间,由于时 钟馈通,沟道电荷注入,瞬时高阻态以及开关切换不同步在输出波形中产生的毛 刺(glitch),都会使 DAC 的动态性能下降。因此,如何解决这些问题是下面设 计电流驱动 D/A 转换器所要考虑的关键问题。 DAC是一个数模混合系统,它主要分为电流源,电流开关和数字电路三个 部分。本章在第二章分析的基础上,综合考虑前面提到的各项指标,设计完成了 一个12位,100兆转换速率,分段编码的数模转换器(DAC)。 3.1 12 位,100 兆转换速率数模转换器的结构 综合芯片面积和精度两方面的考量,本文设计的数模转换器采用高7位温度 计编码,低5位二进制编码的分割结构[1]。 图 3.1 12 位,100 兆 DAC 的结构图