正在加载图片...

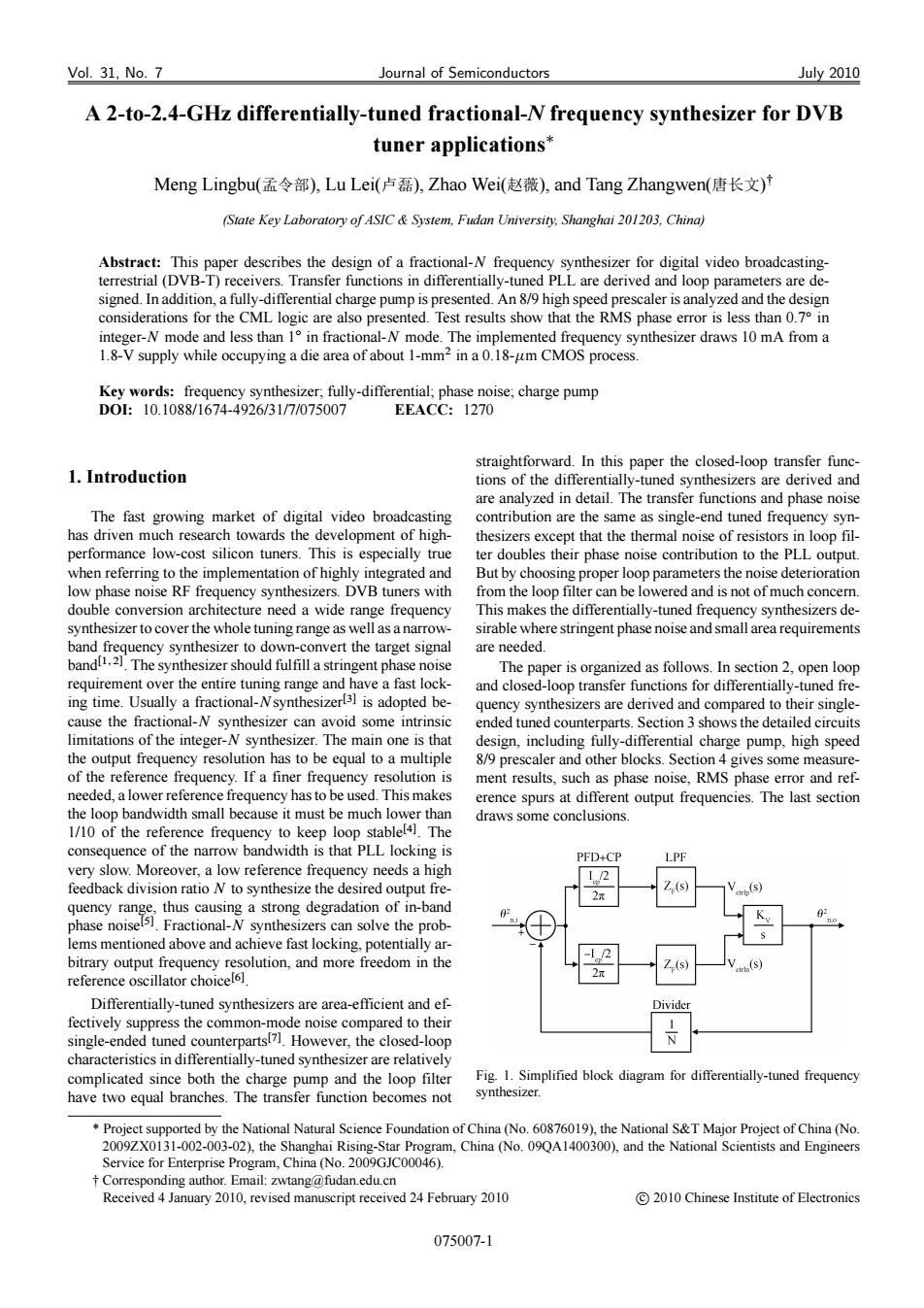

Vol.31,No.7 Journal of Semiconductors July 2010 A 2-to-2.4-GHz differentially-tuned fractional-N frequency synthesizer for DVB tuner applications* Meng Lingbu(孟令部),Lu Lei(卢磊),Zhao Wei(赵薇),and Tang Zhangwen(唐长文)t (State Key Laboratory of ASIC System,Fudan University.Shanghai 201203.China) Abstract:This paper describes the design of a fractional-N frequency synthesizer for digital video broadcasting- terrestrial(DVB-T)receivers.Transfer functions in differentially-tuned PLL are derived and loop parameters are de- signed.In addition,a fully-differential charge pump is presented.An 8/9 high speed prescaler is analyzed and the design considerations for the CML logic are also presented.Test results show that the RMS phase error is less than 0.7 in integer-N mode and less than 1 in fractional-N mode.The implemented frequency synthesizer draws 10 mA from a 1.8-V supply while occupying a die area of about 1-mm2 in a 0.18-um CMOS process. Key words:frequency synthesizer;fully-differential;phase noise;charge pump D0:10.1088/1674-4926/31/7/075007 EEACC:1270 straightforward.In this paper the closed-loop transfer func- 1.Introduction tions of the differentially-tuned synthesizers are derived and are analyzed in detail.The transfer functions and phase noise The fast growing market of digital video broadcasting contribution are the same as single-end tuned frequency syn- has driven much research towards the development of high- thesizers except that the thermal noise of resistors in loop fil- performance low-cost silicon tuners.This is especially true ter doubles their phase noise contribution to the PLL output. when referring to the implementation of highly integrated and But by choosing proper loop parameters the noise deterioration low phase noise RF frequency synthesizers.DVB tuners with from the loop filter can be lowered and is not of much concern. double conversion architecture need a wide range frequency This makes the differentially-tuned frequency synthesizers de- synthesizer to cover the whole tuning range as well as a narrow- sirable where stringent phase noise and small area requirements band frequency synthesizer to down-convert the target signal are needed. band[1.2).The synthesizer should fulfill a stringent phase noise The paper is organized as follows.In section 2,open loop requirement over the entire tuning range and have a fast lock- and closed-loop transfer functions for differentially-tuned fre- ing time.Usually a fractional-Nsynthesizer[3]is adopted be- quency synthesizers are derived and compared to their single- cause the fractional-N synthesizer can avoid some intrinsic ended tuned counterparts.Section 3 shows the detailed circuits limitations of the integer-N synthesizer.The main one is that design,including fully-differential charge pump,high speed the output frequency resolution has to be equal to a multiple 8/9 prescaler and other blocks.Section 4 gives some measure- of the reference frequency.If a finer frequency resolution is ment results,such as phase noise,RMS phase error and ref- needed,a lower reference frequency has to be used.This makes erence spurs at different output frequencies.The last section the loop bandwidth small because it must be much lower than draws some conclusions. 1/10 of the reference frequency to keep loop stablel4l.The consequence of the narrow bandwidth is that PLL locking is PFD+CP LPF very slow.Moreover,a low reference frequency needs a high /2 feedback division ratio N to synthesize the desired output fre- Z(s h(s) quency range,thus causing a strong degradation of in-band 03 phase noisels].Fractional-N synthesizers can solve the prob- lems mentioned above and achieve fast locking,potentially ar- bitrary output frequency resolution,and more freedom in the (S) reference oscillator choicel6]. Differentially-tuned synthesizers are area-efficient and ef- Divider fectively suppress the common-mode noise compared to their single-ended tuned counterpartsl71.However,the closed-loop characteristics in differentially-tuned synthesizer are relatively complicated since both the charge pump and the loop filter Fig.1.Simplified block diagram for differentially-tuned frequency have two equal branches.The transfer function becomes not synthesizer. Project supported by the National Natural Science Foundation of China (No.60876019),the National S&T Major Project of China (No. 2009ZX0131-002-003-02),the Shanghai Rising-Star Program,China (No.09QA1400300),and the National Scientists and Engineers Service for Enterprise Program,China(No.2009GJC00046). Corresponding author.Email:zwtang@fudan.edu.cn Received 4 January 2010,revised manuscript received 24 February 2010 C2010 Chinese Institute of Electronics 075007-1Vol. 31, No. 7 Journal of Semiconductors July 2010 A 2-to-2.4-GHz differentially-tuned fractional-N frequency synthesizer for DVB tuner applications Meng Lingbu(孟令部), Lu Lei(卢磊), Zhao Wei(赵薇), and Tang Zhangwen(唐长文) (State Key Laboratory of ASIC & System, Fudan University, Shanghai 201203, China) Abstract: This paper describes the design of a fractional-N frequency synthesizer for digital video broadcastingterrestrial (DVB-T) receivers. Transfer functions in differentially-tuned PLL are derived and loop parameters are designed. In addition, a fully-differential charge pump is presented. An 8/9 high speed prescaler is analyzed and the design considerations for the CML logic are also presented. Test results show that the RMS phase error is less than 0.7ı in integer-N mode and less than 1ı in fractional-N mode. The implemented frequency synthesizer draws 10 mA from a 1.8-V supply while occupying a die area of about 1-mm2 in a 0.18-m CMOS process. Key words: frequency synthesizer; fully-differential; phase noise; charge pump DOI: 10.1088/1674-4926/31/7/075007 EEACC: 1270 1. Introduction The fast growing market of digital video broadcasting has driven much research towards the development of highperformance low-cost silicon tuners. This is especially true when referring to the implementation of highly integrated and low phase noise RF frequency synthesizers. DVB tuners with double conversion architecture need a wide range frequency synthesizer to cover the whole tuning range as well as a narrowband frequency synthesizer to down-convert the target signal bandŒ1; 2. The synthesizer should fulfill a stringent phase noise requirement over the entire tuning range and have a fast locking time. Usually a fractional-NsynthesizerŒ3 is adopted because the fractional-N synthesizer can avoid some intrinsic limitations of the integer-N synthesizer. The main one is that the output frequency resolution has to be equal to a multiple of the reference frequency. If a finer frequency resolution is needed, a lower reference frequency has to be used. This makes the loop bandwidth small because it must be much lower than 1/10 of the reference frequency to keep loop stableŒ4. The consequence of the narrow bandwidth is that PLL locking is very slow. Moreover, a low reference frequency needs a high feedback division ratio N to synthesize the desired output frequency range, thus causing a strong degradation of in-band phase noiseŒ5. Fractional-N synthesizers can solve the problems mentioned above and achieve fast locking, potentially arbitrary output frequency resolution, and more freedom in the reference oscillator choiceŒ6 . Differentially-tuned synthesizers are area-efficient and effectively suppress the common-mode noise compared to their single-ended tuned counterpartsŒ7. However, the closed-loop characteristics in differentially-tuned synthesizer are relatively complicated since both the charge pump and the loop filter have two equal branches. The transfer function becomes not straightforward. In this paper the closed-loop transfer functions of the differentially-tuned synthesizers are derived and are analyzed in detail. The transfer functions and phase noise contribution are the same as single-end tuned frequency synthesizers except that the thermal noise of resistors in loop filter doubles their phase noise contribution to the PLL output. But by choosing proper loop parameters the noise deterioration from the loop filter can be lowered and is not of much concern. This makes the differentially-tuned frequency synthesizers desirable where stringent phase noise and small area requirements are needed. The paper is organized as follows. In section 2, open loop and closed-loop transfer functions for differentially-tuned frequency synthesizers are derived and compared to their singleended tuned counterparts. Section 3 shows the detailed circuits design, including fully-differential charge pump, high speed 8/9 prescaler and other blocks. Section 4 gives some measurement results, such as phase noise, RMS phase error and reference spurs at different output frequencies. The last section draws some conclusions. Fig. 1. Simplified block diagram for differentially-tuned frequency synthesizer. * Project supported by the National Natural Science Foundation of China (No. 60876019), the National S&T Major Project of China (No. 2009ZX0131-002-003-02), the Shanghai Rising-Star Program, China (No. 09QA1400300), and the National Scientists and Engineers Service for Enterprise Program, China (No. 2009GJC00046). Corresponding author. Email: zwtang@fudan.edu.cn Received 4 January 2010, revised manuscript received 24 February 2010 c 2010 Chinese Institute of Electronics 075007-1�