正在加载图片...

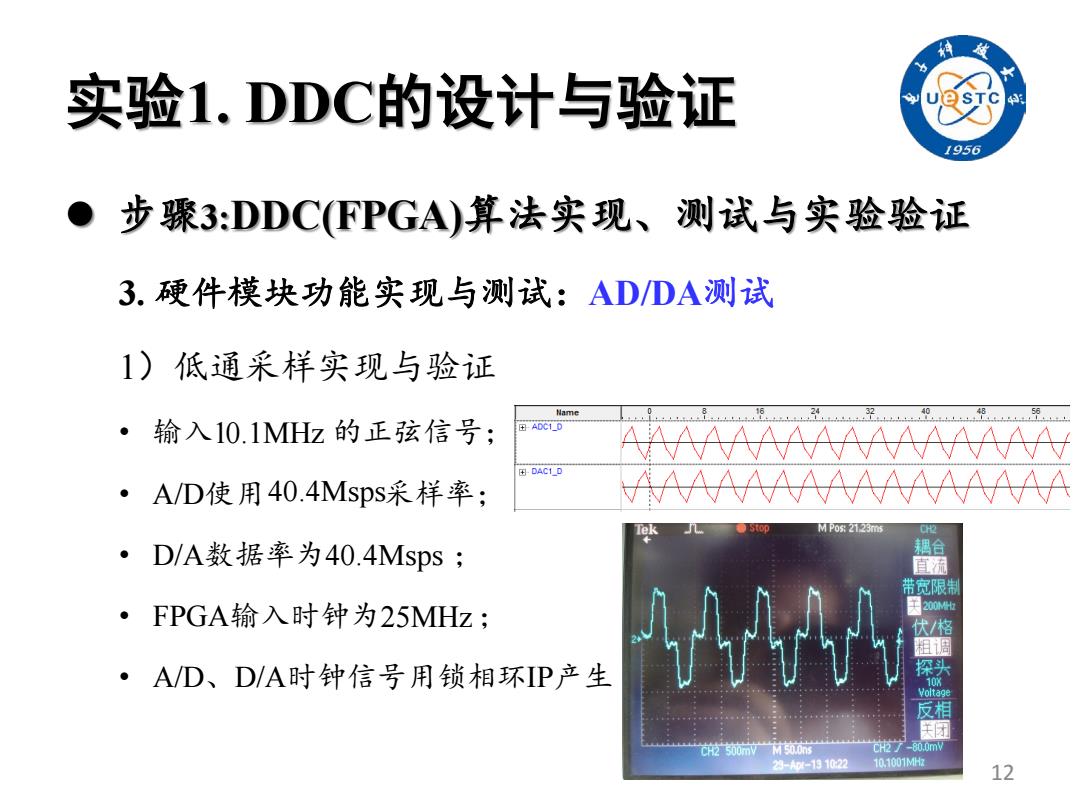

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 3.硬件模块功能实现与测试:ADDA测试 1)低通采样实现与验证 Name ·输入10.1MHz的正弦信号; ADCI D 田DAC1D ·A/D使用40.4Msps采样率; MP02123m D/A数据率为40.4Msps; 宽限 ·FPGA输入时钟为25MHz; 200m 大/格 粗调 ·A/D、D/A时钟信号用锁相环IP产生 探头 反相 天团 dH2了-80.0mN 29-0-131t22 101001MH 1212 步骤3:DDC(FPGA)算法实现、测试与实验验证 3. 硬件模块功能实现与测试:AD/DA测试 1)低通采样实现与验证 • 输入 的正弦信号; • A/D使用 采样率; • D/A数据率为 ; • FPGA输入时钟为 ; • A/D、D/A时钟信号用锁相环IP产生 10.1MHz 40.4Msps 40.4Msps 25MHz 实验1. DDC的设计与验证