正在加载图片...

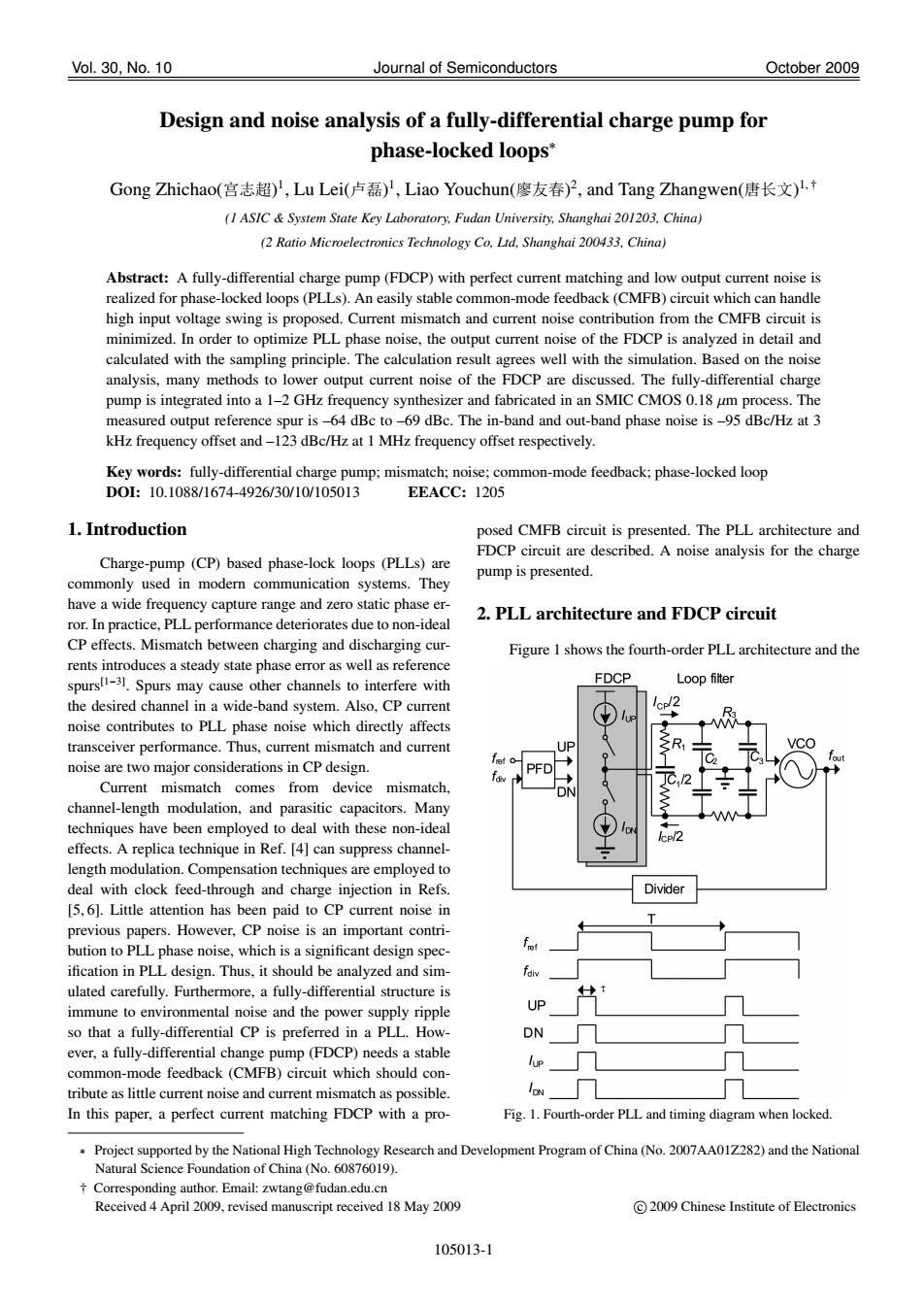

Vol.30,No.10 Journal of Semiconductors October 2009 Design and noise analysis of a fully-differential charge pump for phase-locked loops* Gong Zhichao(宫志超)',Lu Lei(卢磊)',Liao Youchun(廖友春)2,and Tang Zhangwen(唐长文)l,t (1 ASIC System State Key Laboratory,Fudan University,Shanghai 201203,China) (2 Ratio Microelectronics Technology Co,Ld,Shanghai 200433,China) Abstract:A fully-differential charge pump(FDCP)with perfect current matching and low output current noise is realized for phase-locked loops (PLLs).An easily stable common-mode feedback (CMFB)circuit which can handle high input voltage swing is proposed.Current mismatch and current noise contribution from the CMFB circuit is minimized.In order to optimize PLL phase noise,the output current noise of the FDCP is analyzed in detail and calculated with the sampling principle.The calculation result agrees well with the simulation.Based on the noise analysis,many methods to lower output current noise of the FDCP are discussed.The fully-differential charge pump is integrated into a 1-2 GHz frequency synthesizer and fabricated in an SMIC CMOS 0.18 um process.The measured output reference spur is-64 dBc to-69 dBc.The in-band and out-band phase noise is-95 dBc/Hz at 3 kHz frequency offset and-123 dBc/Hz at 1 MHz frequency offset respectively. Key words:fully-differential charge pump;mismatch;noise;common-mode feedback;phase-locked loop D0I:10.1088/1674-4926/30/10/105013 EEACC:1205 1.Introduction posed CMFB circuit is presented.The PLL architecture and FDCP circuit are described.A noise analysis for the charge Charge-pump (CP)based phase-lock loops (PLLs)are pump is presented. commonly used in modern communication systems.They have a wide frequency capture range and zero static phase er- ror.In practice,PLL performance deteriorates due to non-ideal 2.PLL architecture and FDCP circuit CP effects.Mismatch between charging and discharging cur- Figure 1 shows the fourth-order PLL architecture and the rents introduces a steady state phase error as well as reference spurs-31.Spurs may cause other channels to interfere with FDCP Loop filter the desired channel in a wide-band system.Also,CP current Icp/2 R noise contributes to PLL phase noise which directly affects transceiver performance.Thus,current mismatch and current UP noise are two major considerations in CP design. PFD Current mismatch comes from device mismatch, DN channel-length modulation,and parasitic capacitors.Many techniques have been employed to deal with these non-ideal Icp/2 effects.A replica technique in Ref.[4]can suppress channel- length modulation.Compensation techniques are employed to deal with clock feed-through and charge injection in Refs. Divider [5,6].Little attention has been paid to CP current noise in previous papers.However,CP noise is an important contri- bution to PLL phase noise,which is a significant design spec- ification in PLL design.Thus,it should be analyzed and sim- fdiv ulated carefully.Furthermore,a fully-differential structure is immune to environmental noise and the power supply ripple UP so that a fully-differential CP is preferred in a PLL.How- DN ever,a fully-differential change pump (FDCP)needs a stable common-mode feedback (CMFB)circuit which should con- tribute as little current noise and current mismatch as possible. In this paper,a perfect current matching FDCP with a pro- Fig.1.Fourth-order PLL and timing diagram when locked. Project supported by the National High Technology Research and Development Program of China(No.2007AA012282)and the National Natural Science Foundation of China (No.60876019). Corresponding author.Email:zwtang@fudan.edu.cn Received 4 April 2009,revised manuscript received 18 May 2009 C2009 Chinese Institute of Electronics 105013-1Vol. 30, No. 10 Journal of Semiconductors October 2009 Design and noise analysis of a fully-differential charge pump for phase-locked loops∗ Gong Zhichao(宫志超) 1 , Lu Lei(卢磊) 1 , Liao Youchun(廖友春) 2 , and Tang Zhangwen(唐长文) 1, † (1 ASIC & System State Key Laboratory, Fudan University, Shanghai 201203, China) (2 Ratio Microelectronics Technology Co, Ltd, Shanghai 200433, China) Abstract: A fully-differential charge pump (FDCP) with perfect current matching and low output current noise is realized for phase-locked loops (PLLs). An easily stable common-mode feedback (CMFB) circuit which can handle high input voltage swing is proposed. Current mismatch and current noise contribution from the CMFB circuit is minimized. In order to optimize PLL phase noise, the output current noise of the FDCP is analyzed in detail and calculated with the sampling principle. The calculation result agrees well with the simulation. Based on the noise analysis, many methods to lower output current noise of the FDCP are discussed. The fully-differential charge pump is integrated into a 1–2 GHz frequency synthesizer and fabricated in an SMIC CMOS 0.18 µm process. The measured output reference spur is –64 dBc to –69 dBc. The in-band and out-band phase noise is –95 dBc/Hz at 3 kHz frequency offset and –123 dBc/Hz at 1 MHz frequency offset respectively. Key words: fully-differential charge pump; mismatch; noise; common-mode feedback; phase-locked loop DOI: 10.1088/1674-4926/30/10/105013 EEACC: 1205 1. Introduction Charge-pump (CP) based phase-lock loops (PLLs) are commonly used in modern communication systems. They have a wide frequency capture range and zero static phase error. In practice, PLL performance deteriorates due to non-ideal CP effects. Mismatch between charging and discharging currents introduces a steady state phase error as well as reference spurs[1−3]. Spurs may cause other channels to interfere with the desired channel in a wide-band system. Also, CP current noise contributes to PLL phase noise which directly affects transceiver performance. Thus, current mismatch and current noise are two major considerations in CP design. Current mismatch comes from device mismatch, channel-length modulation, and parasitic capacitors. Many techniques have been employed to deal with these non-ideal effects. A replica technique in Ref. [4] can suppress channellength modulation. Compensation techniques are employed to deal with clock feed-through and charge injection in Refs. [5, 6]. Little attention has been paid to CP current noise in previous papers. However, CP noise is an important contribution to PLL phase noise, which is a significant design specification in PLL design. Thus, it should be analyzed and simulated carefully. Furthermore, a fully-differential structure is immune to environmental noise and the power supply ripple so that a fully-differential CP is preferred in a PLL. However, a fully-differential change pump (FDCP) needs a stable common-mode feedback (CMFB) circuit which should contribute as little current noise and current mismatch as possible. In this paper, a perfect current matching FDCP with a proposed CMFB circuit is presented. The PLL architecture and FDCP circuit are described. A noise analysis for the charge pump is presented. 2. PLL architecture and FDCP circuit Figure 1 shows the fourth-order PLL architecture and the Fig. 1. Fourth-order PLL and timing diagram when locked. ∗ Project supported by the National High Technology Research and Development Program of China (No. 2007AA01Z282) and the National Natural Science Foundation of China (No. 60876019). † Corresponding author. Email: zwtang@fudan.edu.cn Received 4 April 2009, revised manuscript received 18 May 2009 ⃝c 2009 Chinese Institute of Electronics 105013-1