正在加载图片...

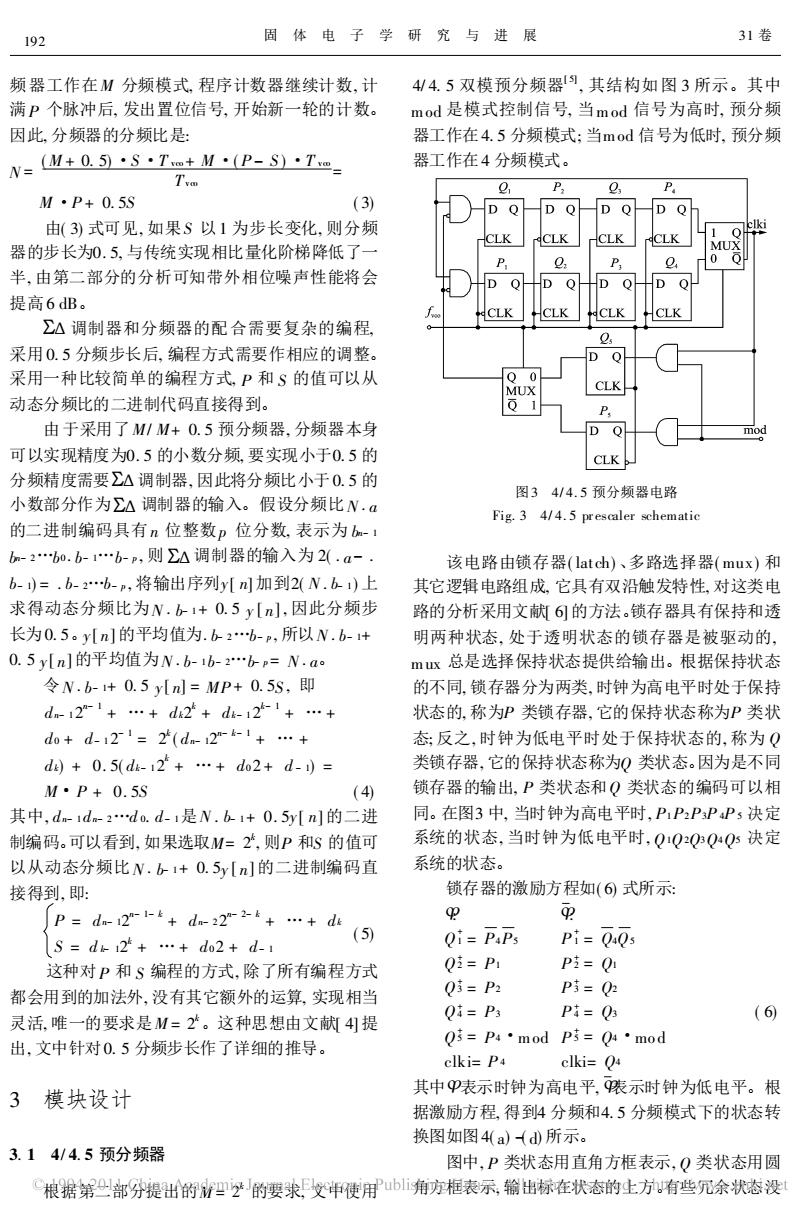

192 固体电子学研究与进展 31卷 频器工作在M分频模式,程序计数器继续计数,计 4/4.5双模预分频器1,其结构如图3所示。其中 满P个脉冲后,发出置位信号,开始新一轮的计数。 mod是模式控制信号,当mod信号为高时,预分频 因此,分频器的分频比是: 器工作在4.5分频模式:当mod信号为低时,预分频 N=M+0·S·T=+MP-S》·T四 器工作在4分频模式。 0 P 0, P M·P+0.5S (3) D Q D Q 由(3)式可见,如果S以1为步长变化,则分频 elki CLK CLK HCLK CLK 器的步长为0.5,与传统实现相比量化阶梯降低了一 MUX P P 0 半,由第二部分的分析可知带外相位噪声性能将会 D 0 D O D Q D Q 提高6dB。 CLK CLK CLK CLK ∑△调制器和分频器的配合需要复杂的编程, 采用0.5分频步长后,编程方式需要作相应的调整。 采用一种比较简单的编程方式,P和S的值可以从 00 MUX CLK 动态分频比的二进制代码直接得到。 Q 1 P 由于采用了M/M+0.5预分频器,分频器本身 mod 可以实现精度为0.5的小数分频,要实现小于0.5的 CLK 分频精度需要∑△调制器,因此将分频比小于0.5的 图34/4.5预分频器电路 小数部分作为∑△调制器的输入。假设分频比N.a Fig.3 4/4.5 prescaler schematic 的二进制编码具有n位整数p位分数,表示为b-1 bm-2b0.b-1…b-p,则D△调制器的输入为2(.a- 该电路由锁存器(latch)、多路选择器(mux)和 b-)=.b-2b-p,将输出序列y[n加到2(N.b1)上 其它逻辑电路组成,它具有双沿触发特性,对这类电 求得动态分频比为N.b1+0.5y[n,因此分频步 路的分析采用文献6的方法。锁存器具有保持和透 长为0.5。y[n]的平均值为.b2b-p,所以N.b-1+ 明两种状态,处于透明状态的锁存器是被驱动的, 0.5y[n的平均值为N.b-1b-2…hp=N.a mx总是选择保持状态提供给输出。根据保持状态 令N.b-+0.5yln=MP+0.5S,即 的不同,锁存器分为两类,时钟为高电平时处于保持 dn121+…+d2+dk-121+…+ 状态的,称为P类锁存器,它的保持状态称为P类状 do+d-12l=2(dn2-1+…+ 态:反之,时钟为低电平时处于保持状态的,称为Q d)+0.5(dk-12+…+do2+d-)= 类锁存器,它的保持状态称为Q类状态。因为是不同 M·P+0.5S (4) 锁存器的输出,P类状态和Q类状态的编码可以相 其中,dm-1d。-2…do.d-1是N.k1+0.5y[n的二进 同。在图3中,当时钟为高电平时,P1P2PPPs决定 制编码。可以看到,如果选取M=2,则P和S的值可 系统的状态,当时钟为低电平时,QQ2QQ4Q5决定 以从动态分频比N.b1+0.5y[n]的二进制编码直 系统的状态。 接得到,即 锁存器的激励方程如(6式所示: p=d-12-+da-22-2h+…+dk P 平 (5) S=dk2+…+do2+d-1 Qi=PaPs Pi=Q4Qs 这种对P和S编程的方式,除了所有编程方式 Q=P1 P克=Q 都会用到的加法外,没有其它额外的运算,实现相当 0=P2 P3=02 灵活,唯一的要求是M=2。这种思想由文献4提 Qi=P3 Pi=03 (6 出,文中针对0.5分频步长作了详细的推导。 Q5=P4·modP5=Q4·mod clki=P4 clki=04 3模块设计 其中P表示时钟为高电平,限示时钟为低电平。根 据激励方程,得到4分频和4.5分频模式下的状态转 换图如图4(a)(d)所示。 3.14/4.5预分频器 图中,P类状态用直角方框表示,Q类状态用圆 根据第部分提出的M四2的要求,文中使用ub角方框表示,输出标在状态的生,有些冗余状态没频器工作在M 分频模式, 程序计数器继续计数, 计 满P 个脉冲后, 发出置位信号, 开始新一轮的计数。 因此, 分频器的分频比是: N = ( M + 0. 5) ·S ·T vco+ M ·( P - S ) ·T vco Tvco = M ·P + 0. 5S ( 3) 由( 3) 式可见, 如果S 以1 为步长变化, 则分频 器的步长为0. 5, 与传统实现相比量化阶梯降低了一 半, 由第二部分的分析可知带外相位噪声性能将会 提高6 dB。 调制器和分频器的配合需要复杂的编程, 采用0. 5 分频步长后, 编程方式需要作相应的调整。 采用一种比较简单的编程方式, P 和 S 的值可以从 动态分频比的二进制代码直接得到。 由于采用了M/ M+ 0. 5 预分频器, 分频器本身 可以实现精度为0. 5 的小数分频, 要实现小于0. 5 的 分频精度需要 调制器, 因此将分频比小于0. 5 的 小数部分作为 调制器的输入。假设分频比N . a 的二进制编码具有n 位整数p 位分数, 表示为 bn- 1 bn- 2…b0 . b- 1…b- p , 则 调制器的输入为 2( . a- . b- 1) = . b- 2…b- p , 将输出序列y [ n] 加到2( N . b- 1 ) 上 求得动态分频比为N . b- 1+ 0. 5 y [ n] , 因此分频步 长为0. 5。y [ n] 的平均值为. b- 2…b- p , 所以N . b- 1+ 0. 5 y [ n] 的平均值为N . b- 1 b- 2…b- p= N . a。 令N . b- 1+ 0. 5 y [ n] = MP + 0. 5S , 即 dn- 1 2 n- 1 + … + dk2 k + dk- 1 2 k- 1 + … + d0 + d- 1 2 - 1 = 2 k ( dn- 12 n- k- 1 + … + dk) + 0. 5( dk- 1 2 k + … + d0 2 + d - 1) = M P + 0. 5S ( 4) 其中, dn- 1 dn- 2…d 0. d- 1是N . b- 1+ 0. 5y [ n] 的二进 制编码。可以看到, 如果选取M= 2 k , 则P 和S 的值可 以从动态分频比N . b- 1+ 0. 5y [ n] 的二进制编码直 接得到, 即: P = dn- 12 n- 1- k + dn- 2 2 n- 2- k + … + dk S = d k- 12 k + … + d0 2 + d- 1 ( 5) 这种对P 和 S 编程的方式, 除了所有编程方式 都会用到的加法外, 没有其它额外的运算, 实现相当 灵活, 唯一的要求是M = 2 k。这种思想由文献[ 4] 提 出, 文中针对0. 5 分频步长作了详细的推导。 3 模块设计 3. 1 4/ 4. 5 预分频器 根据第二部分提出的M = 2 k 的要求, 文中使用 4/ 4. 5 双模预分频器 [ 5] , 其结构如图 3 所示。其中 mod 是模式控制信号, 当mod 信号为高时, 预分频 器工作在4. 5 分频模式; 当mod 信号为低时, 预分频 器工作在4 分频模式。 图3 4/ 4. 5 预分频器电路 Fig. 3 4/ 4. 5 pr escaler schematic 该电路由锁存器( latch) 、多路选择器( mux ) 和 其它逻辑电路组成, 它具有双沿触发特性, 对这类电 路的分析采用文献[ 6] 的方法。锁存器具有保持和透 明两种状态, 处于透明状态的锁存器是被驱动的, mux 总是选择保持状态提供给输出。根据保持状态 的不同, 锁存器分为两类, 时钟为高电平时处于保持 状态的, 称为P 类锁存器, 它的保持状态称为P 类状 态; 反之, 时钟为低电平时处于保持状态的, 称为 Q 类锁存器, 它的保持状态称为Q 类状态。因为是不同 锁存器的输出, P 类状态和Q 类状态的编码可以相 同。在图3 中, 当时钟为高电平时, P1P2P3P 4P 5 决定 系统的状态, 当时钟为低电平时, Q1Q2Q3Q4Q5 决定 系统的状态。 锁存器的激励方程如( 6) 式所示: : : Q + 1 = P4P5 P + 1 = Q4Q5 Q + 2 = P1 P + 2 = Q1 Q + 3 = P2 P + 3 = Q2 Q + 4 = P3 P + 4 = Q3 ( 6) Q + 5 = P4·mod P + 5 = Q4·mo d clki= P 4 clki= Q4 其中表示时钟为高电平, 表示时钟为低电平。根 据激励方程, 得到4 分频和4. 5 分频模式下的状态转 换图如图4( a) -( d) 所示。 图中, P 类状态用直角方框表示, Q 类状态用圆 角方框表示, 输出标在状态的上方。有些冗余状态没 192 固 体 电 子 学 研 究 与 进 展 31 卷����