正在加载图片...

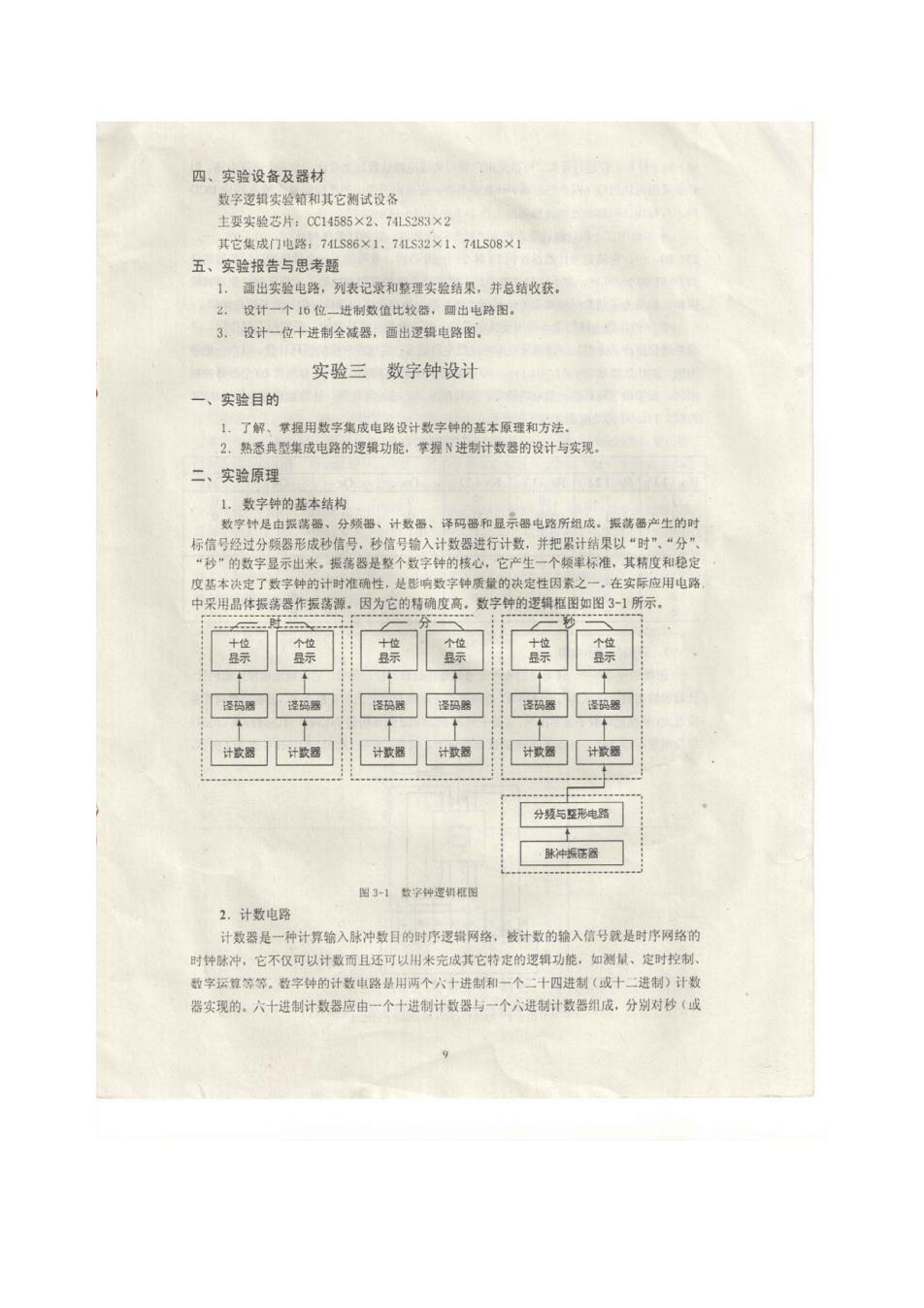

四、实验设备及器材 数字逻辑实验箱和其它测试设备 主要实验芯片:CC14585×2、741S283×2 其它集成门电路:74LS86×1、74LS32×1、74LS08×1 五、实验报告与思考题 1. 画出实验电路,列表记录和整理实验结果,并总结收获, 2.设计一个16位一进制数值比较器,画出电路图 3.设计一位十进制全减器,画出逻辑电路图, 实验三数字钟设计 一、实验目的 1.了解、掌握用数字集成电路设计数字钟的基本原理和方法 2.熟悉典型集成电路的逻辑功能,掌握N进制计数器的设计与实现。 二、实验原理 1.数字钟的基本结构 数字钟是由振荡器、分频器、计数器、译码器和显示器电路所组成。振荡器产生的时 标信号经过分频器形成秒信号,秒信号输入计数器进行计数,并把累计结果以“时”,“分” “秒”的数字显示出来。振荡器是整个数字钟的核心,它产生一个烦率标准,其精度和稳定 度基本决定了数字钟的计时准确性,是影响数字钟质量的决定性因素之一,在实际应用电路 中采用品体振荡器作振荡源。因为它的精确度高。数字钟的逻辑框图如图31所示。 十位 个位 十位 个位 十位 个位 显示 显示 显示 显示 显示 显示 怪玛器 路码器 怪码器 译码瑶 译码器 译码器 计数器 计数器 计数器 计数器 计数器 计数器 分频与坚形电路 脉冲振活器 图3-1数字钟逻辑框图 2.计数电路 计数器是一种计算输入脉冲数目的时序逻辑网络,被计数的输入信号就是时序网络的 时钟脉冲,它不仅可以计数而且还可以用米完成其它特定的逻辑功能,如测量、定时控制、 数字运算等等。数字钟的计数电路是用两个六十进制和一个二十四进制(或十二进制)计数 器实现的。六十进制计数器应由一个十进制计数器与一个六进制计数器组成,分别对秒(或