正在加载图片...

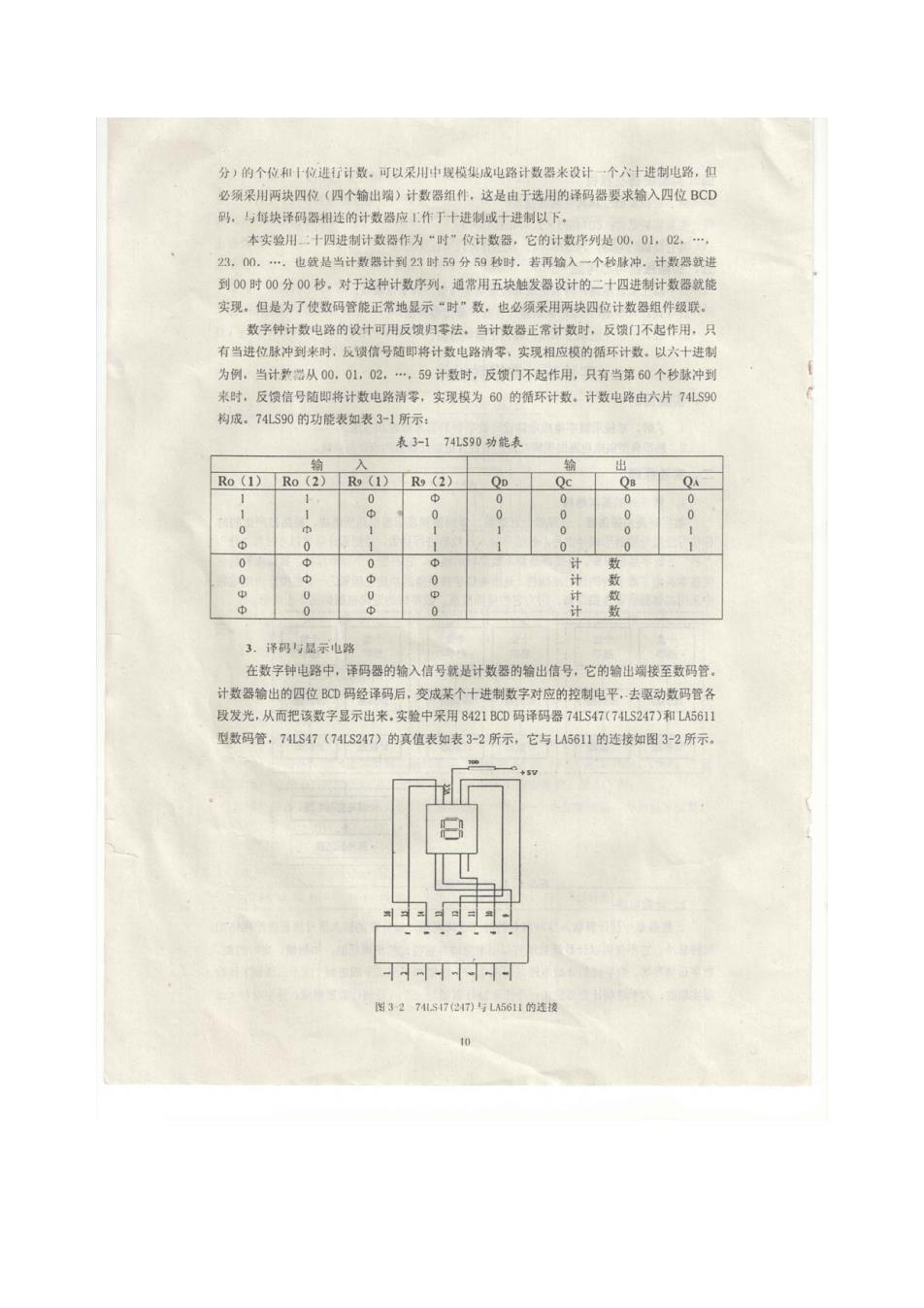

分)的个位和十位进行计数。可以采用中规模集成电路计数器米设计一个六十进制电路,但 必须采用两块四位(四个输出端)计数器组件,这是由于选用的译码器要求输入四位BCD 码,与每块译码器相连的计数器应工作于十进制域十进制以下。 本实验用二十四进制计数器作为“时”位计数器,它的计数序列是00.01,02…, 23.00.….也就是当计数器计到23时9分9秒时,若再输入一个秒脉冲.计数器就进 到00时00分00秒,对于这种计数序列,通常用五块触发器设计的二十四进制计数器就能 实现。但是为了使数码管能正常地显示“时”数,也必须采用两块四位计数器组件级联。 数字钟计数电路的设计可用反馈归零法,当计数器正常计数时,反馈门不起作用,只 有当进位脉冲到来时,反馈信号随即将计数电路清零,实现相应模的循环计数。以六十进制 为例,当计数誉从00,01,02,,59计数时,反馈门不起作用,只有当第60个秒燕冲到 来时,反馈信号随即将计数电路清零,实现模为60的循环计数。计数电路由六片74LS90 构成。74S90的功能表如表3-1所示: 表3-174LS90功能表 出 Ro(1)Ro(2)Rg(1)Rg(2) OD Qc QB QA 0 0 0 0 0 中 0 0 0 0 0 0 1 0 0 1 0 0 0 0 中 0 φ 计 0 中 0 计 0 0 0 数 中 0 中 0 3,译码与显示电路 在数字钟电路中,译码器的输入信号就是计数器的输出信号,它的输出端接至数码管。 计数器输出的四位BCD码经译码后,变成某个十进制数字对应的控制电平,去驱动数码管各 段发光,从而把该数字显示出来,实验中采用8421BCD码译码器74LS47(74LS247)和LA5611 型数码管,74LS47(74LS247)的真值表如表3-2所示,它与L45611的连接如图3-2所示, 图3274517(247)与LA5611的连接 10