正在加载图片...

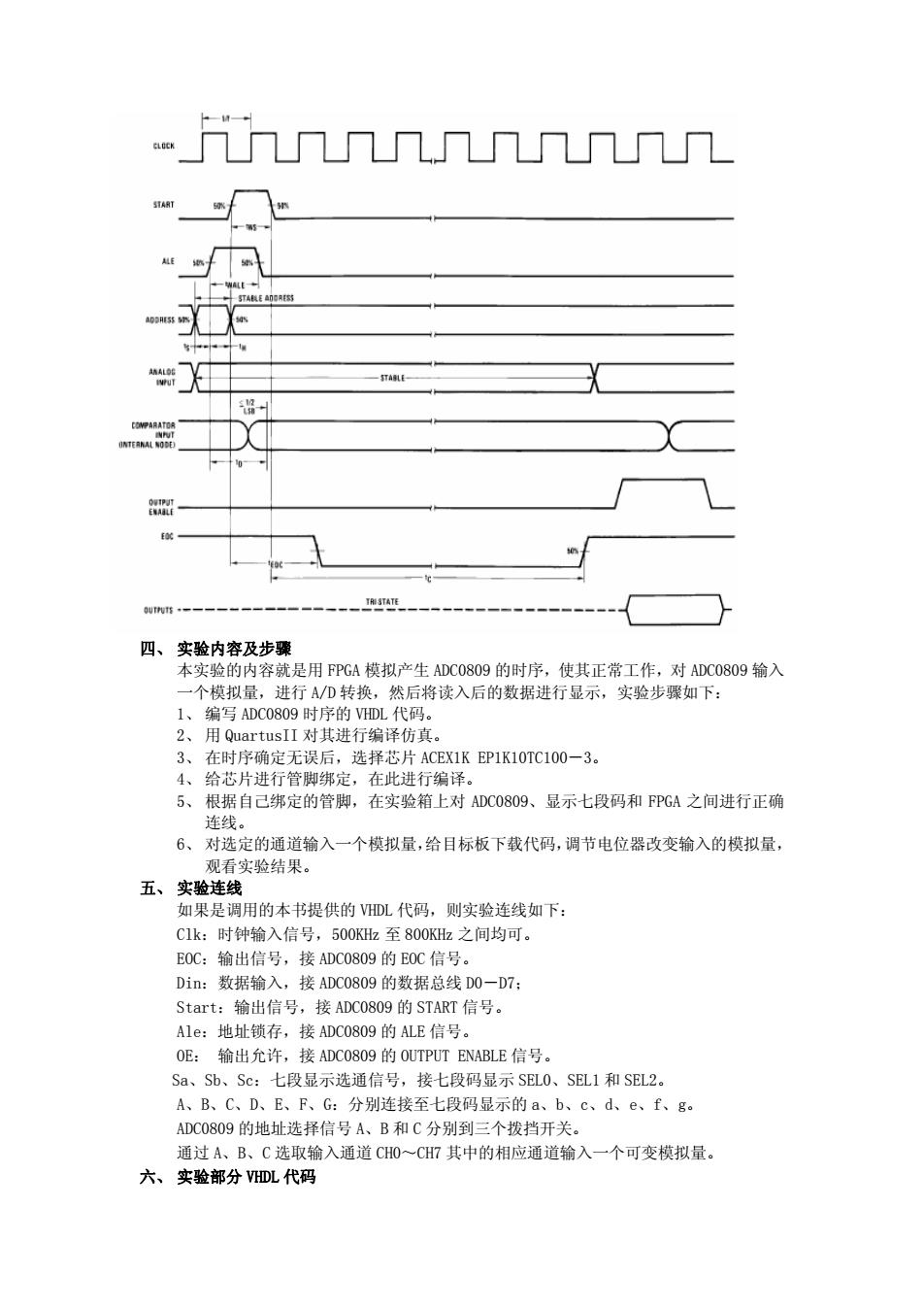

.Jihmu A AMAL能 T STASLE 锅 COMPARATOR ONTERNAL NODE 0 9Ut判5+一 四、实验内容及步骤 本实验的内容就是用FPGA模拟产生ADC0809的时序,使其正常工作,对ADC0809输入 一个模拟量,进行AD转换,然后将读入后的数据进行显示,实验步骤如下: 1、编写ADC0809时序的VHDL代码。 2、用QuartusII对其进行编译仿真。 3、在时序确定无误后,选择芯片ACEX1KEP1K10TC100一3。 4、给芯片进行管脚绑定,在此进行编译。 5、根据自己绑定的管脚,在实验箱上对ADCO809、显示七段码和FPGA之间进行正确 连线。 6、对选定的通道输入一个模拟量,给目标板下载代码,调节电位器改变输入的模拟量, 观看实验结果。 五、实验连线 如果是调用的本书提供的HDL代码,则实验连线如下: C1k:时钟输入信号,500Kz至800KHz之间均可。 E0C:输出信号,接ADC0809的E0C信号。 Din:数据输入,接ADCO809的数据总线D0-D7: Start:输出信号,接ADCO8O9的START信号。 A1e:地址锁存,接ADC0809的ALE信号。 OE:输出允许,接ADCO8O9的OUTPUT ENABLE信号。 Sa、Sb、Sc:七段显示选通信号,接七段码显示SEL0、SEL1和SEL2。 A、B、C、D、E、F、G:分别连接至七段码显示的a、b、c、d、e、f、g。 ADC0809的地址选择信号A、B和C分别到三个拨挡开关。 通过A、B、C选取输入通道CHO~CH7其中的相应通道输入一个可变模拟量。 六、实验部分HDL代码四、 实验内容及步骤 本实验的内容就是用 FPGA 模拟产生 ADC0809 的时序,使其正常工作,对 ADC0809 输入 一个模拟量,进行 A/D 转换,然后将读入后的数据进行显示,实验步骤如下: 1、 编写 ADC0809 时序的 VHDL 代码。 2、 用 QuartusII 对其进行编译仿真。 3、 在时序确定无误后,选择芯片 ACEX1K EP1K10TC100-3。 4、 给芯片进行管脚绑定,在此进行编译。 5、 根据自己绑定的管脚,在实验箱上对 ADC0809、显示七段码和 FPGA 之间进行正确 连线。 6、 对选定的通道输入一个模拟量,给目标板下载代码,调节电位器改变输入的模拟量, 观看实验结果。 五、 实验连线 如果是调用的本书提供的 VHDL 代码,则实验连线如下: Clk:时钟输入信号,500KHz 至 800KHz 之间均可。 EOC:输出信号,接 ADC0809 的 EOC 信号。 Din:数据输入,接 ADC0809 的数据总线 D0-D7; Start:输出信号,接 ADC0809 的 START 信号。 Ale:地址锁存,接 ADC0809 的 ALE 信号。 OE: 输出允许,接 ADC0809 的 OUTPUT ENABLE 信号。 Sa、Sb、Sc:七段显示选通信号,接七段码显示 SEL0、SEL1 和 SEL2。 A、B、C、D、E、F、G:分别连接至七段码显示的 a、b、c、d、e、f、g。 ADC0809 的地址选择信号 A、B 和 C 分别到三个拨挡开关。 通过 A、B、C 选取输入通道 CH0~CH7 其中的相应通道输入一个可变模拟量。 六、 实验部分 VHDL 代码