正在加载图片...

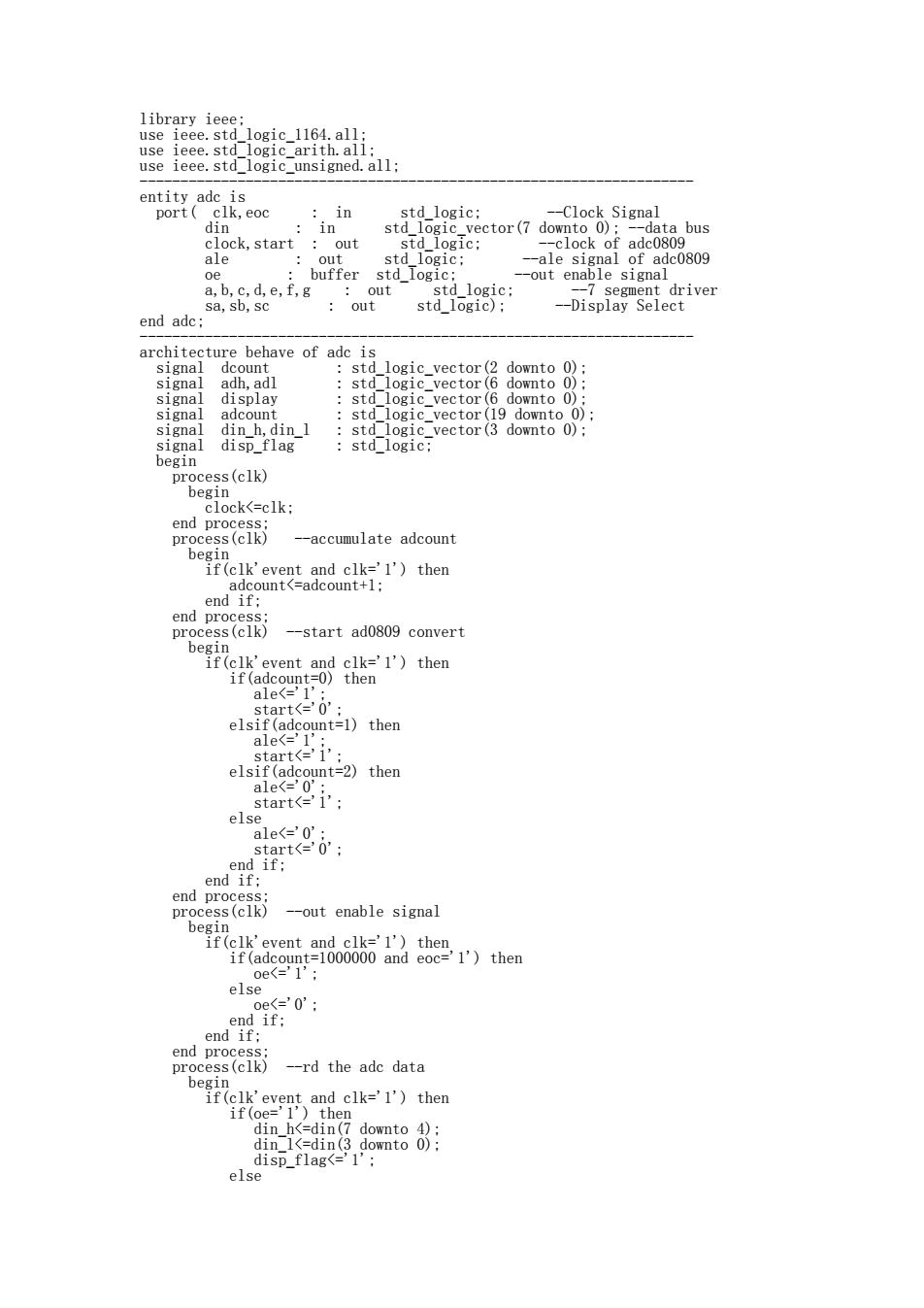

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all: use ieee.std_logic_unsigned.all; entity adc is port clk,eoc in std logic: Clock Signal din 10 std_logic_vector(7 downto 0); --data bus clock,start out std_logic: --clock of adc0809 ale out std logic; -ale signal of adc0809 oe buffer std logic; --out enable signal a,b,c,d,e,f,g :out std logic; --7 segment driver sa,sb,sc out std logic): --Display Select end adc; architecture behave of adc is signal dcount std_logic_vector(2 downto 0); signal adh,adl std-logic_vector(6 downto 0): signal display std_logic_vector(6 downto 0); signal adcount std logic vector(19 downto 0): signal din h,din l std logic vector(3 downto 0); signal disp_flag std logic; begin process(clk) begin clock<=clk; end process; process(clk) --accumulate adcount begin if(clk'event and clk='1')then adcount<=adcount+1; end if; end process; process(clk) --start ad0809 convert begin if(clk'event and clk='1')then if(adcount=0)then ale<='1, start<='0' elsif(adcount=1)then ale<='1' start=': elsif(adcount=2)then ale<='0': start='i'; else ale<=0': start<='0'; end if; end if; end process process(clk) --out enable signal begin if(clk'event and clk='1')then if(adcount=1000000 and eoc='1')then 0e<='1': else e<='0': end if; end if: end process; process(clk) --rd the adc data begin if(clk'event and clk='1')then if(oe='1')then din h<=din(7 downto 4); din 1<=din(3 downto 0): disp_flag<='1'; elslibrary ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; -------------------------------------------------------------------- entity adc is port( clk,eoc : in std_logic; --Clock Signal din : in std_logic_vector(7 downto 0); --data bus clock,start : out std_logic; --clock of adc0809 ale : out std_logic; --ale signal of adc0809 oe : buffer std_logic; --out enable signal a,b,c,d,e,f,g : out std_logic; --7 segment driver sa,sb,sc : out std_logic); --Display Select end adc; -------------------------------------------------------------------- architecture behave of adc is signal dcount : std_logic_vector(2 downto 0); signal adh,adl : std_logic_vector(6 downto 0); signal display : std_logic_vector(6 downto 0); signal adcount : std_logic_vector(19 downto 0); signal din_h,din_l : std_logic_vector(3 downto 0); signal disp_flag : std_logic; begin process(clk) begin clock<=clk; end process; process(clk) --accumulate adcount begin if(clk'event and clk='1') then adcount<=adcount+1; end if; end process; process(clk) --start ad0809 convert begin if(clk'event and clk='1') then if(adcount=0) then ale<='1'; start<='0'; elsif(adcount=1) then ale<='1'; start<='1'; elsif(adcount=2) then ale<='0'; start<='1'; else ale<='0'; start<='0'; end if; end if; end process; process(clk) --out enable signal begin if(clk'event and clk='1') then if(adcount=1000000 and eoc='1') then oe<='1'; else oe<='0'; end if; end if; end process; process(clk) --rd the adc data begin if(clk'event and clk='1') then if(oe='1') then din_h<=din(7 downto 4); din_l<=din(3 downto 0); disp_flag<='1'; else