正在加载图片...

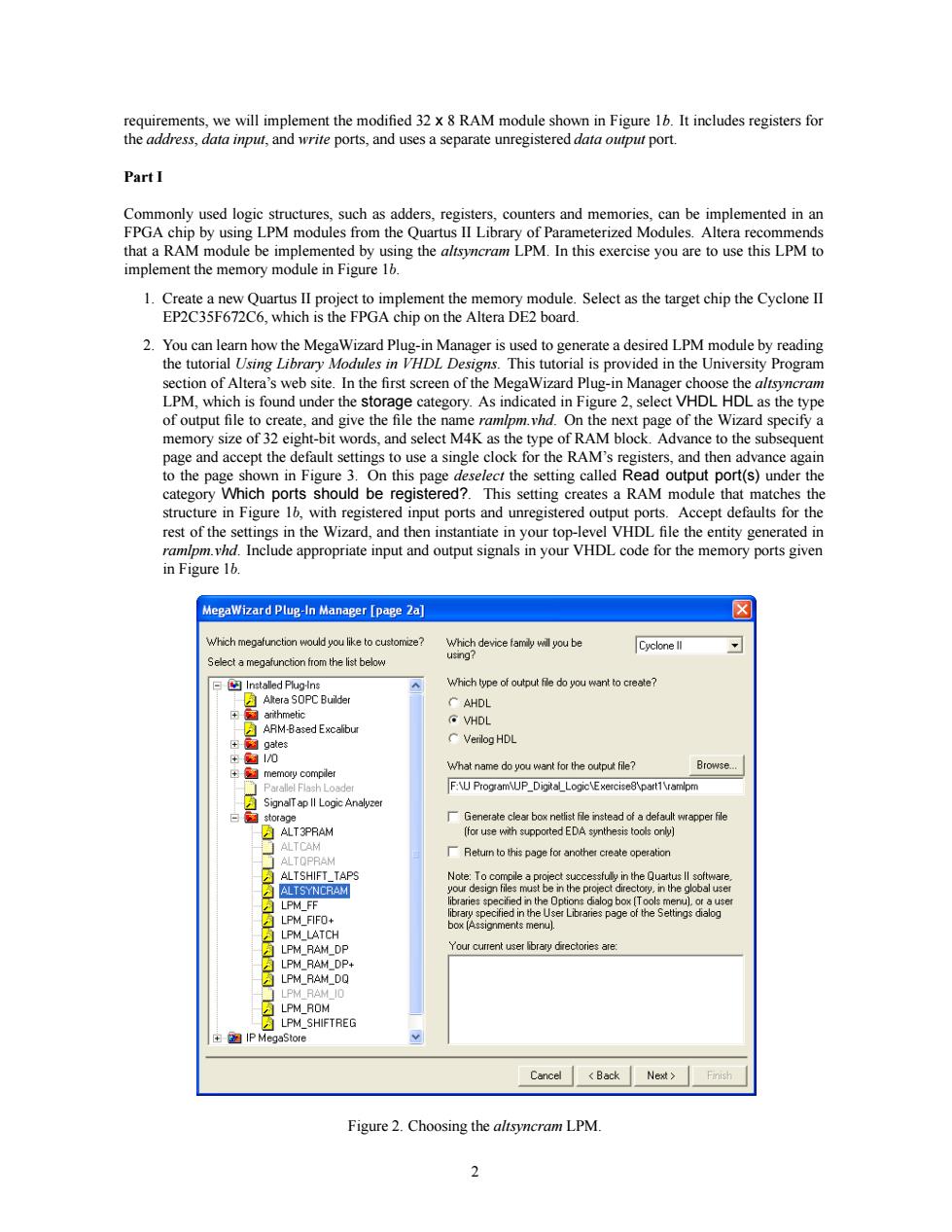

ents we will ir ent the modified 32 x 8 rAm module sh inFigure It includes registers for PartI Com nly used logic structur such as adders counters and m that a RAM module be implemented by using the altsyncram LPM.In this exercise you are to use this LPM to implement the memory module in Figure 16 CP6 e o t le v Ouartus II project to implement the dule.Select as the target chip the Cyclone II 2.how the MegaWizard Plug-in Manager is used to generatea desired LPM module by reading the tutor s in VHDL De ersity Program As indicated in Fis of output file to create,and give the file the name ramlpm.On the next page of the Wizard specify a accept Fig ngs to use a single clock aled Read ou category Which ports should be registered?This setting creates a RAM module that matches the structurein Figure with registered input ports and unregistered output ports.Accept defaults for the VHDL file the entity generated in ude appropriate input and output signals in your code for the memory ports given MegaWizard Plug-In Manager [page 2a] ☒ Selectameosfuncfon tiom the list belw Which ypefledoe? AHDL what name do you want for the output file? Browse.. F:PogaUP DigiLogic\Ekerci parpm ALT 3FRAM 厂Retmothpgelesnctgcesecpesen CRAN aTocnCearneeceenhe9uatsete Concel<Back Nest>」fm Figure 2.Choosing the altsyncram LPM requirements, we will implement the modified 32 x 8 RAM module shown in Figure 1b. It includes registers for the address, data input, and write ports, and uses a separate unregistered data output port. Part I Commonly used logic structures, such as adders, registers, counters and memories, can be implemented in an FPGA chip by using LPM modules from the Quartus II Library of Parameterized Modules. Altera recommends that a RAM module be implemented by using the altsyncram LPM. In this exercise you are to use this LPM to implement the memory module in Figure 1b. 1. Create a new Quartus II project to implement the memory module. Select as the target chip the Cyclone II EP2C35F672C6, which is the FPGA chip on the Altera DE2 board. 2. You can learn how the MegaWizard Plug-in Manager is used to generate a desired LPM module by reading the tutorial Using Library Modules in VHDL Designs. This tutorial is provided in the University Program section of Altera’s web site. In the first screen of the MegaWizard Plug-in Manager choose the altsyncram LPM, which is found under the storage category. As indicated in Figure 2, select VHDL HDL as the type of output file to create, and give the file the name ramlpm.vhd. On the next page of the Wizard specify a memory size of 32 eight-bit words, and select M4K as the type of RAM block. Advance to the subsequent page and accept the default settings to use a single clock for the RAM’s registers, and then advance again to the page shown in Figure 3. On this page deselect the setting called Read output port(s) under the category Which ports should be registered?. This setting creates a RAM module that matches the structure in Figure 1b, with registered input ports and unregistered output ports. Accept defaults for the rest of the settings in the Wizard, and then instantiate in your top-level VHDL file the entity generated in ramlpm.vhd. Include appropriate input and output signals in your VHDL code for the memory ports given in Figure 1b. Figure 2. Choosing the altsyncram LPM. 2