正在加载图片...

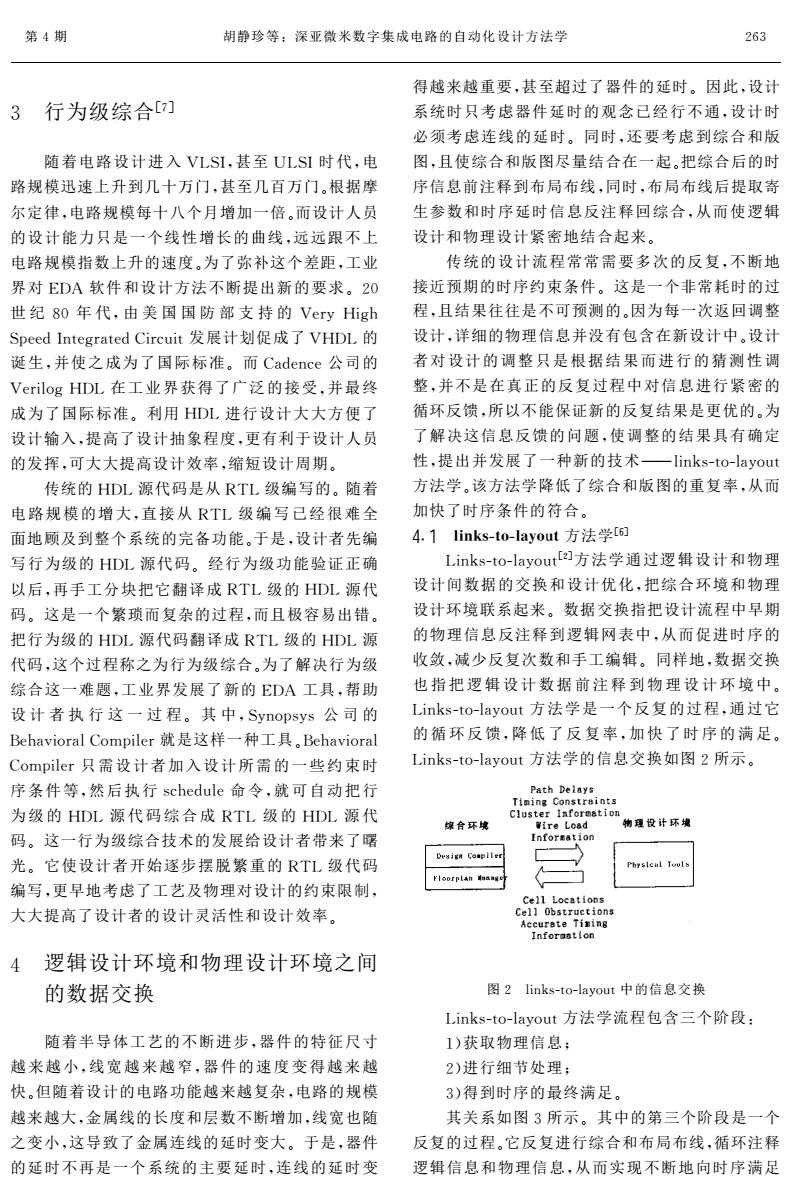

第4期 胡静珍等:深亚微米数字集成电路的自动化设计方法学 263 得越来越重要,甚至超过了器件的延时。因此,设计 3 行为级综合[] 系统时只考虑器件延时的观念已经行不通,设计时 必须考虑连线的延时。同时,还要考虑到综合和版 随着电路设计进入VLSI,甚至ULSI时代,电 图,且使综合和版图尽量结合在一起。把综合后的时 路规模迅速上升到几十万门,甚至几百万门。根据摩 序信息前注释到布局布线,同时,布局布线后提取寄 尔定律,电路规模每十八个月增加一倍。而设计人员 生参数和时序延时信息反注释回综合,从而使逻辑 的设计能力只是一个线性增长的曲线,远远跟不上 设计和物理设计紧密地结合起来。 电路规模指数上升的速度。为了弥补这个差距,工业 传统的设计流程常常需要多次的反复,不断地 界对EDA软件和设计方法不断提出新的要求。20 接近预期的时序约束条件。这是一个非常耗时的过 世纪80年代,由美国国防部支持的Very High 程,且结果往往是不可预测的。因为每一次返回调整 Speed Integrated Circuit发展计划促成了VHDL的 设计,详细的物理信息并没有包含在新设计中。设计 诞生,并使之成为了国际标准。而Cadence公司的 者对设计的调整只是根据结果而进行的猜测性调 Verilog HDL在工业界获得了广泛的接受,并最终 整,并不是在真正的反复过程中对信息进行紧密的 成为了国际标准。利用HDL进行设计大大方便了 循环反馈,所以不能保证新的反复结果是更优的。为 设计输入,提高了设计抽象程度,更有利于设计人员 了解决这信息反馈的问题,使调整的结果具有确定 的发挥,可大大提高设计效率,缩短设计周期。 性,提出并发展了一种新的技术一links-to-layout 传统的HDL源代码是从RTL级编写的。随着 方法学。该方法学降低了综合和版图的重复率,从而 电路规模的增大,直接从RTL级编写已经很难全 加快了时序条件的符合。 面地顾及到整个系统的完备功能。于是,设计者先编 4.1 links-to-layout方法学[6] 写行为级的HDL源代码。经行为级功能验证正确 Links--to-layout幻方法学通过逻辑设计和物理 以后,再手工分块把它翻译成RTL级的HDL源代 设计间数据的交换和设计优化,把综合环境和物理 码。这是一个繁琐而复杂的过程,而且极容易出错。 设计环境联系起来。数据交换指把设计流程中早期 把行为级的HDL源代码翻译成RTL级的HDL源 的物理信息反注释到逻辑网表中,从而促进时序的 代码,这个过程称之为行为级综合。为了解决行为级 收敛,减少反复次数和手工编辑。同样地,数据交换 综合这一难题,工业界发展了新的EDA工具,帮助 也指把逻辑设计数据前注释到物理设计环境中。 设计者执行这一过程。其中,Synopsys公司的 Links-to-layout方法学是一个反复的过程,通过它 Behavioral Compiler就是这样一种工具。Behavioral 的循环反馈,降低了反复率,加快了时序的满足。 Compiler只需设计者加入设计所需的一些约束时 Links-to-layout方法学的信息交换如图2所示。 序条件等,然后执行schedule命令,就可自动把行 Path Delays Timing Constraints 为级的HDL源代码综合成RTL级的HDL源代 Cluster Information 擦合环境 Wire Load 物理设计环城 码。这一行为级综合技术的发展给设计者带来了曙 Infor图ation Desiga CoaplLer 光。它使设计者开始逐步摆脱繁重的RTL级代码 Phrslcul Touls 编写,更早地考虑了工艺及物理对设计的约束限制, Cell Locations 大大提高了设计者的设计灵活性和设计效率。 Cel】0 bstructions Accurate Tining Inforastion 逻辑设计环境和物理设计环境之间 的数据交换 图2 links--to-layout中的信息交换 Links-to-layout方法学流程包含三个阶段: 随着半导体工艺的不断进步,器件的特征尺寸 1)获取物理信息: 越来越小,线宽越来越窄,器件的速度变得越来越 2)进行细节处理; 快。但随着设计的电路功能越来越复杂,电路的规模 3)得到时序的最终满足。 越来越大,金属线的长度和层数不断增加,线宽也随 其关系如图3所示。其中的第三个阶段是一个 之变小,这导致了金属连线的延时变大。于是,器件 反复的过程。它反复进行综合和布局布线,循环注释 的延时不再是一个系统的主要延时,连线的延时变 逻辑信息和物理信息,从而实现不断地向时序满足! 行为级综合"#$ 随着电路设计进入 %&’()甚至 *&’(时代)电 路规模迅速上升到几十万门)甚至几百万门+根据摩 尔定律)电路规模每十八个月增加一倍+而设计人员 的设计能力只是一个线性增长的曲线)远远跟不上 电路规模指数上升的速度+为了弥补这个差距)工业 界对 ,-.软件和设计方法不断提出新的要求+/0 世 纪 10年 代)由 美 国 国 防 部 支 持 的 %2345678 ’922:(;<273=<2:>63?@6<发展计划促成了 %5-&的 诞生)并使之成为了国际标准+而 >=:2;?2公司的 %236AB75-&在工业界获得了广泛的接受)并最终 成为了国际标准+利用 5-&进行设计大大方便了 设计输入)提高了设计抽象程度)更有利于设计人员 的发挥)可大大提高设计效率)缩短设计周期+ 传统的 5-&源代码是从 CD&级编写的+随着 电路规模的增大)直接从 CD&级编写已经很难全 面地顾及到整个系统的完备功能+于是)设计者先编 写行为级的 5-&源代码+经行为级功能验证正确 以后)再手工分块把它翻译成 CD&级的 5-&源代 码+这是一个繁琐而复杂的过程)而且极容易出错+ 把行为级的 5-&源代码翻译成 CD&级的 5-&源 代码)这个过程称之为行为级综合+为了解决行为级 综合这一难题)工业界发展了新的 ,-.工具)帮助 设 计 者 执 行 这 一 过 程+ 其 中)’4;B9E4E公 司 的 F28=G6B3=A>BH96A23就是这样一种工具+F28=G6B3=A >BH96A23只需设计者加入设计所需的一些约束时 序条件等)然后执行 E?82:@A2命令)就可自动把行 为级的 5-&源代码综合 成 CD&级 的 5-&源 代 码+这一行为级综合技术的发展给设计者带来了曙 光+它使设计者开始逐步摆脱繁重的 CD&级代码 编写)更早地考虑了工艺及物理对设计的约束限制) 大大提高了设计者的设计灵活性和设计效率+ I 逻辑设计环境和物理设计环境之间 的数据交换 随着半导体工艺的不断进步)器件的特征尺寸 越来越小)线宽越来越窄)器件的速度变得越来越 快+但随着设计的电路功能越来越复杂)电路的规模 越来越大)金属线的长度和层数不断增加)线宽也随 之变小)这导致了金属连线的延时变大+于是)器件 的延时不再是一个系统的主要延时)连线的延时变 得越来越重要)甚至超过了器件的延时+因此)设计 系统时只考虑器件延时的观念已经行不通)设计时 必须考虑连线的延时+同时)还要考虑到综合和版 图)且使综合和版图尽量结合在一起+把综合后的时 序信息前注释到布局布线)同时)布局布线后提取寄 生参数和时序延时信息反注释回综合)从而使逻辑 设计和物理设计紧密地结合起来+ 传统的设计流程常常需要多次的反复)不断地 接近预期的时序约束条件+这是一个非常耗时的过 程)且结果往往是不可预测的+因为每一次返回调整 设计)详细的物理信息并没有包含在新设计中+设计 者对设计的调整只是根据结果而进行的猜测性调 整)并不是在真正的反复过程中对信息进行紧密的 循环反馈)所以不能保证新的反复结果是更优的+为 了解决这信息反馈的问题)使调整的结果具有确定 性)提出并发展了一种新的技术JJ A6;KEL<BLA=4B@< 方法学+该方法学降低了综合和版图的重复率)从而 加快了时序条件的符合+ MNO PQRSTUVWUPXYWZV方法学"[$ &6;KEL<BLA=4B@< "/$方法学通过逻辑设计和物理 设计间数据的交换和设计优化)把综合环境和物理 设计环境联系起来+数据交换指把设计流程中早期 的物理信息反注释到逻辑网表中)从而促进时序的 收敛)减少反复次数和手工编辑+同样地)数据交换 也指把逻辑设计数据前 注 释 到 物 理 设 计 环 境 中+ &6;KEL<BLA=4B@<方法学是一个反复的过程)通过它 的 循 环 反 馈)降 低 了 反 复 率)加 快 了 时 序 的 满 足+ &6;KEL<BLA=4B@<方法学的信息交换如图 /所示+ 图 / A6;KEL<BLA=4B@<中的信息交换 &6;KEL<BLA=4B@<方法学流程包含三个阶段\ ]^获取物理信息_ /^进行细节处理_ !^得到时序的最终满足+ 其关系如图 !所示+其中的第三个阶段是一个 反复的过程+它反复进行综合和布局布线)循环注释 逻辑信息和物理信息)从而实现不断地向时序满足 第 I期 胡静珍等\深亚微米数字集成电路的自动化设计方法学 /‘!