正在加载图片...

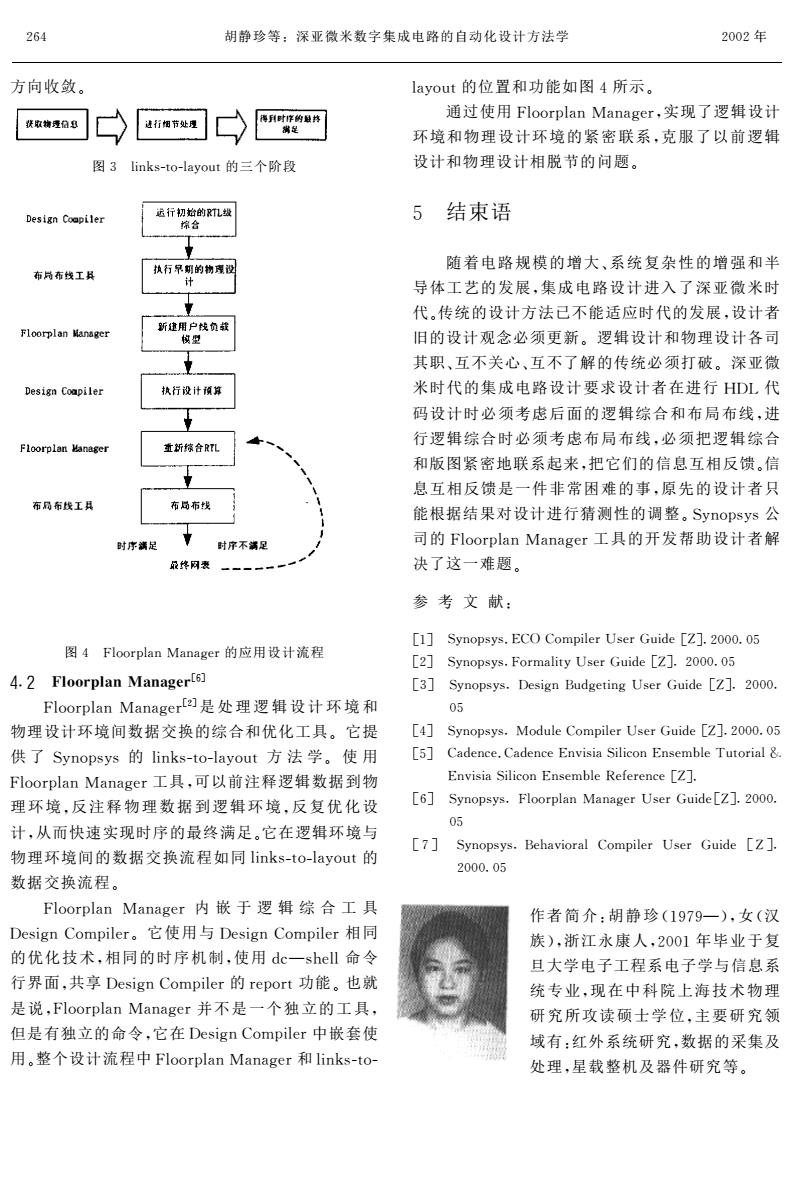

264 胡静珍等:深亚微米数字集成电路的自动化设计方法学 2002年 方向收敛。 layout的位置和功能如图4所示。 通过使用Floorplan Manager,实现了逻辑设计 铁收物理伯 选行烟节处理 海到时序的县势 满足 环境和物理设计环境的紧密联系,克服了以前逻辑 图3 links--to-layout的三个阶段 设计和物理设计相脱节的问题。 Design Compiler 运行初始的TL线 5 结束语 棕合 执行早期的物理没 随着电路规模的增大、系统复杂性的增强和半 布局布线工具 计 导体工艺的发展,集成电路设计进入了深亚微米时 代。传统的设计方法已不能适应时代的发展,设计者 下loorplan Manager 新建用户找负载 树型 旧的设计观念必须更新。逻辑设计和物理设计各司 其职、互不关心、互不了解的传统必须打破。深亚微 Design Coapiler 执行设计说算 米时代的集成电路设计要求设计者在进行HDL代 码设计时必须考虑后面的逻辑综合和布局布线,进 行逻辑综合时必须考虑布局布线,必须把逻辑综合 Floorplan Hanager 重新棕合RTL 和版图紧密地联系起来,把它们的信息互相反馈。信 息互相反馈是一件非常困难的事,原先的设计者只 布局布线工具 布局布找 能根据结果对设计进行猜测性的调整。Synopsys公 时序满足 时序不满足 司的Floorplan Manager工具的开发帮助设计者解 最终网表 决了这一难题。 参考文献: [1]Synopsys.ECO Compiler User Guide [Z].2000.05 图4 Floorplan Manager的应用设计流程 [2]Synopsys.Formality User Guide [Z].2000.05 4.2 Floorplan Managert6] [3]Synopsys.Design Budgeting User Guide [Z].2000. Floorplan Managert)是处理逻辑设计环境和 05 物理设计环境间数据交换的综合和优化工具。它提 [4] Synopsys.Module Compiler User Guide [Z].2000.05 供了Synopsys的links-to-layout方法学。使用 [5]Cadence.Cadence Envisia Silicon Ensemble Tutorial & Floorplan Manager工具,可以前注释逻辑数据到物 Envisia Silicon Ensemble Reference [Z]. 理环境,反注释物理数据到逻辑环境,反复优化设 [6] Synopsys.Floorplan Manager User Guide [Z].2000. 05 计,从而快速实现时序的最终满足。它在逻辑环境与 [7] Synopsys.Behavioral Compiler User Guide [Z]. 物理环境间的数据交换流程如同links-to-layout的 2000.05 数据交换流程。 Floorplan Manager内嵌于逻辑综合工具 作者简介:胡静珍(1979一),女(汉 Design Compiler。它使用与Design Compiler相同 族),浙江永康人,2001年毕业于复 的优化技术,相同的时序机制,使用dc一shell命令 旦大学电子工程系电子学与信息系 行界面,共享Design Compiler的report功能。也就 统专业,现在中科院上海技术物理 是说,Floorplan Manager并不是一个独立的工具, 研究所攻读硕士学位,主要研究领 但是有独立的命令,它在Design Compiler中嵌套使 域有:红外系统研究,数据的采集及 用。整个设计流程中Floorplan Manager和links--to- 处理,星载整机及器件研究等。方向收敛! 图 " #$%&’()*(#+,*-)的三个阶段 图 . /#**01#+%2+%+340的应用设计流程 567 89::;<9=>?=>=@A;BCD /#**01#+%2+%+340BED是 处 理 逻 辑 设 计 环 境 和 物理设计环境间数据交换的综合和优化工具!它提 供 了 F,%*1’,’的 #$%&’()*(#+,*-)方 法 学! 使 用 /#**01#+%2+%+340工具G可以前注释逻辑数据到物 理 环 境G反 注 释 物 理 数 据 到 逻 辑 环 境G反 复 优 化 设 计G从而快速实现时序的最终满足!它在逻辑环境与 物理环境间的数据交换流程如同 #$%&’()*(#+,*-)的 数据交换流程! /#**01#+% 2+%+340内 嵌 于 逻 辑 综 合 工 具 H4’$3%I*J1$#40!它使用与 H4’$3%I*J1$#40相同 的优化技术G相同的时序机制G使用 KLM’N4##命令 行界面G共享 H4’$3%I*J1$#40的 041*0)功能!也就 是说G/#**01#+%2+%+340并不是一个 独 立 的 工 具G 但是有独立的命令G它在 H4’$3%I*J1$#40中嵌套使 用!整个设计流程中 /#**01#+%2+%+340和 #$%&’()*( #+,*-)的位置和功能如图 .所示! 通过使用 /#**01#+%2+%+340G实现了逻辑设计 环境和物理设计环境的紧密联系G克服了以前逻辑 设计和物理设计相脱节的问题! O 结束语 随着电路规模的增大P系统复杂性的增强和半 导体工艺的发展G集成电路设计进入了深亚微米时 代!传统的设计方法已不能适应时代的发展G设计者 旧的设计观念必须更新!逻辑设计和物理设计各司 其职P互不关心P互不了解的传统必须打破!深亚微 米时代的集成电路设计要求设计者在进行 QHR代 码设计时必须考虑后面的逻辑综合和布局布线G进 行逻辑综合时必须考虑布局布线G必须把逻辑综合 和版图紧密地联系起来G把它们的信息互相反馈!信 息互相反馈是一件非常困难的事G原先的设计者只 能根据结果对设计进行猜测性的调整!F,%*1’,’公 司的 /#**01#+%2+%+340工具的开发帮助设计者解 决了这一难题! 参 考 文 献S BTD F,%*1’,’UVIWI*J1$#40X’40Y-$K4BZDUE[[[U[O BED F,%*1’,’U/*0J+#$),X’40Y-$K4BZDUE[[[U[O B"D F,%*1’,’UH4’$3%\-K34)$%3X’40Y-$K4BZDUE[[[U [O B.D F,%*1’,’U2*K-#4I*J1$#40X’40Y-$K4BZDUE[[[U[O BOD I+K4%L4UI+K4%L4V%]$’$+F$#$L*%V%’4J^#4_-)*0$+#‘ V%]$’$+F$#$L*%V%’4J^#4a4b404%L4BZDU BcD F,%*1’,’U/#**01#+%2+%+340X’40Y-$K4BZDUE[[[U [O BdD F,%*1’,’U\4N+]$*0+#I*J1$#40X’40Y-$K4 BZDU E[[[U[O 作者 简 介S胡 静 珍eTfdfghG女e汉 族hG浙江永康人GE[[T年毕业于复 旦大学电子工程系电子学与信息系 统专业G现在中科院上海技术 物 理 研究所攻读硕士学位G主要研 究 领 域有S红外系统研究G数据的采集及 处理G星载整机及器件研究等! Ec. 胡静珍等S深亚微米数字集成电路的自动化设计方法学 E[[E年