正在加载图片...

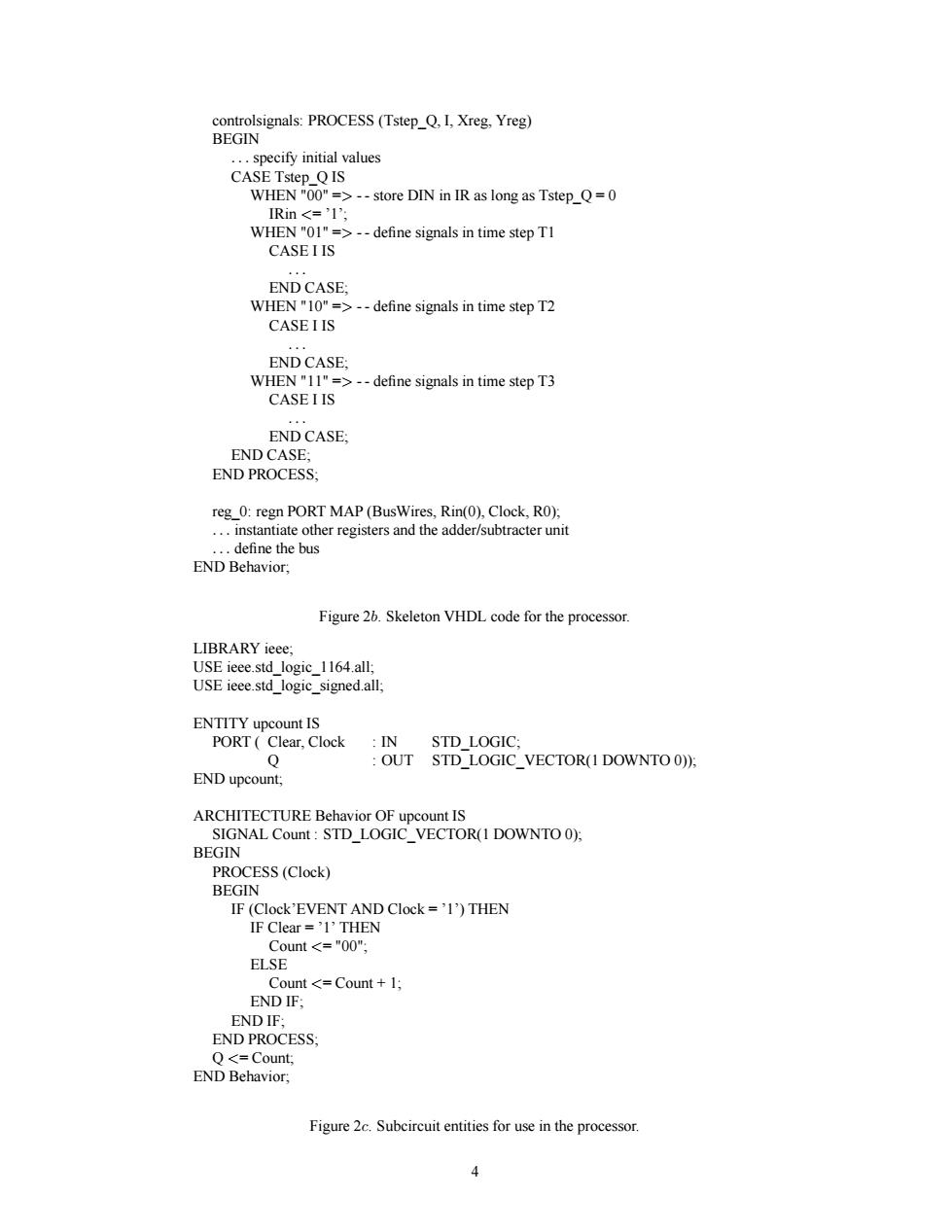

sPROCESS () pecify initial values CASE Tstep_QIS WHEN "00*- -store DIN in IR as long as Tstep_Q=0 WHEN -OI --define signals in time step TI cAsEus define signals in time stepT2 CASEIIS .CASE -define signals in time step T3 CASEIIS END CASE reg_0:regn PORT MAP(BusWires,Rin(0),Clock,RO), :define the buiser registers nd Figure 2b.Skeleton VHDL code for the processor. LIBRARY ieee; ENTITY upcount IS PORT(Clear,Clock IN STD_LOGIC OUT STD_LOGIC_VECTOR(I DOWNTO 0)): BEGNAL CoSTD LOGIC VECTORLI DONWNTOO ARCHITECTURE Behavior OF upcount IS IF (Clock'EVENT AND Clock='1')THEN Count <Count+1; END IF; Q=Count END Behavior; Figure 2c.Subcircuit entities for use in the processor.controlsignals: PROCESS (Tstep_Q, I, Xreg, Yreg) BEGIN ... specify initial values CASE Tstep_Q IS WHEN "00" => - - store DIN in IR as long as Tstep_Q = 0 IRin <= ’1’; WHEN "01" => - - define signals in time step T1 CASE I IS ... END CASE; WHEN "10" => - - define signals in time step T2 CASE I IS ... END CASE; WHEN "11" => - - define signals in time step T3 CASE I IS ... END CASE; END CASE; END PROCESS; reg_0: regn PORT MAP (BusWires, Rin(0), Clock, R0); ... instantiate other registers and the adder/subtracter unit ... define the bus END Behavior; Figure 2b. Skeleton VHDL code for the processor. LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_signed.all; ENTITY upcount IS PORT ( Clear, Clock : IN STD_LOGIC; Q : OUT STD_LOGIC_VECTOR(1 DOWNTO 0)); END upcount; ARCHITECTURE Behavior OF upcount IS SIGNAL Count : STD_LOGIC_VECTOR(1 DOWNTO 0); BEGIN PROCESS (Clock) BEGIN IF (Clock’EVENT AND Clock = ’1’) THEN IF Clear = ’1’ THEN Count <= "00"; ELSE Count <= Count + 1; END IF; END IF; END PROCESS; Q <= Count; END Behavior; Figure 2c. Subcircuit entities for use in the processor. 4