正在加载图片...

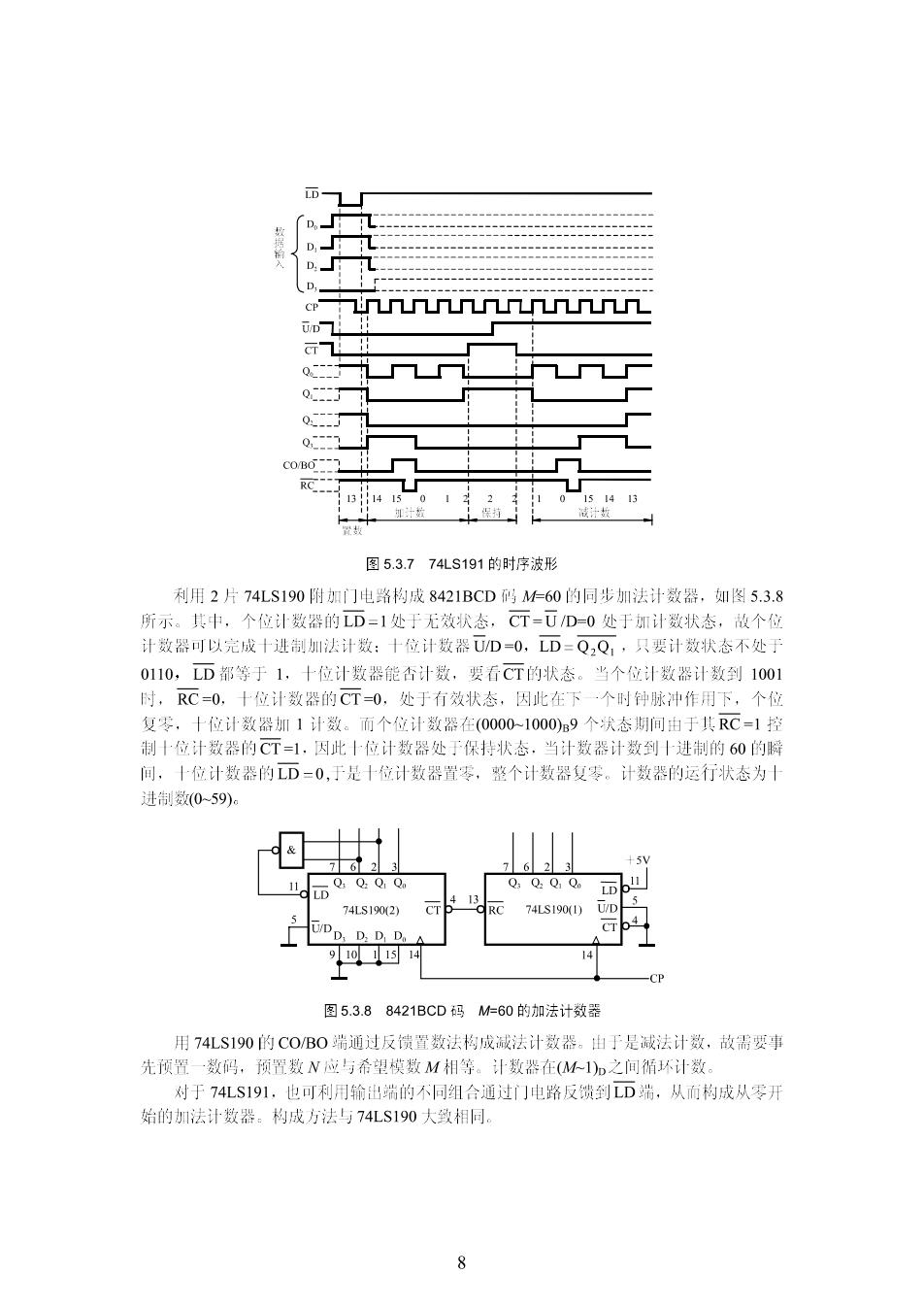

30B0.2 图5.3.774LS191的时序波形 利用2片74LS190附加门电路构成8421BCD码M=60的同步加法计数器,如图53.8 所示。其中,个位计数器的D=1处于无效状态,CT=UD-0处于加计数状态,放个位 计数器可以完成十进制加法计数:十位计数器ūD-0,D=Q,Q,,只要计数状态不处于 0110,D都等于1,十位计数器能否计数,要看CT的状态。当个位计数器计数到100 时,C=0.十位计数器的CT=0,处于有效状态,因此在下一个时钟脉冲作用下,个位 复零.十位计数器加1计数。而个位计数器在(O000-1000)9个天态期间由于其RC-1控 制十位计数器的CT=1,因此十位计数器处于保持状态,当计数器计数到十进制的60的瞬 间,十位计数器的LD=0,于是十位计数器置零,整个计数器复零。计数器的运行状态为 进制数(0-59) 74L51902 74Ls190D1 4 -CP 图5.3.88421BCD码M仁60的加法计效器 用74LS190的C0B0瑞通过反资置数法杉成或法计数器。由于是或法计数,故需要事 先顶置一数码,预置数N应与希望模数M相等。计数器在(M1)D之间循达计数。 对于74LS191,也可利用输出端的不同组合通过门电路反馈到D,从而构成从零开 始的加法计数器。构成方法与74LS190大纹相同 8