数字电子技术课程设计指导(ZSH.2015) 多功能数字钟电路设计 数字电路安装与调试技术 数字电路的安装与调试过程是检验、修正设计方案的实践过程,也是应用理论知识来 解决实践中各类问题的关键环节,是数字电路设计者必须掌握的基本技能。下面介绍数字 电路安装与调试中的一些常用方法。 1.集成电路器件的功能测试 在安装电路之前,对所选用的数字集成电路器件,应进行逻辑功能检测,以避免因器 件功能不正常而增加调试的困难。检测器件功能的方法是多种多样的,常用如下方法: (1)仪器检测法 用一些简单而实用的数字集成电路测试仪进行检测 (2)功能实验检查法 用实验电路进行逻辑功能测试。 (3)替代法 用被测器件替代正常工作的数字电路中的相同器件。 2.集成电路器件的接插和布线方法 数字电路的实验通常在面包板上进行,插接集成器件时,使器件的缺口端朝左方,先 对准插孔的位置,然后稍用力将其插牢,防止集成器件管脚弯曲或折断。 布线时应注意导线不宜太长,最好贴近底板并在集成器件的周围走线,切忌导线跨越 集成器件的上空,杂乱地在空中搭成网状。数字电路的布线应整齐美观,既可提高电路的 可靠性,又便于检查排除故障或更换器件。 导线的连接顺序是:先接固定电平端的连线,如电源的正极(一般用红色导线)、地线 (一般用黑色导线)、各MSI电路的使能端、门电路的多余输入端及电平固定的某些输入端 (如触发器的控制端K或J):然后按照电路中信号的流向顺序对所划分的子系统逐一布线、 调试:最后将各子系统连接起来。 3.数字电路的调试方法 数字电路的调试顺序也是先调试单元电路或子系统,然后逐渐扩大将几个单元电路进 行联调,最后进行整机调试。一般根据信号的流向逐级调试。由于数字电路系统中,相同 的单元电路和集成器件往往较多,为了尽快找出故障,常采用以下调试方法: (1)替代法

将已经调整好的单元电路代替有故障或有疑问的相同的单无电路,这样可以很快判 出故障原因是在单元电路本身,还是在其它的单元或连接线上。当发现某一局部电路有间 时,应先检查多部分的连线,当确认无误后再更换集成电路苏片: (2)对北法 将有问愿的电路的状态、参数与相同正常电路进行逐原对比。 (3)对分法 把有故的电路对分为两个部分,可检查出有问的一部分面除另一部分无放 的电路。然后样对有故降的部分进行对分检测,直到对分找出放障点为止。 实践表明,数字单元电路的故章大多都是接线错误或接触不良引起的,集成器件本身 的向题是较少的。然而设计者在调试中发现工作不正常时,往往·开始筑怀疑集成器件损 天,这是成该:音的 4.几种基本电路的测试方法 (集成逻辑门电 静态时,在各输入端分别接入不同的电平值,即逻辑“1”接高电平(输入瑞通过1k口 电阳接电源正极),逻辑“0”接低电平〔输入瑞接地).用数宁万用表消量各输出滞的逻辑 由平,并分析各罗细申平值是否将合由路的零辑关系。动本则月指名输入端分州接入里 定的脉冲信号,用示波器观测各输出瑞的信号并画出这些脉冲信号的时序波形关系图。 分析它们之间是否符合电路的逻辑关系 (2)集成触发器电路 静态时,主要测试钳发器的复位、置位、翻转功能。动态时,在时钟脉冲的作用下测 试触发器的计数功能,用示波器观测电路各处波形的变化情况,据此可以测定输出、输入 信号之间的分须关系,输出脉冲的上和下降时间,发灵敏度和抗干扰能力以及接入不 性质负我时 ,对输出波形参数的影响。测试时,蚀发冲的定度般要大于数微秒目 脉冲的上升沿或下降沿要陡。 (3)计效器电路 计数器电路的静态测试主要是测试电路的复位、置位功能及各MSI电路使能端的电平 是否正确。动杰武是出在过的脉冲作:用下刘开计数器久输出端的状态是否满足计数功倒 表的安求。可用示波器观测各输出端的波形、并记录这些波形与时钟脉冲之间的波形关系 (④译码显示电 首先式数码管冬笔段工作是雪正常,如共阴被的发光二战管:示器,可以将阴极接 地,耳将各笔段通过1k2电阻接电源正极+D:各笔段应亮。再将译码器的数据输入瑞依 次输入0001-1001,则显示器对应显示出19数字。 译码显示电路常见故路是: ①数码显示器上某宁总是“亮”而不“灭”。可能是译码器的输出幅度不正常或泽码 器的工作不正常。 ②数码显示器上某字总是不“亮”。可能是数码管或译码卷的连接不下确或接铂不良。 ③数码管学符显示模物.而且不随输入信号变化。可能是译码器的电源电压不正常或 连线不正确或接蚀不良。 2

门电路构成的时钟源 利用反相器或与非门可以构成时钟脉冲源,如图2.3.1所示。其中,图()为TTL门电 路构成的时钟源,晶体管T接成射极跟随器,可使箱出级与前级隔离,电位器电阻RP变化 几十千欧也不会影而电路的工作状态。因此,该电路具有输出须率范围宽、输出波形好、 带负裁能力强的优点。 电路的输出须率可由下式计算: =2(R+RP)C (2-3-60 式中,凡为门电路内部等效电丑,一殷为儿百攸姆。输出频率可从几赫兹至儿兆赫兹变化 改变电容C实现频率粗调,调节RP实现频幸细调。输出的矩形脉冲如图()所示。在要求 须率稳定性较高的情况下,如提供基准频率,则可采用图(b)所示电路,输出须率由品罪 的率决定。 iT 337 =1.I7(R,-RPIC 000- 74LS04 图23.1门电路构成的时钟源及其波形 a)Tm门生路构成酷k时源o门电路均发的器么张落声@)CMOs门电路鸡最的味时封学 图()为CMOS门电路构成的简易时钟源.由于门电路的输入阻抗很高,定时电容C 的值不是很大减能获得较大的时间常数,尤其适于对频率准确性要求不太高的低颇时钟源 (小于10OkHz)。常取补偿电阻R,>RG定时电阻),即R,=10R。翰出频率 f=7=2.2R,C (2-3-7)

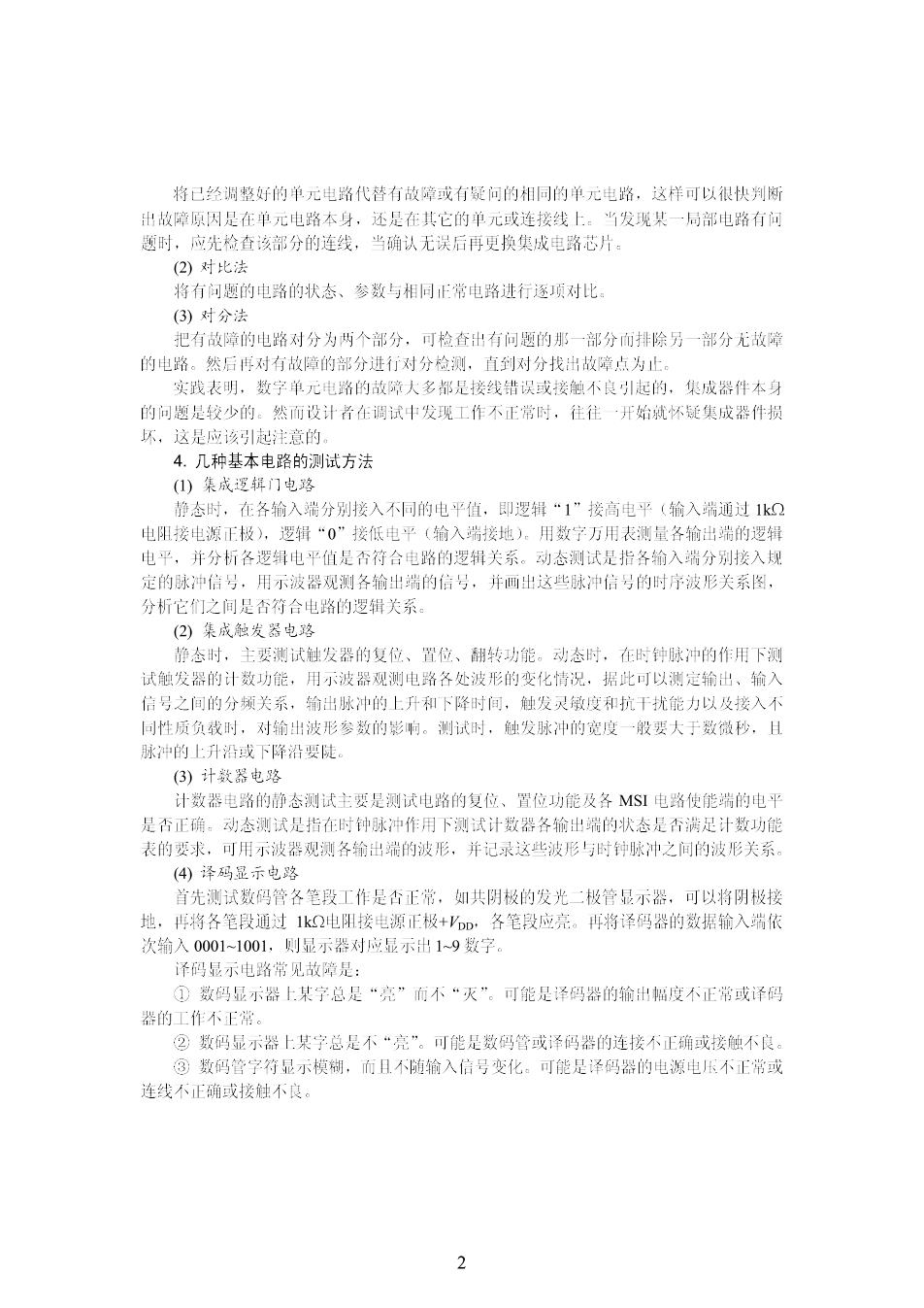

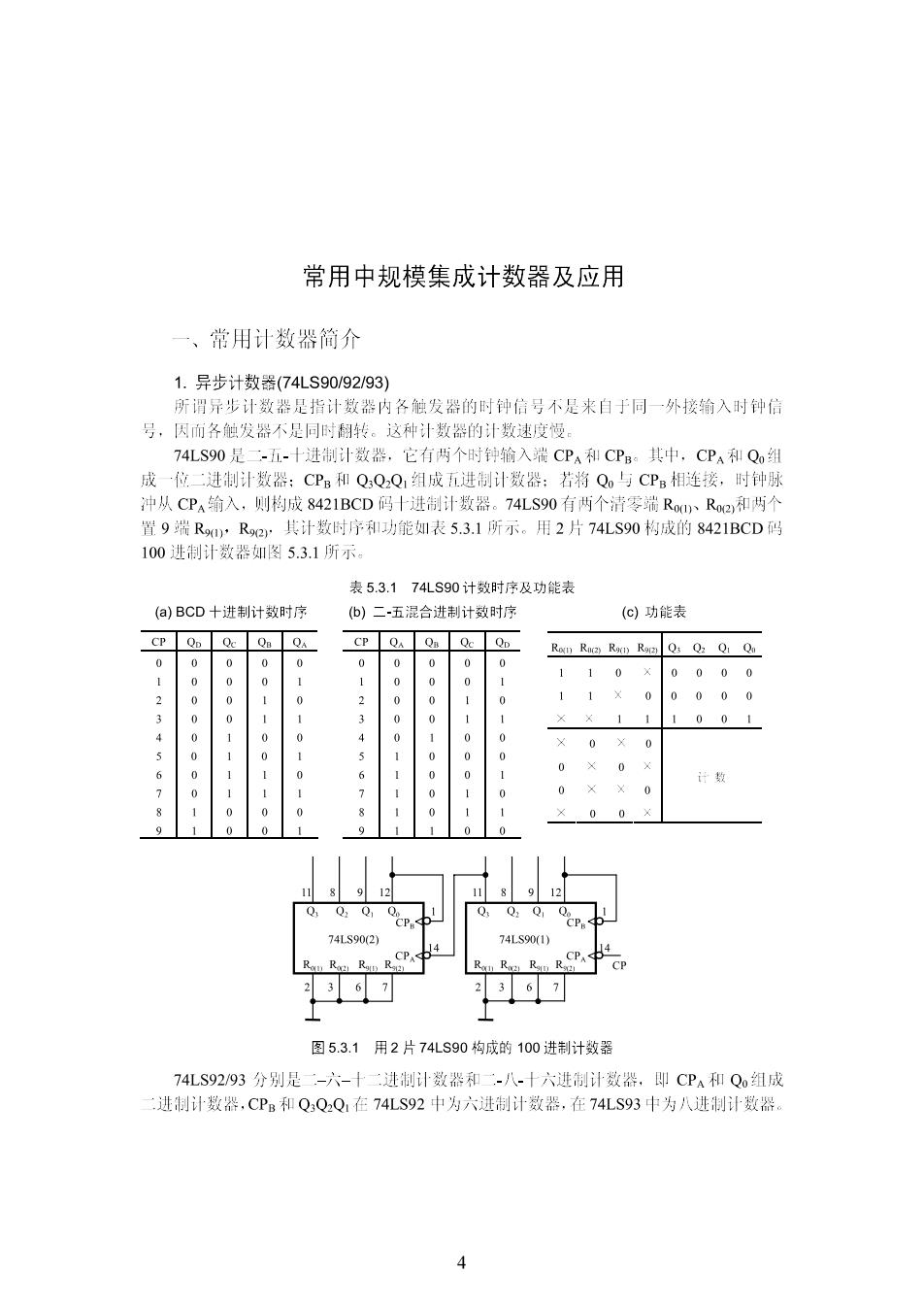

常用中规模集成计数器及应用 一、常用计数器简介 1.异步计数器(74LS90/92/93) 异步计数器是指计数器内各发器的时钟信号不是来于同一外接箱入时钟信 号,因而各触发器不是同时转。这种计数器的计数速度漫: 74LS90是二-五-十进制计数器,它有两个时钟喻入端CPa和CPa。其中,CPA和Q组 成一位进制计数器:CPa和Q:Q2Q,组成进制计数器:若将Q。与CP。相连接,时钟脉 冲从CP第入.则构城8421BCD码十进制计数器。74LS90有两个清零端R、R2和两个 置9端R:R0其计数时序和功能如表531所示。用2片74LS90构成的8421BCD码 100进期数器如图5.3.1所示 表5.3.174S90计数时序及功能表 (a)BCD十进制计数时序 b)二-五混合进制计致时序 (@)功能表 Ro R Ro Ro O:0:00 000 0001 11001 0×0 0×0 计数 ×X0 00× 0 361 2367 图5,3.1用2片74LS90构成的100进制计数器 74红S9293分品-六-+·计利数塞和“.八.十六井补数器,即CP、印O。组成 进制计数器,CPa和Q,QQ仁74LS92中为六进制计数器,在74LS93中为八进制计数器

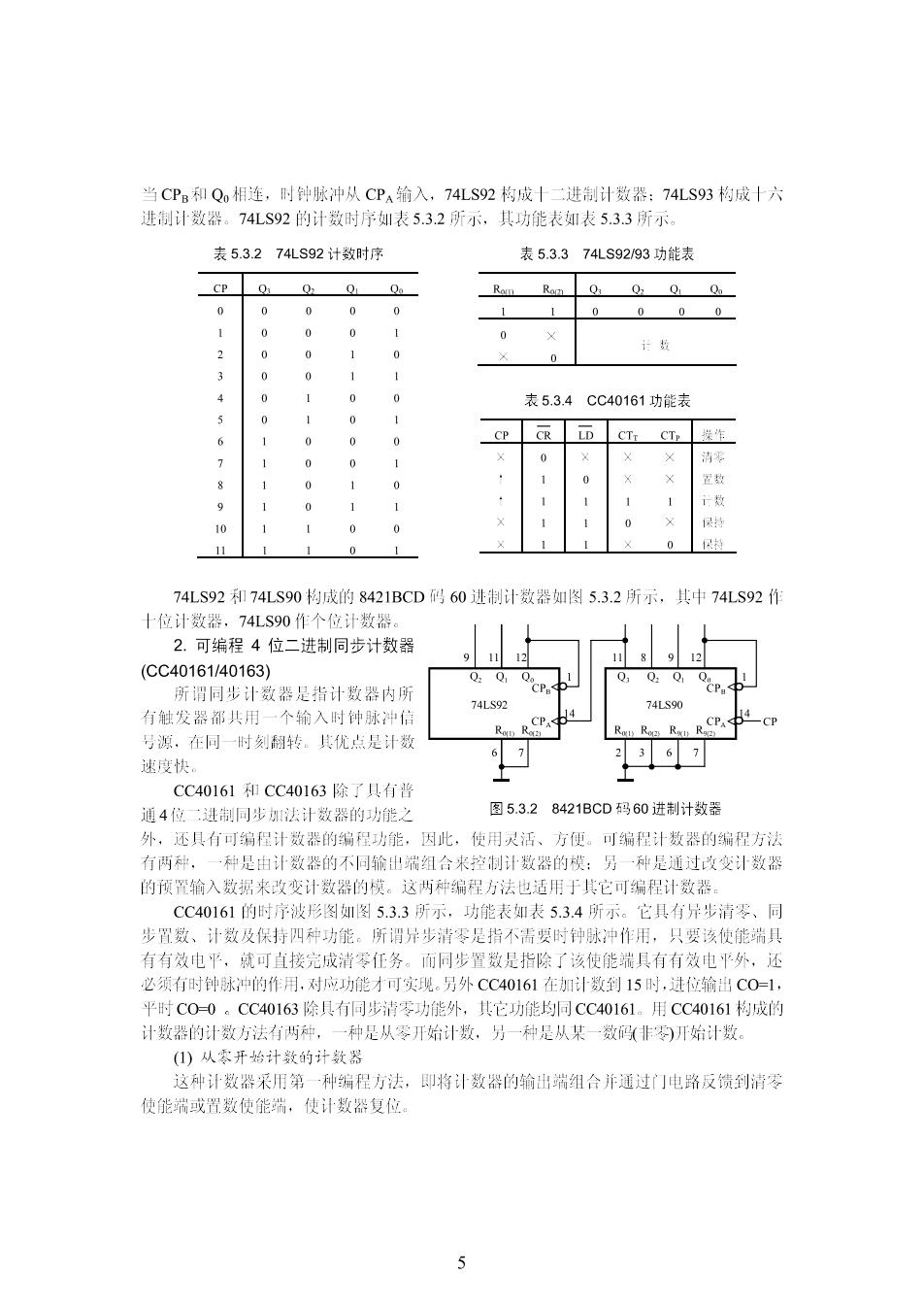

当CPa和Q相连,时钟脉冲从CPa输入,74LS2构成十二进制计数器:74LS3构成十六 进制计效器 74LS92的计致时序如表5.32所示,其功能表知表5.33所示 表5.3274L92计数时序 表5.3374Ls92/93功能表 CP 0.02010 0 0 000 0 0 234567 0 表5.3.4CC40161功能表 0 0 0 0 8。 置 , 1 0 特 74LS92和74LS90构成的8421BCD码60进制计数器如图5.3.2所示,其中74LS92 十位计数器,74LS90作个位计数器。 2.可编程4位二进制同步计数器 8g1 (CC40161/40163) 所调同步计数器是指计数器内月 有发器部其用 入时钟 4Ls92 4Ls90 与源,在同一时翻转。优点是计数 速度快。 367 CC40161和CC40163除了具有普 酒4位补同步上计数界的力能之 图5.3.28421BCD码60进制计数器 外,还具有可编程计数器的编程功能,因此 使用灵活、方便。可编程计数器的编程方法 有两种 种是由计数器的不同输出端组合来控制计数器的模:另一种是通过改变计数器 的顶置输入数据来改变计数器的模。这两种编程方法也适用于其它可编程计数器 CC40161的时序被形图知图5.3.3所示,功能表如表5.3.4所示。它具有异步清零、同 步置数、计数及保持四种功能。所谓异步洁零是指不需要时钟脉冲作用,只要该使能瑞具 有有效电平,就可直接完成清零任务。而同步置数是指除了该使能端具有有效电平外,还 必须有时钟脉冲的作用.对应功能才可实现.另外CC40161在加计数到15时,进位输出C0- 平时C00。CC40163除具有同步清零功能外,其它功能均同CC40161。用CC40161构成的 计数器的计数方法有两种,一种是从零开始计数,另一种是从某一数吗(非约开始计数。 (①)从零开始计数的计数器 这种计数器采用第种编程方法,即将计数器的输出端组合并通过门电路反到清罗 使能端或置数使能端,使计数器复位 5

-= 0.0.0 cC40161 D.D, 计 图5.33CC40161/163的时序泼形图 图5.3.4CC40161构成的十进制计数器 用一片CC40161附门电路可构成8421BCD码十进制计数器,如图5.3.4所示。它是 利用同步置数功能实现BCD码计数的,当计数器计数到1001时,D=Q,Q。=0,在第 CC40161E cc401610) (b) 图5.3.58421BCD码60进制计数器 创华行进散方式领联间并行进位方式减歌

十个CP脉冲作用下计数器置零,之后D=1,计数器又开始计数 若将图5.34电路中与非]的两输入端改接到Q2、Q,即D=Q,Q。,则可构成 8421BCD码的六进制计致器。将六进计数器和十进制计数器级联,可构成8421BCD码 60进制计数器,如图5.3.5b)所示。计数器在(0-59之间环计数。 从非零致码开始的计器 这种计数器采用的是第二种编程方法。它是利用进位输出瑞C0和置数使能瑞LD杨成 由预置数来决定计数器的模。预置数N与计数器模效M之间的关系为N=Mx一M式中, M是计数器的最人模数。计数器在N马与最大计数值(得计数器给出为全1状态)之间循环 计致,共有M个状态。用这种计数器构成分须器最方使,只要改变预置输入数据即可改变 分数,从而构成任意分须器 用2片CC40161 附加门电路构成一个60分频器,顶置数 N=100000000-00111100=11000100,其中,1100是高位CC40161的顶置数,0100是低位 CC40161的顶置数,电路如图5.3.6所示。计数器在(C4FF)H之间循环计数,在L端输出 个60分蜘的脉冲信号。改变疾置输入数据即可在L端得到不同分频数的脉冲信号。 CC401612) C401611) 图5.3.6用CC40161构成60分频器 3.加减同步计数器(74LS190/191/192/193) (1)单时钟(74LS190/74LS191) 表5.3.574s190/191功能表 74LS190和74LS191是单时钟4位同步加/减可逆 计数器 其中74LS190为8421BCD码十进制计数器 74LS191是BCD码十六进制计数器,两者的引购排列 00 图和引脚功能完全一样,如表5.3.5所示。74LS191的 时序波形如图537所示 需要指出的是正耿冲输出COBO及负脉冲喻 端C,两者在加计数到歧大计数值时或减计数到 零时,都发出脉冲信号:不同之处是 COB0端发出个与输入时钟周期相等且同步的下脉冲,C端发出一个与输入时钟信号 低电平时间相等日同步的负脉冲。 74LS190一般用于构成BCD码十进制计数器,而74LS191通过编程可构成任意进制计 数器

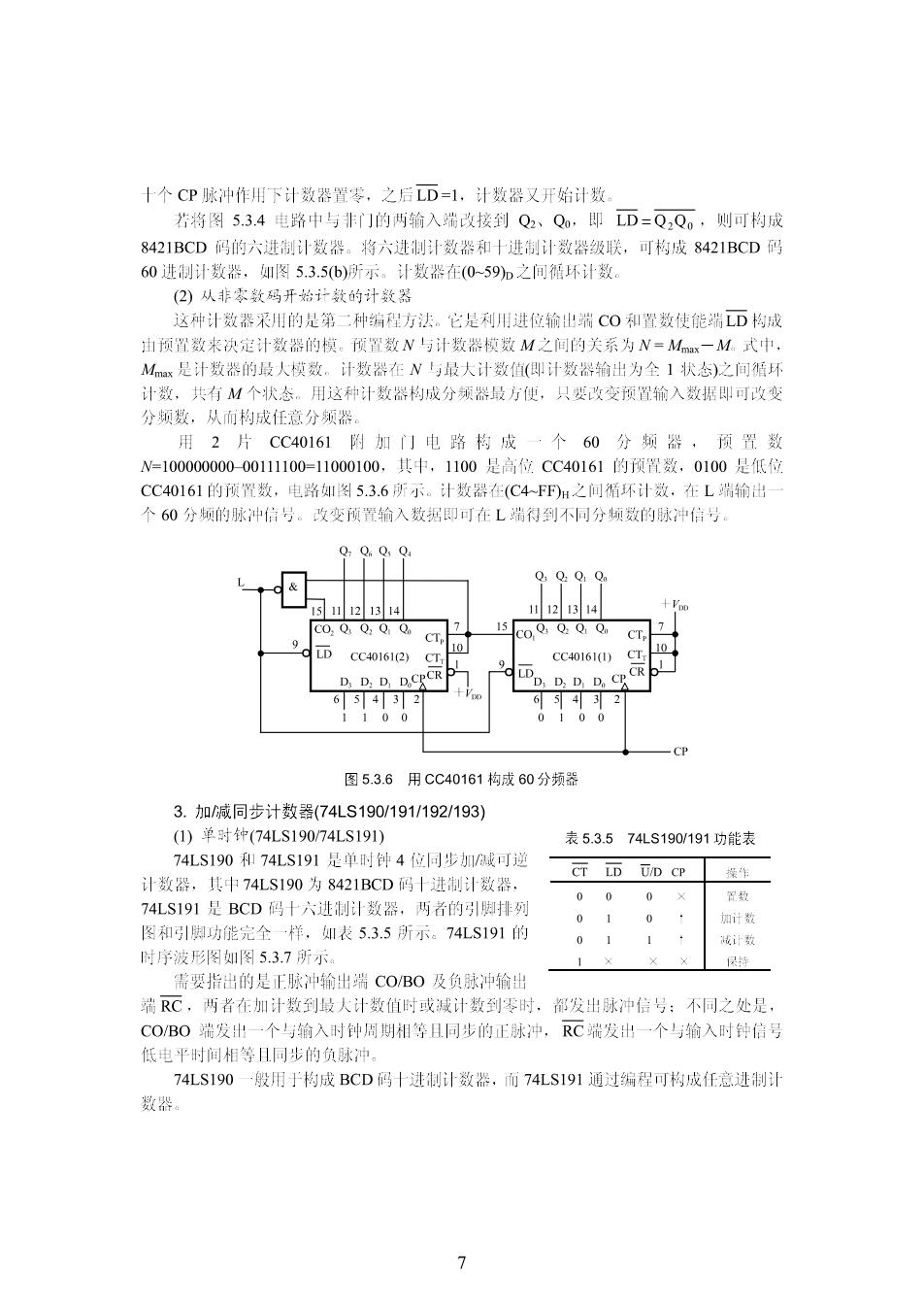

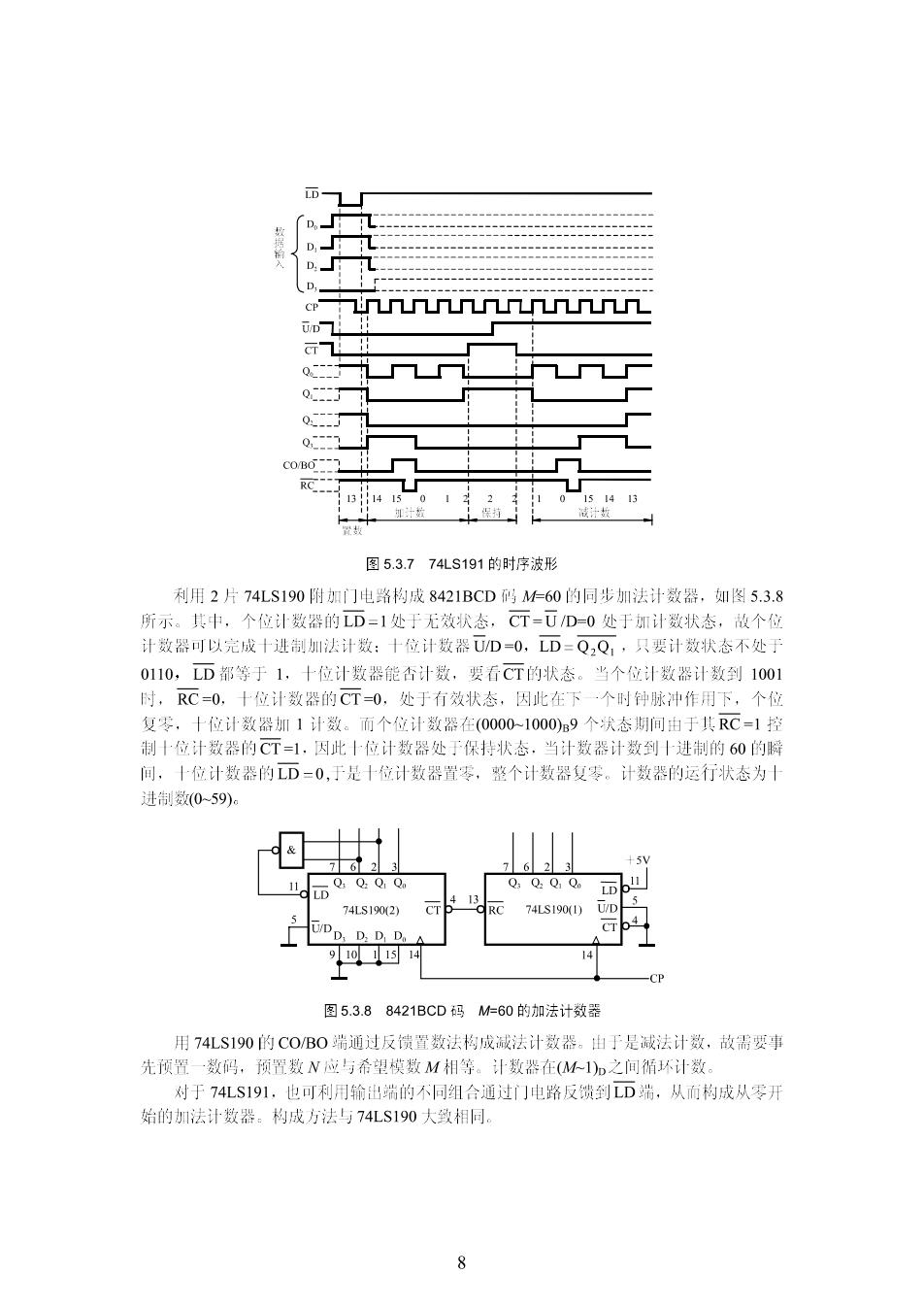

30B0.2 图5.3.774LS191的时序波形 利用2片74LS190附加门电路构成8421BCD码M=60的同步加法计数器,如图53.8 所示。其中,个位计数器的D=1处于无效状态,CT=UD-0处于加计数状态,放个位 计数器可以完成十进制加法计数:十位计数器ūD-0,D=Q,Q,,只要计数状态不处于 0110,D都等于1,十位计数器能否计数,要看CT的状态。当个位计数器计数到100 时,C=0.十位计数器的CT=0,处于有效状态,因此在下一个时钟脉冲作用下,个位 复零.十位计数器加1计数。而个位计数器在(O000-1000)9个天态期间由于其RC-1控 制十位计数器的CT=1,因此十位计数器处于保持状态,当计数器计数到十进制的60的瞬 间,十位计数器的LD=0,于是十位计数器置零,整个计数器复零。计数器的运行状态为 进制数(0-59) 74L51902 74Ls190D1 4 -CP 图5.3.88421BCD码M仁60的加法计效器 用74LS190的C0B0瑞通过反资置数法杉成或法计数器。由于是或法计数,故需要事 先顶置一数码,预置数N应与希望模数M相等。计数器在(M1)D之间循达计数。 对于74LS191,也可利用输出端的不同组合通过门电路反馈到D,从而构成从零开 始的加法计数器。构成方法与74LS190大纹相同 8

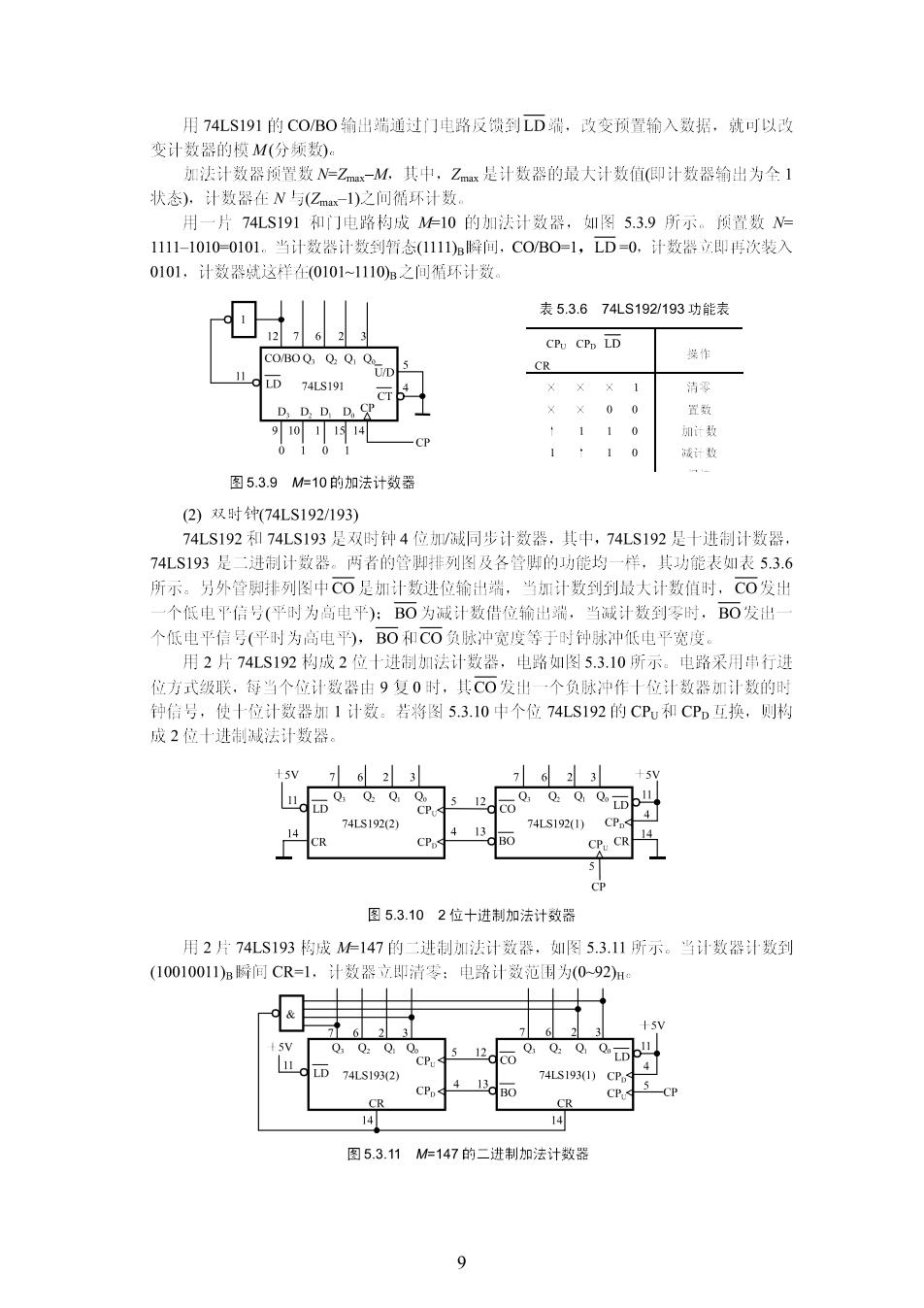

用74LS191的C0B0输出端通过门电路反馈到D汽,改变预置输入数据,就可以改 变计数器的模M(分须数): 加法计数器预置数N乙-M,其中,乙m是计数器的最大计数值(卿计数器输出为全1 状态).计数器在N与(亿一)之间循环计数。 用一片74LS191和门电路构成F10的加法计数器,如图5.3.9所示。慎置数N 1111-10100101当计数器计数到暂态1111)瞬间,C0B0-1,D-0,计数器立即样次装入 0101,计数器减这样存(01011110之间循环计效 表5.3.674LS192/193功能表 损作 CR 74S191 4 XX X 清 D ××00 置 C 110 1 10 图5.3.9M10的加法计数器 (2)双时钟(74LS192/193) 74LS192和74LS193是双时钟4位加/减同步计数器,其中,74LS192是十进制计数器 74LS13是二进制计数器 两者的管脚非列图及各管脾的功能均 ¥,其功能表如表53.6 所示。另外管脚挂列图中C0是加计数进位输出端,当加计数到到最人计数值时,CO发出 一个低电平信号(平时为高电平):BO为减计数借位输瑞,当减计数到零时,Bō发出 个低电平信号(平时为高电門),B0和C而负脉冲宽度等于时钟脉冲低电平宽 用2片74LS192构成2位十进制加法计数器 电路如图53.10所示。 电路采用串行进 位方式级联,每当个位计数器由9复0时,其C0发出一个负脉冲作十位计数器加计数的 钟信号,使十位计数器1计数。若将图5.3.10中个位74LS192的CPu和CPD互换,构 成2位十让生制设法计凝器 74L51922 国53.102位十进制加法计致器 用2片74LS193构成147的二进制加法计效器,如图5.3.11所示。当计数器计数到 (10010011)B间CR=1, 计数器立即清专:电路计数范围为(0-92州 4L51932) Ls193)9 14 图5.3.11147的二进制加法计数器

二、“12翻1”小时计数器设计 (①)列计数器状态转换表或画时序波形图 “12甜1”小时计数器是核“01一0203一…一11一120102…”规律计数的。计 数器的计数软态转换表,如表53.11所示。其中,Q。为小时计数器10位的最低 表5.3.11“12翻1”小时计数时序 CP CP 0 700111 (2)选择触发器和计效 十数器 制同步可逆计数器74 S19构成,十位计数器由双D触发器 74LS74构成,将它们级联组成“12陆1”小时计数器。 (3)求复位信号:置位信号 由表5.3.11可知,计数器的状态要发生两次跳越:一是计数器计致到9,即个位计数器 的状态为QoQ2Q1Qm=1001后,在下一计数脉冲作用下计数器进入暂态1010.利用暂态 的5个1即O 个位异步置0,同时向十位计数器进位使Q1: 数器计到12 后,在第1B个计数脉冲作用下个位计数器的状态应为-001, 十位计数器的 Q100:第二次跳越的十位清“0”和个位置“1”信号可由暂念为“1”的输出端Q0,Q1, Q0来产生。由上述分析得74LS191的控制方程式: 置数端 LD=Qo;Qo (5-31) 圳y减控制端 U/D=Q10Qo (5-3-2) D触发器74LS74的清“0”岩 1RD-Q1 oQarQoo-U/D·Q0 (5-3-3) 其中,式(5-31)的作用是完成个位计数器第一次置“0”:式(5-3-2)的作用是在计数器计到12 时改变74LS191的加减控淘模式,使其由原来的加法计数变为减法计数,当第13个脉冲 米到时,个位计数器减1:式(5-3-3)性1位计数器清“0”,使计数器的状态变为Q。=0, QoQQoQ=0001 (4)根据控制方程式画计数器的逻辑电路图 由以上设计得到的“12翻1”小时计数器的逻辑图如图5.3.18所示。由CC40161构成 的“12樹1”小时计数器电路如图5.3.19可示