正在加载图片...

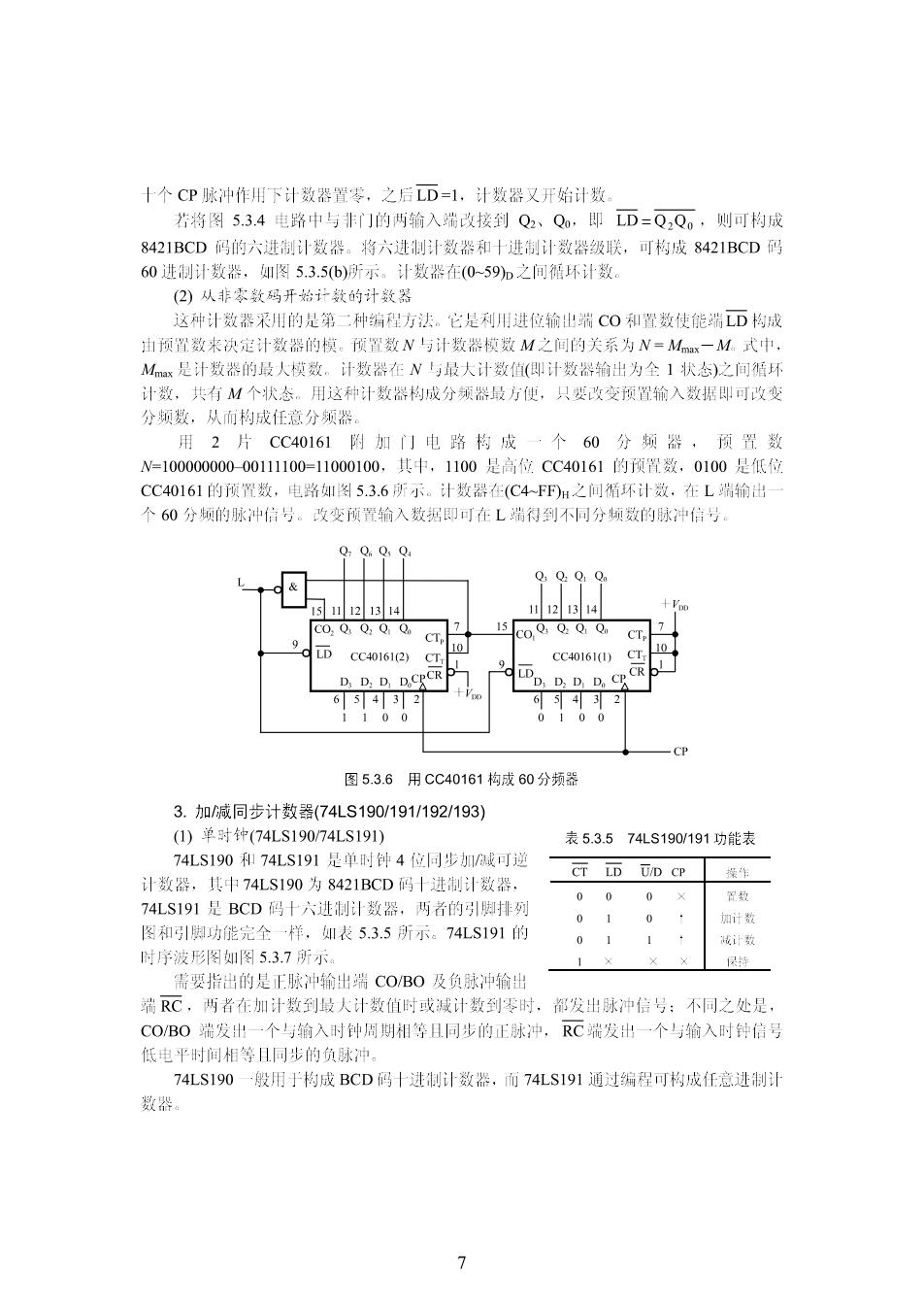

十个CP脉冲作用下计数器置零,之后D=1,计数器又开始计数 若将图5.34电路中与非]的两输入端改接到Q2、Q,即D=Q,Q。,则可构成 8421BCD码的六进制计致器。将六进计数器和十进制计数器级联,可构成8421BCD码 60进制计数器,如图5.3.5b)所示。计数器在(0-59之间环计数。 从非零致码开始的计器 这种计数器采用的是第二种编程方法。它是利用进位输出瑞C0和置数使能瑞LD杨成 由预置数来决定计数器的模。预置数N与计数器模效M之间的关系为N=Mx一M式中, M是计数器的最人模数。计数器在N马与最大计数值(得计数器给出为全1状态)之间循环 计致,共有M个状态。用这种计数器构成分须器最方使,只要改变预置输入数据即可改变 分数,从而构成任意分须器 用2片CC40161 附加门电路构成一个60分频器,顶置数 N=100000000-00111100=11000100,其中,1100是高位CC40161的顶置数,0100是低位 CC40161的顶置数,电路如图5.3.6所示。计数器在(C4FF)H之间循环计数,在L端输出 个60分蜘的脉冲信号。改变疾置输入数据即可在L端得到不同分频数的脉冲信号。 CC401612) C401611) 图5.3.6用CC40161构成60分频器 3.加减同步计数器(74LS190/191/192/193) (1)单时钟(74LS190/74LS191) 表5.3.574s190/191功能表 74LS190和74LS191是单时钟4位同步加/减可逆 计数器 其中74LS190为8421BCD码十进制计数器 74LS191是BCD码十六进制计数器,两者的引购排列 00 图和引脚功能完全一样,如表5.3.5所示。74LS191的 时序波形如图537所示 需要指出的是正耿冲输出COBO及负脉冲喻 端C,两者在加计数到歧大计数值时或减计数到 零时,都发出脉冲信号:不同之处是 COB0端发出个与输入时钟周期相等且同步的下脉冲,C端发出一个与输入时钟信号 低电平时间相等日同步的负脉冲。 74LS190一般用于构成BCD码十进制计数器,而74LS191通过编程可构成任意进制计 数器