正在加载图片...

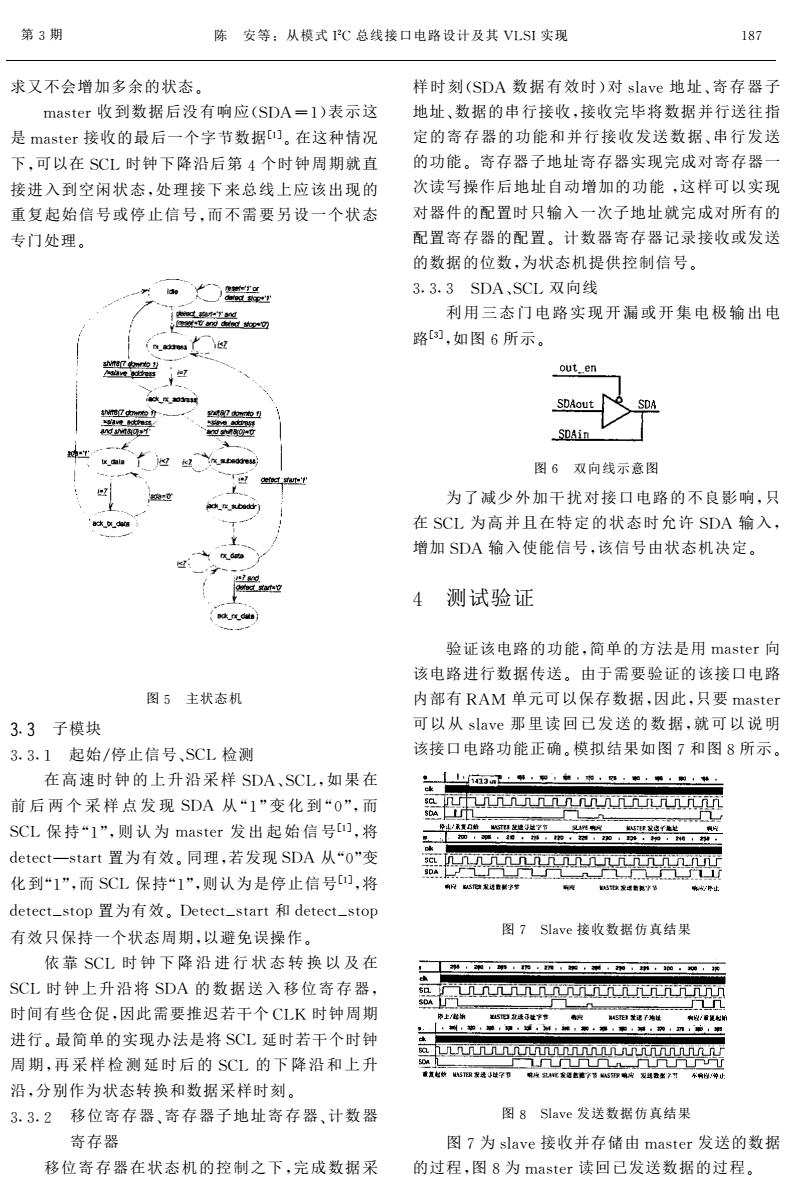

第3期 陈安等:从模式1C总线接口电路设计及其VISI实现 187 求又不会增加多余的状态。 样时刻(SDA数据有效时)对slave地址、寄存器子 master收到数据后没有响应(SDA=I)表示这 地址、数据的串行接收,接收完毕将数据并行送往指 是master接收的最后一个字节数据)。在这种情况 定的寄存器的功能和并行接收发送数据、串行发送 下,可以在SCL时钟下降沿后第4个时钟周期就直 的功能。寄存器子地址寄存器实现完成对寄存器一 接进入到空闲状态,处理接下来总线上应该出现的 次读写操作后地址自动增加的功能,这样可以实现 重复起始信号或停止信号,而不需要另设一个状态 对器件的配置时只输入一次子地址就完成对所有的 专门处理。 配置寄存器的配置。计数器寄存器记录接收或发送 的数据的位数,为状态机提供控制信号。 3.3.3SDA、SCL双向线 icod geond 利用三态门电路实现开漏或开集电极输出电 2t6n0ce过边 路[),如图6所示。 h的配安w也型 t短 outen SDAout SDA 辽介 SDAin 图6双向线示意图 为了减少外加干扰对接口电路的不良影响,只 在SCL为高并且在特定的状态时允许SDA输入, 增加SDA输入使能信号,该信号由状态机决定。 4测试验证 验证该电路的功能,简单的方法是用master向 该电路进行数据传送。由于需要验证的该接口电路 图5主状态机 内部有RAM单元可以保存数据,因此,只要master 3.3子模块 可以从slave那里读回已发送的数据,就可以说明 3.3.1起始/停止信号、SCL检测 该接口电路功能正确。模拟结果如图7和图8所示。 在高速时钟的上升沿采样SDA、SCL,如果在 前后两个采样点发现SDA从“1”变化到“0”,而 SCL保持“1”,则认为master发出起始信号们,将 经承复日静T和业进子世字官 detect-一start置为有效。同理,若发现SDA从“o”变 nnnn元nij 化到“1”,而SCL保持“1”,则认为是停止信号山,将 地发进售包序书 detect_stop置为有效。Detect-.start和detect_.stop 有效只保持一个状态周期,以避免误操作。 图7 Slave接收数据仿真结果 依靠SCL时钟下降沿进行状态转换以及在 ··第·的·m,年,·阳·,举 SCL时钟上升沿将SDA的数据送入移位寄存器, unnnnnnnnnnn 时间有些仓促,因此需要推迟若干个CLK时钟周期 具几 师上/出嫩 心回和进子生平节款5装这墙址南以:量便财的 进行。最简单的实现办法是将SCL延时若干个时钟 物第,果·,带·型:准:瑞n的 aLUnLuuuiuUuUUurUi 周期,再采样检测延时后的SCL的下降沿和上升 L拉 :5因架绿世子节明片氧爱直宽不装5西确牌双线数堂子T本响:钟止 沿,分别作为状态转换和数据采样时刻。 3.3.2移位寄存器、寄存器子地址寄存器、计数器 图8 Slave发送数据仿真结果 寄存器 图7为slave接收并存储由master发送的数据 移位寄存器在状态机的控制之下,完成数据采 的过程,图8为master读回已发送数据的过程。求又不会增加多余的状态! "#$%&’收到数据后没有响应()*+,-.表示这 是 "#$%&’接收的最后一个字节数据/-0!在这种情况 下1可以在 )23时钟下降沿后第 4个时钟周期就直 接进入到空闲状态1处理接下来总线上应该出现的 重复起始信号或停止信号1而不需要另设一个状态 专门处理! 图 5 主状态机 676 子模块 8787- 起始9停止信号:)23检测 在 高 速 时 钟 的 上 升 沿 采 样 )*+:)231如 果 在 前 后 两 个 采 样 点 发 现 )*+ 从 ;-<变 化 到 ;=<1而 )23保 持;-<1则 认 为 "#$%&’发 出 起 始 信 号/-01将 >&%&?%@$%#’%置为有效!同理1若发现 )*+从;=<变 化 到;-<1而 )23保持;-<1则认为是停止信号/-01将 >&%&?%A$%BC置为有效!*&%&?%A $%#’%和 >&%&?%A $%BC 有效只保持一个状态周期1以避免误操作! 依 靠 )23时 钟 下 降 沿 进 行 状 态 转 换 以 及 在 )23时 钟 上 升 沿 将 )*+ 的 数 据 送 入 移 位 寄 存 器1 时间有些仓促1因此需要推迟若干个 23D时钟周期 进行!最简单的实现办法是将 )23延时若干个时钟 周 期1再 采 样 检 测 延 时 后 的 )23的 下 降 沿 和 上 升 沿1分别作为状态转换和数据采样时刻! 8787E 移位寄存器:寄存器子地址寄存器:计数器 寄存器 移位寄存器在状态机的控制之下1完成数据采 样 时刻()*+数据有效时.对 $F#G&地址:寄存器子 地址:数据的串行接收1接收完毕将数据并行送往指 定的寄存器的功能和并行接收发送数据:串行发送 的功能!寄存器子地址寄存器实现完成对寄存器一 次读写操作后地址自动增加的功能 1这样可以实现 对器件的配置时只输入一次子地址就完成对所有的 配置寄存器的配置!计数器寄存器记录接收或发送 的数据的位数1为状态机提供控制信号! 87878 )*+:)23双向线 利 用 三 态 门 电 路 实 现 开 漏 或 开 集 电 极 输 出 电 路/801如图 H所示! 图 H 双向线示意图 为了减少外加干扰对接口电路的不良影响1只 在 )23为高并且在特定的状态时允许 )*+输入1 增加 )*+输入使能信号1该信号由状态机决定! 4 测试验证 验证该电路的功能1简单的方法是用 "#$%&’向 该电路进行数据传送!由于需要验证的该接口电路 内部有 I+J 单元可以保存数据1因此1只要 "#$%&’ 可 以 从 $F#G&那 里 读 回 已 发 送 的 数 据1就 可 以 说 明 该接口电路功能正确!模拟结果如图 K和图 L所示! 图 K )F#G&接收数据仿真结果 图 L )F#G&发送数据仿真结果 图 K为 $F#G&接收并存储由 "#$%&’发送的数据 的过程1图 L为 "#$%&’读回已发送数据的过程! 第 8期 陈 安等M从模式 N E 2总线接口电路设计及其 O3)N实现 -LK