正在加载图片...

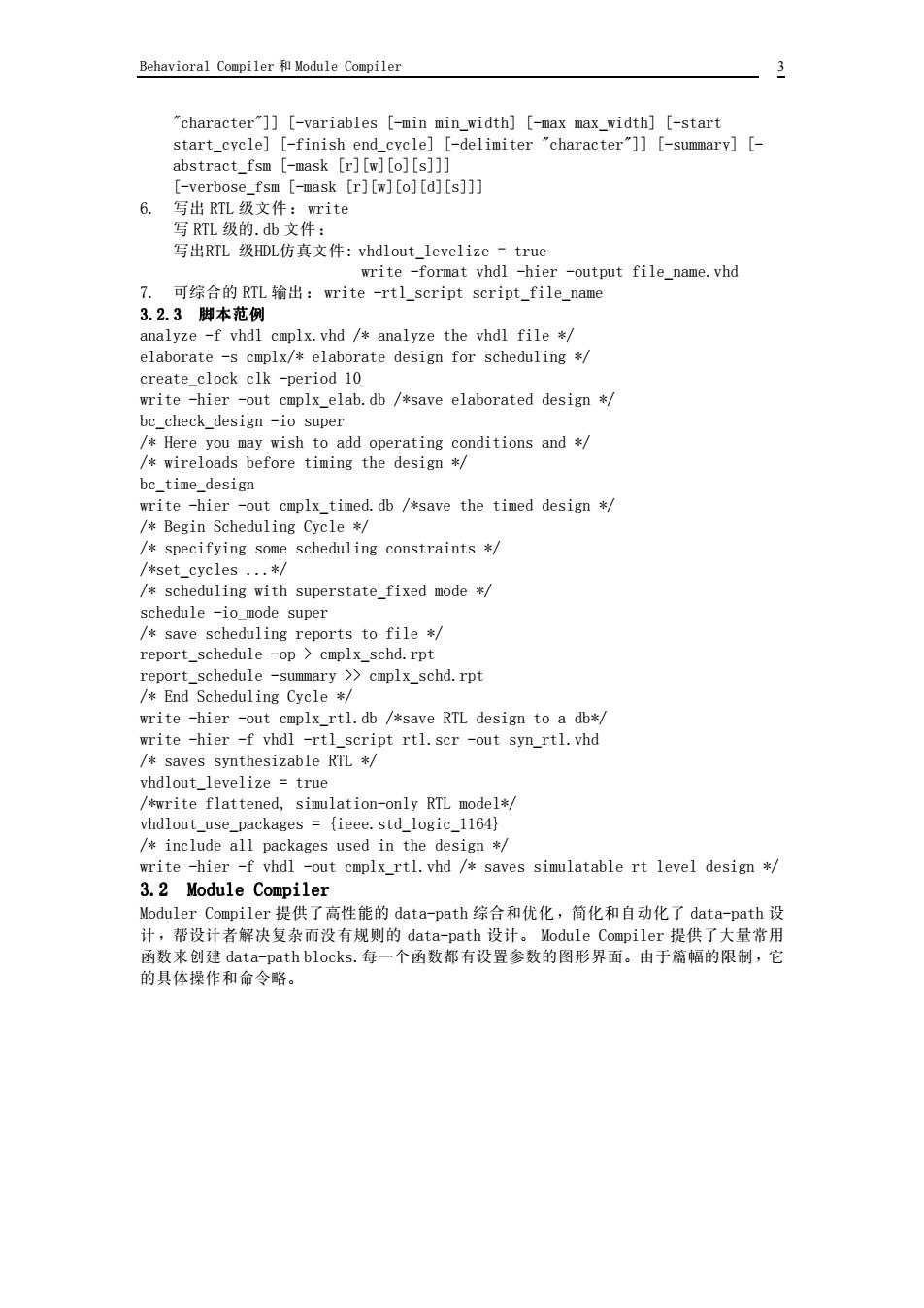

Behavioral Compiler Module Compiler 3 "character"]][-variables [-min min_width][-max max_width][-start start_cycle][-finish end_cycle][-delimiter "character"]][-summary][ abstract_fsm [-mask [r][w][o][s]]] [-verbose_fsm [-mask [r][w][o][d][s]]] 6.写出RTL级文件:rite 写RTL级的.db文件: 写出RTL级HDL仿真文件:vhdlout._levelize=true write -format vhdl -hier -output file name.vhd 7.可综合的RTL输出:write-rtl_script script._file_name 3.2.3脚本范例 analyze -f vhdl cmplx.vhd /analyze the vhdl file * elaborate -s cmplx/*elaborate design for scheduling * create_clock clk -period 10 write -hier -out cmplx_elab.db /*save elaborated design * bc check_design -io super /Here you may wish to add operating conditions and * /wireloads before timing the design * bc time design write -hier -out cmplx_timed.db /*save the timed design * /Begin Scheduling Cycle * /specifying some scheduling constraints * /*set_cycles ...* /scheduling with superstate_fixed mode * schedule -io_mode super /save scheduling reports to file * report schedule -op cmplx schd.rpt report_schedule -summary >>cmplx_schd.rpt /End Scheduling Cycle * write -hier -out cmplx_rtl.db /*save RTL design to a db*/ write -hier -f vhdl -rtl_script rtl.ser -out syn_rtl.vhd /saves synthesizable RTL * vhdlout_levelize =true /*write flattened,simulation-only RTL model*/ vhdlout_use_packages {ieee.std_logic_1164} /include all packages used in the design * write -hier -f vhdl -out cmplx_rtl.vhd /saves simulatable rt level design * 3.2 Module Compiler Moduler Compiler提供了高性能的data-path综合和优化,简化和自动化了data-path设 计,帮设计者解决复杂而没有规则的data-path设计。Module Compiler提供了大量常用 函数来创建data-path blocks..每一个函数都有设置参数的图形界面。由于篇幅的限制,它 的具体操作和命令略。Behavioral Compiler 和 Module Compiler 3 "character"]] [-variables [-min min_width] [-max max_width] [-start start_cycle] [-finish end_cycle] [-delimiter "character"]] [-summary] [- abstract_fsm [-mask [r][w][o][s]]] [-verbose_fsm [-mask [r][w][o][d][s]]] 6. 写出 RTL 级文件: write 写 RTL 级的.db 文件: 写出RTL 级HDL仿真文件: vhdlout_levelize = true write -format vhdl -hier -output file_name.vhd 7. 可综合的 RTL 输出: write -rtl_script script_file_name 3.2.3 脚本范例 analyze -f vhdl cmplx.vhd /* analyze the vhdl file */ elaborate -s cmplx/* elaborate design for scheduling */ create_clock clk -period 10 write -hier -out cmplx_elab.db /*save elaborated design */ bc_check_design -io super /* Here you may wish to add operating conditions and */ /* wireloads before timing the design */ bc_time_design write -hier -out cmplx_timed.db /*save the timed design */ /* Begin Scheduling Cycle */ /* specifying some scheduling constraints */ /*set_cycles ...*/ /* scheduling with superstate_fixed mode */ schedule -io_mode super /* save scheduling reports to file */ report_schedule -op > cmplx_schd.rpt report_schedule -summary >> cmplx_schd.rpt /* End Scheduling Cycle */ write -hier -out cmplx_rtl.db /*save RTL design to a db*/ write -hier -f vhdl -rtl_script rtl.scr -out syn_rtl.vhd /* saves synthesizable RTL */ vhdlout_levelize = true /*write flattened, simulation-only RTL model*/ vhdlout_use_packages = {ieee.std_logic_1164} /* include all packages used in the design */ write -hier -f vhdl -out cmplx_rtl.vhd /* saves simulatable rt level design */ 3.2ModuleCompiler Moduler Compiler 提供了高性能的 data-path 综合和优化,简化和自动化了 data-path 设 计,帮设计者解决复杂而没有规则的 data-path 设计。 Module Compiler 提供了大量常用 函数来创建 data-path blocks.每一个函数都有设置参数的图形界面。由于篇幅的限制,它 的具体操作和命令略