正在加载图片...

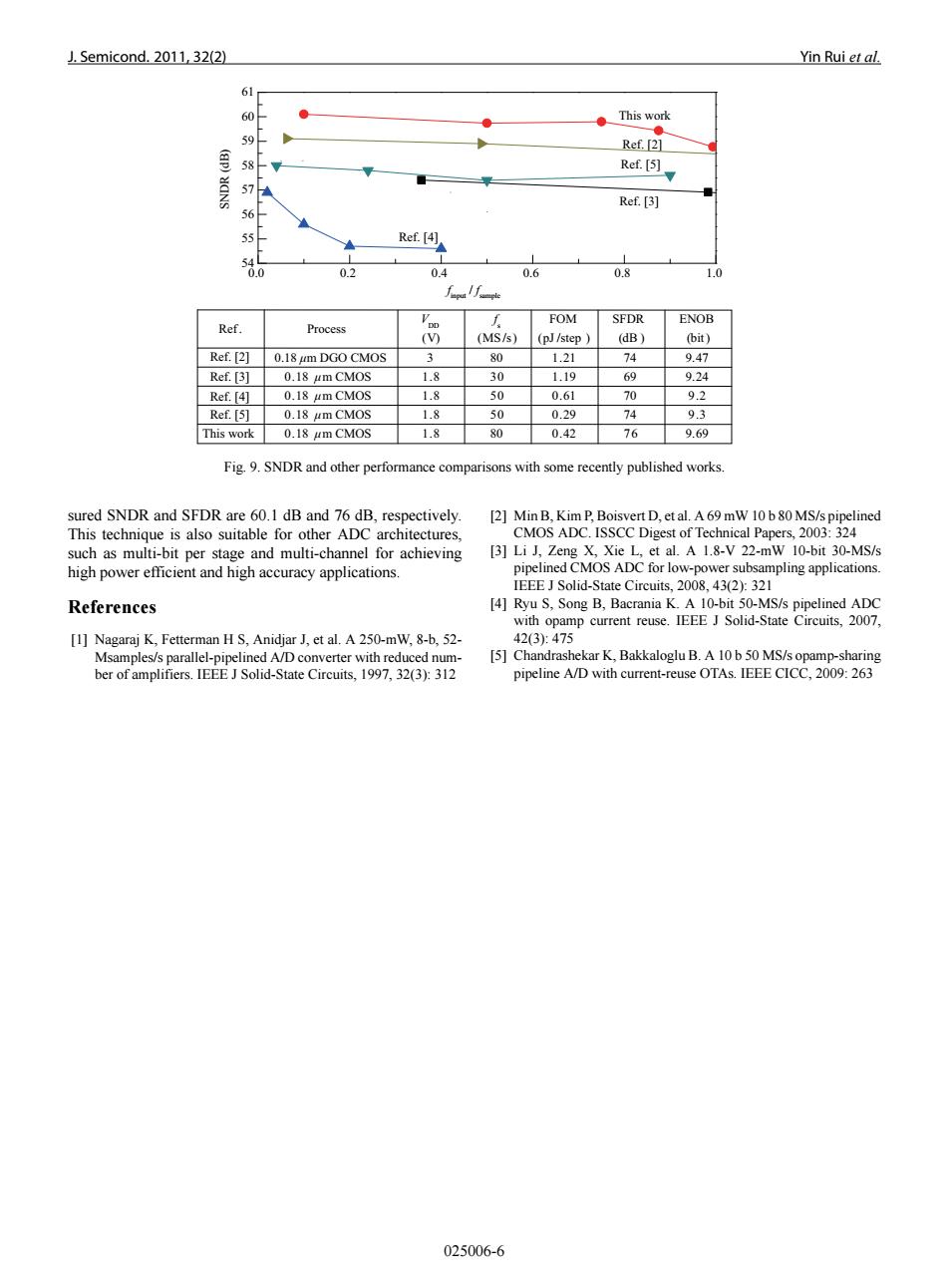

J.Semicond.2011,32(2) Yin Rui et al. 61 60 ●This work 59 Ref.[2] 8 Ref.[5] Ref.[3] 55 Ref.[4] 00 0.2 0.4 0.6 0.8 1.0 fogu/fpe FOM SFDR ENOB Ref. Process (V (MS/s) (pJ /step (dB) (bit) Ref.[2] 0.18 um DGO CMOS 3 80 1.21 74 9.47 Ref.[3] 0.18 um CMOS 1.8 30 1.19 69 9.24 Ref.[4] 0.18 um CMOS 1.8 50 0.61 70 9.2 Ref.[5] 0.18 um CMOS 1.8 50 0.29 74 9.3 This work 0.18 um CMOS 1.8 80 0.42 76 9.69 Fig.9.SNDR and other performance comparisons with some recently published works. sured SNDR and SFDR are 60.1 dB and 76 dB,respectively. [2]Min B,Kim P,Boisvert D,et al.A69 mW 10 b80 MS/s pipelined This technique is also suitable for other ADC architectures. CMOS ADC.ISSCC Digest of Technical Papers,2003:324 such as multi-bit per stage and multi-channel for achieving [3]Li J,Zeng X,Xie L,et al.A 1.8-V 22-mW 10-bit 30-MS/s high power efficient and high accuracy applications. pipelined CMOS ADC for low-power subsampling applications. IEEE J Solid-State Circuits,2008,43(2):321 References [4]Ryu S,Song B,Bacrania K.A 10-bit 50-MS/s pipelined ADC with opamp current reuse.IEEE J Solid-State Circuits,2007, [1]Nagaraj K,Fetterman H S,Anidjar J,et al.A 250-mW,8-b,52- 42(3):475 Msamples/s parallel-pipelined A/D converter with reduced num- [5]Chandrashekar K,Bakkaloglu B.A 10 b 50 MS/s opamp-sharing ber of amplifiers.IEEE J Solid-State Circuits,1997,32(3):312 pipeline A/D with current-reuse OTAs.IEEE CICC,2009:263 025006-6J. Semicond. 2011, 32(2) Yin Rui et al. This work Ref. [2] Ref. [3] Ref. [4] Process VDD f s FOM SFDR ENOB (V) (MS /s) (pJ /step ) (dB ) (bit ) Ref. [2] Ref. [3] Ref. [4] Ref. [5] This work 0.18 μm DGO CMOS 3 80 1.21 74 9.47 0.18 μm CMOS 1.8 0.18 μm CMOS 1.8 50 0.61 70 9.2 30 1.19 69 9.24 0.18 μm CMOS 1.8 50 0.29 74 9.3 0.18 μm CMOS 1.8 80 0.42 76 9.69 Ref . f input / f sample SNDR (dB) 0.0 0.2 0.4 0.6 0.8 1.0 54 55 56 57 58 59 60 61 Ref. [5] Fig. 9. SNDR and other performance comparisons with some recently published works. sured SNDR and SFDR are 60.1 dB and 76 dB, respectively. This technique is also suitable for other ADC architectures, such as multi-bit per stage and multi-channel for achieving high power efficient and high accuracy applications. References [1] Nagaraj K, Fetterman H S, Anidjar J, et al. A 250-mW, 8-b, 52- Msamples/s parallel-pipelined A/D converter with reduced number of amplifiers. IEEE J Solid-State Circuits, 1997, 32(3): 312 [2] Min B, Kim P, Boisvert D, et al. A 69 mW 10 b 80 MS/s pipelined CMOS ADC. ISSCC Digest of Technical Papers, 2003: 324 [3] Li J, Zeng X, Xie L, et al. A 1.8-V 22-mW 10-bit 30-MS/s pipelined CMOS ADC for low-power subsampling applications. IEEE J Solid-State Circuits, 2008, 43(2): 321 [4] Ryu S, Song B, Bacrania K. A 10-bit 50-MS/s pipelined ADC with opamp current reuse. IEEE J Solid-State Circuits, 2007, 42(3): 475 [5] Chandrashekar K, Bakkaloglu B. A 10 b 50 MS/s opamp-sharing pipeline A/D with current-reuse OTAs. IEEE CICC, 2009: 263 025006-6