正在加载图片...

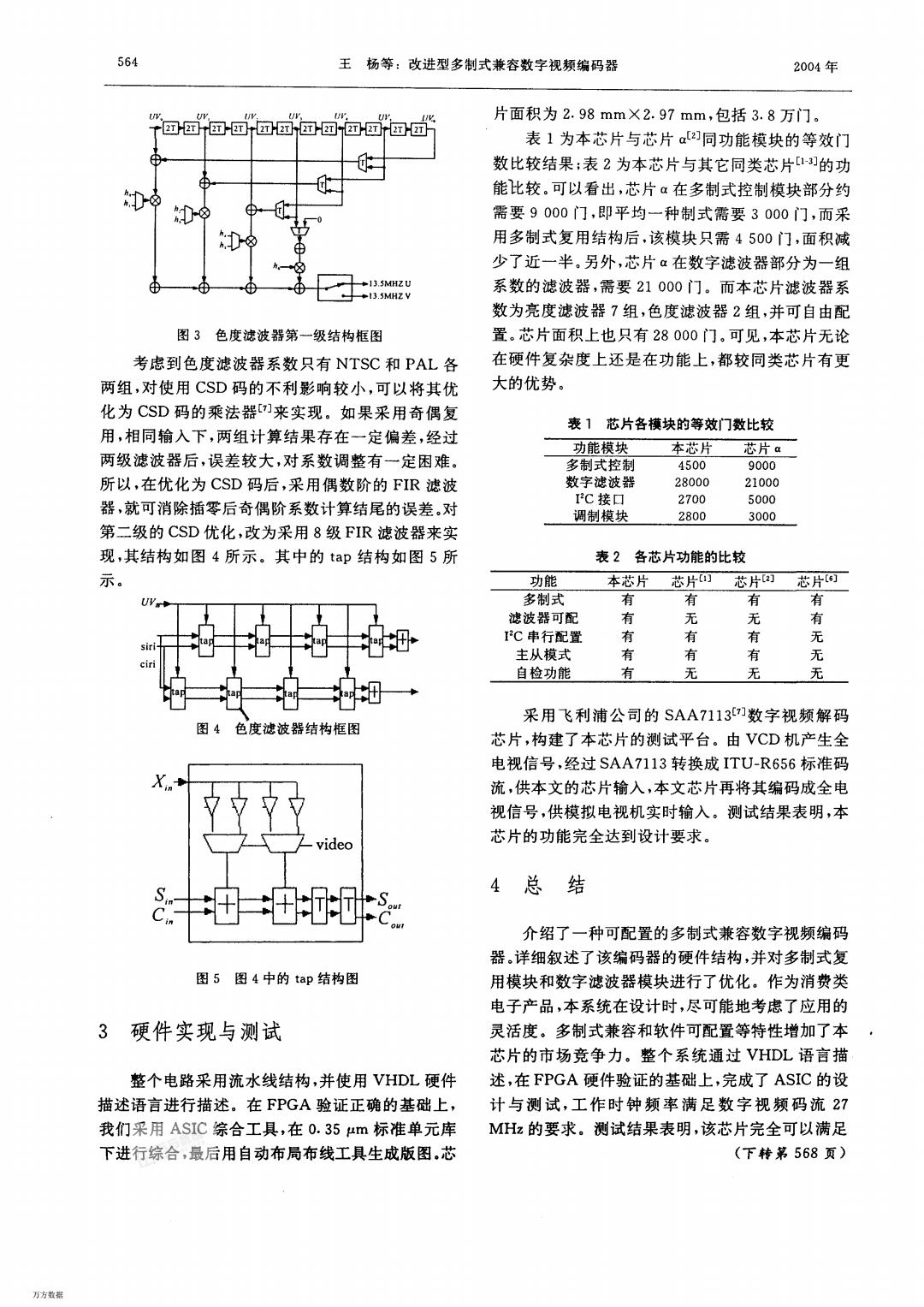

564 王杨等:改进型多制式兼容数字视频编码器 2004年 十四回包@@西面四@四@画武 片面积为2.98mm×2.97mm,包括3.8万门。 表1为本芯片与芯片a同功能模块的等效门 数比较结果;表2为本芯片与其它同类芯片1的功 能比较。可以看出,芯片α在多制式控制模块部分约 需要9000门,即平均一种制式需要3000门,而采 用多制式复用结构后,该模块只需4500门,面积减 少了近一半,另外,芯片α在数字滤波器部分为一组 13.5MHZ U 系数的滤波器,需要21000门。而本芯片滤波器系 13.SMHZ V 数为亮度滤波器7组,色度滤波器2组,并可自由配 图3色度滤波器第一级结构框图 置。芯片面积上也只有28000门,可见,本芯片无论 考虑到色度滤波器系数只有NTSC和PAL各 在硬件复杂度上还是在功能上,都较同类芯片有更 两组,对使用CSD码的不利影响较小,可以将其优 大的优势。 化为CSD码的乘法器[)来实现。如果采用奇偶复 表1 芯片各模块的等效门数比较 用,相同输入下,两组计算结果存在一定偏差,经过 功能模块 本芯片芯片。 两级滤波器后,误差较大,对系数调整有一定困难。 多制式控制 4500 9000 所以,在优化为CSD码后,采用偶数阶的FIR滤波 数字滤波器 28000 21000 器,就可消除插零后奇偶阶系数计算结尾的误差。对 IC接口 2700 5000 调制模块 2800 3000 第二级的CSD优化,改为采用8级FIR滤波器来实 现,其结构如图4所示。其中的tap结构如图5所 表2各芯片功能的比较 示。 功能 本芯片芯片而芯片芯片 U 多制式 有 有 有 有 滤波器可配 有 无 无 有 I℃串行配置 有 莎 有 无 siri 主从模式 有 有 有 无 自检功能 有 无 无 无 采用飞利浦公司的SAA7113)数字视频解码 图4色度滤波器结构框图 芯片,构建了本芯片的测试平台。由VCD机产生全 电视信号,经过SAA7113转换成ITU-R656标准码 流,供本文的芯片输入,本文芯片再将其编码成全电 视信号,供模拟电视机实时输入。测试结果表明,本 video 芯片的功能完全达到设计要求。 4总结 中中中00 介绍了一种可配置的多制式兼容数字视频编码 器。详细叙述了该编码器的硬件结构,并对多制式复 图5图4中的tap结构图 用模块和数字滤波器模块进行了优化。作为消费类 电子产品,本系统在设计时,尽可能地考虑了应用的 3硬件实现与测试 灵活度。多制式兼容和软件可配置等特性增加了本 芯片的市场竞争力。整个系统通过VHDL语言描 整个电路采用流水线结构,并使用VHDL硬件 述,在FPGA硬件验证的基础上,完成了ASIC的设 描述语言进行描述。在FPGA验证正确的基础上, 计与测试,工作时钟频率满足数字视频码流27 我们采用ASIC综合工具,在0.35μm标准单元库 MHz的要求。测试结果表明,该芯片完全可以满足 下进行综合,最后用自动布局布线工具生成版图,芯 (下转第568页) 万方数搭王 杨等:改进型多制式兼容数字视频编码器 2004年 图3 色度滤波器第一级结构框图 考虑到色度滤波器系数只有NTSC和PAL各 两组,对使用CSD码的不利影响较小,可以将其优 化为CSD码的乘法器[,1来实现。如果采用奇偶复 用,相同输入下,两组计算结果存在一定偏差,经过 两级滤波器后,误差较大,对系数调整有一定困难。 所以,在优化为CSD码后,采用偶数阶的FIR滤波 器,就可消除插零后奇偶阶系数计算结尾的误差。对 第二级的CSD优化,改为采用8级FIR滤波器来实 现,其结构如图 4所示。其中的 tap结构如图 5所 示 。 片面积为 2.98 mm X 2.97 mm,包括 3.8万门。 表 1为本芯片与芯片a [z〕同功能模块的等效门 数比较结果;表2为本芯片与其它同类芯片[1-3〕的功 能讹较。可以看出,芯片。在多制式控制模块部分约 需要 9 000门,即平均一种制式需要 3 000门,而采 用多制式复用结构后,该模块只需4 500门,面积减 少了近一半。另外,芯片a在数字滤波器部分为一组 系数的滤波器,需要 21 000门。而本芯片滤波器系 数为亮度滤波器 7组,色度滤波器2组,并可自由配 置。芯片面积上也只有 28 000门。可见,本芯片无论 在硬件复杂度上还是在功能上,都较同类芯片有更 大的优势。 表 1 芯片各模块的等效门数比较 功能模块 多制式控制 数字滤波器 PC接 口 调制模块 本芯片 4500 28000 2700 2800 芯片 。 9000 21000 5000 3000 表 2 各芯片功能的比较 尸 一有 无 有 有 无 功能 本芯片 芯 ] 芯片[z〕 芯片 有 [‘〕 有 无 无 无 有 无 有 有 无 有 有 有 有 有 多制式 滤波器可配 PC申行配置 主从模式 自检功能 图4 色度滤波器结构框图 xi. 二滋-}- -}- T videTo 图5 图4中的 tap结构图 采用飞利浦公司的SAA7113[71数字视频解码 芯片,构建了本芯片的测试平台。由VCD机产生全 电视信号,经过SAA7113转换成ITU-R656标准码 流,供本文的芯片输入,本文芯片再将其编码成全电 视信号,供模拟电视机实时输入。测试结果表明,本 芯片的功能完全达到设计要求。 叹 4 总 结 C 3 硬件实现与测试 整个电路采用流水线结构,并使用VHDL硬件 描述语言进行描述。在FPGA验证正确的基础上, 我们采用ASIC综合工具,在 0. 35 jim标准单元库 下进行综合,最后用自动布局布线工具生成版图.芯 介绍了一种可配置的多制式兼容数字视频编码 器。详细叙述了该编码器的硬件结构,并对多制式复 用模块和数字滤波器模块进行了优化。作为消费类 电子产品,本系统在设计时,尽可能地考虑了应用的 灵活度。多制式兼容和软件可配置等特性增加了本 芯片的市场竞争力。整个系统通过VHDL语言描 述,在FPGA硬件验证的基础上,完成了ASIC的设 计与测试,工作时钟频率满足数字视频码流 27 MH:的要求。测试结果表明,该芯片完全可以满足 <-F转第 568页) 万方数据