正在加载图片...

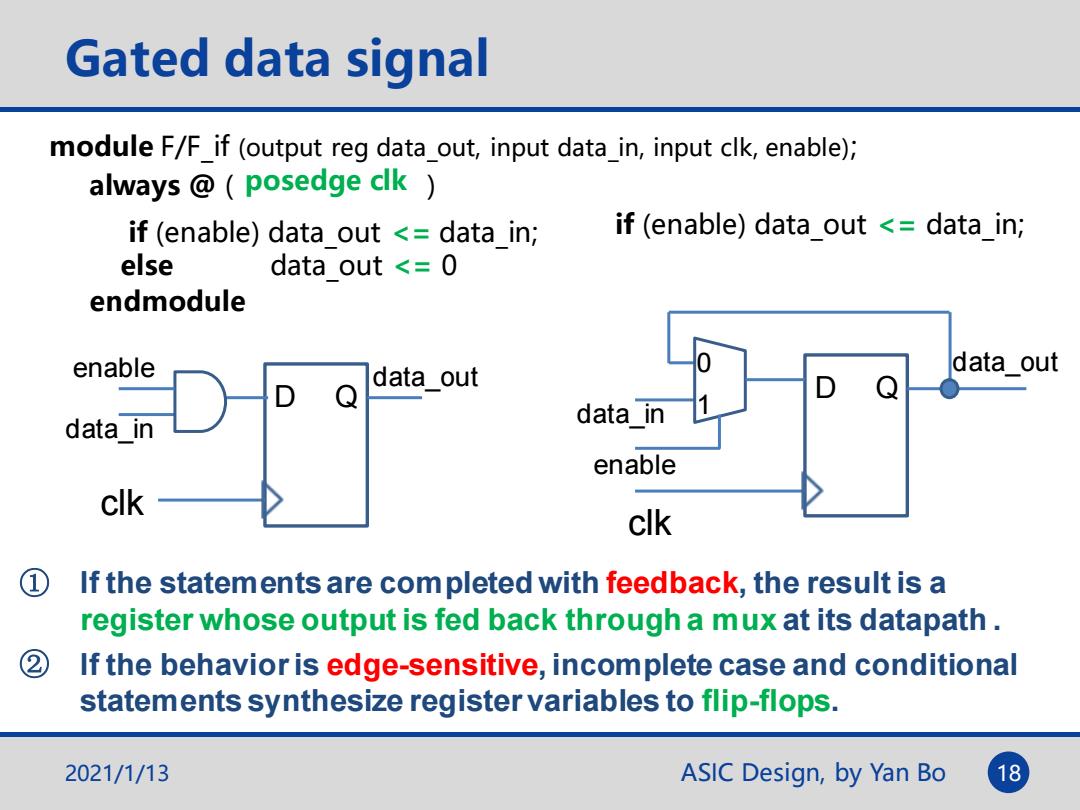

Gated data signal module F/F_if (output reg data_out,input data_in,input clk,enable); always @posedge clk if (enable)data out <data in; if (enable)data out <data in; else data out <=0 endmodule enable data out data out data in enable clk clk If the statements are com pleted with feedback,the result is a register whose output is fed back through a mux at its datapath. If the behavior is edge-sensitive,incomplete case and conditional statements synthesize register variables to flip-flops. 2021/1/13 ASIC Design,by Yan Bo 18ASIC Design, by Yan Bo Gated data signal module F/F_if (output reg data_out, input data_in, input clk, enable); always @ ( ) endmodule if (enable) data_out <= data_in; else data_out <= data_out; ① If the statements are completed with feedback, the result is a register whose output is fed back through a mux at its datapath . ② If the behavior is edge-sensitive, incomplete case and conditional statements synthesize register variables to flip-flops. 1 0 data_out data_in enable clk D Q data_out data_in enable clk D Q posedge clk 2021/1/13 18 if (enable) data_out <= data_in; else data_out <= 0