Topic2:FPGA Design with Verilog FPGA Design Method Design flow tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples 。RTL level design Components of Datapath Components of Controller Supplementary ·Synthesizable 。Some experiences 。Other syntax rules 2021/1/13 ASIC Design,by Yan Bo 3

ASIC Design, by Yan Bo Topic2: FPGA Design with Verilog FPGA Design Method Design flow & tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples • RTL level design • Components of Datapath • Components of Controller Supplementary • Synthesizable • Some experiences • Other syntax rules 2021/1/13 3

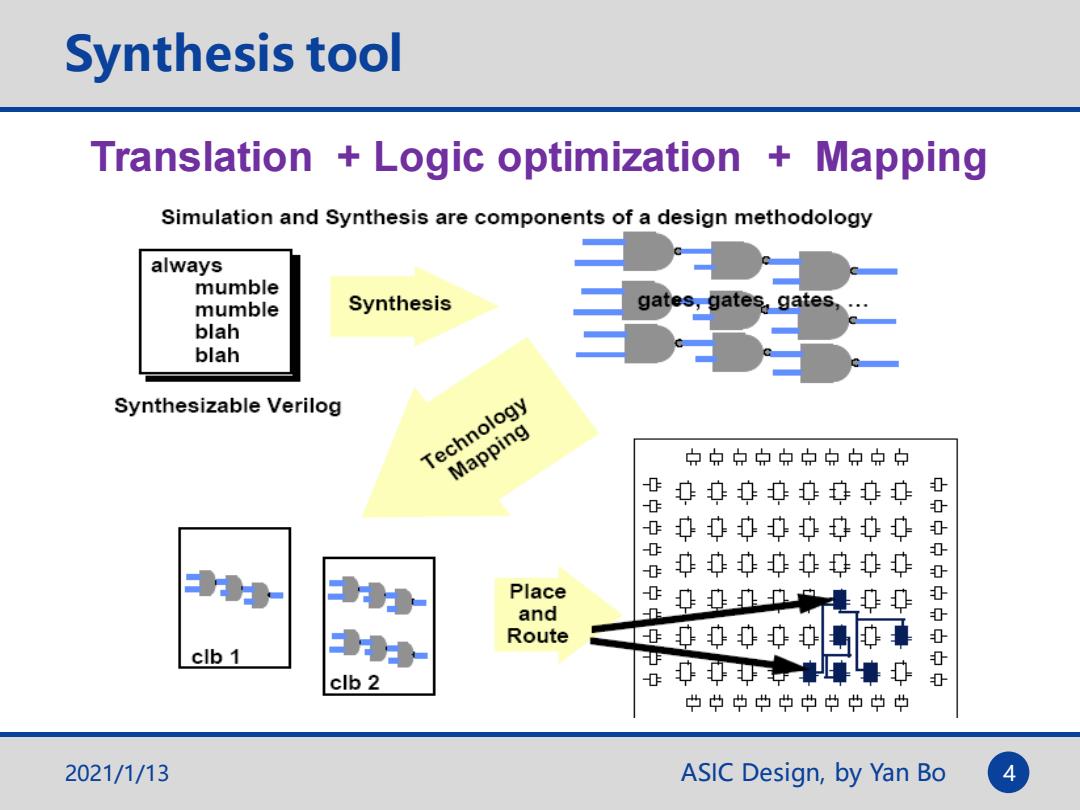

Synthesis tool Translation Logic optimization Mapping Simulation and Synthesis are components of a design methodology always mumble mumble Synthesis gates,gates,gates, blah blah Synthesizable Verilog Technology Mapping 白白白白白白白白白白 800000000 0中中中中中中中中 0 中中中中中中中中 Place and 00n是09 0 Route clb1 clb2 中中中中中中中单中中 2021/1/13 ASIC Design,by Yan Bo

ASIC Design, by Yan Bo Synthesis tool 2021/1/13 4 Translation + Logic optimization + Mapping

Logic optimization 综合目标: 在满足物理约束条件下,综合出最优的逻辑结构。 Area,Delay,Fan in/out,Types of component 主要步骤: 优化算法: ◆检测消除冗余逻辑 ◆查找组合反馈环路 消去操作Elimination ◆利用无关紧要条件 替代操作Substitution ,上多级网络 ◆检测未使用的状态 因式分解Factoring ◆查找消除等价的状态 二级优化2-level optimization ◆进行状态分配 2021/1/13 ASIC Design,by Yan Bo 5

ASIC Design, by Yan Bo Logic optimization 2021/1/13 5 主要步骤: ◆检测消除冗余逻辑 ◆查找组合反馈环路 ◆利用无关紧要条件 ◆检测未使用的状态 ◆查找消除等价的状态 ◆进行状态分配 综合目标: 在满足物理约束条件下,综合出最优的逻辑结构。 Area, Delay, Fan in/out, Types of component 优化算法: ◆ 消去操作Elimination ◆ 替代操作Substitution ◆ 因式分解Factoring ◆ 二级优化2-level optimization 多级网络

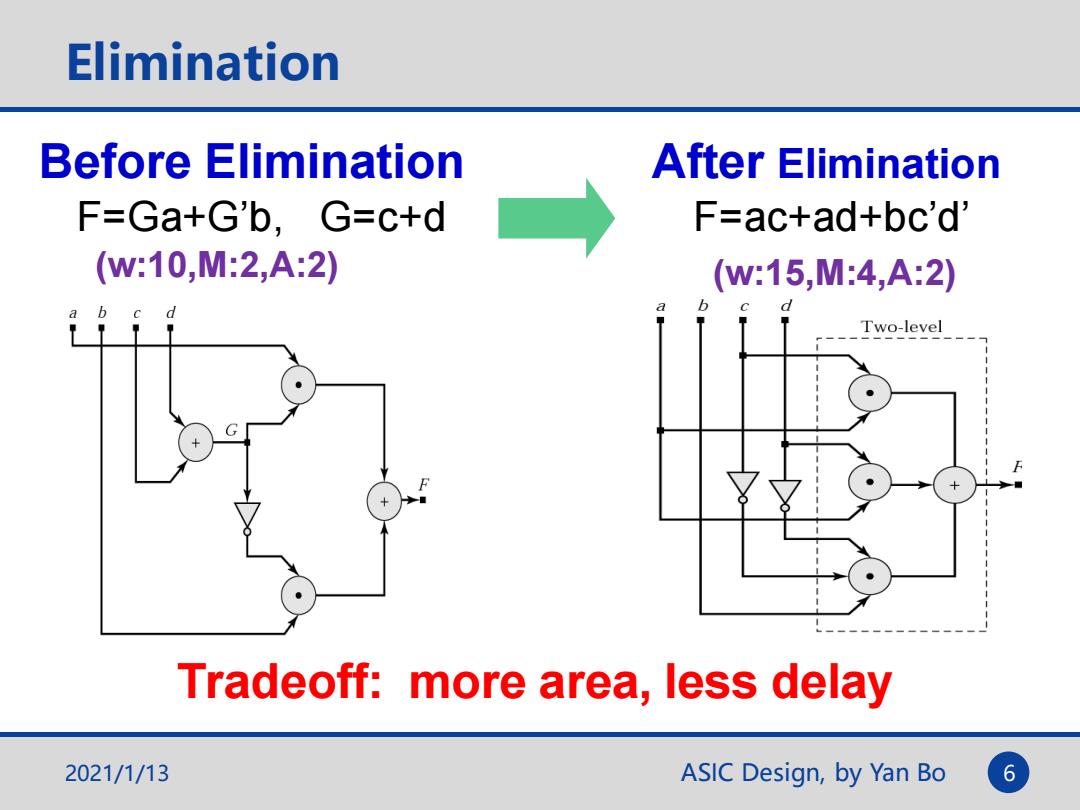

Elimination Before Elimination After Elimination F=Ga+G'b,G=c+d F=ac+ad+bc'd' w:10,M:2,A:2) (w:15,M:4,A:2) b c a Two-level Tradeoff:more area,less delay 2021/1/13 ASIC Design,by Yan Bo 6

ASIC Design, by Yan Bo Elimination 2021/1/13 6 After Elimination F=ac+ad+bc’d’ Before Elimination F=Ga+G’b, G=c+d (w:10,M:2,A:2) (w:15,M:4,A:2) Tradeoff: more area, less delay

Factoring Before factoring After factoring F=ac+ad+bc+bd+e F=(a+b)(c+d)+e w:17,M:4,A:4) (W:9,M:1,A:3) b (a1b) (c1d) Tradeoff:less area,more delay 2021/1/13 ASIC Design,by Yan Bo 7

ASIC Design, by Yan Bo Factoring 2021/1/13 7 Tradeoff: less area, more delay After factoring F=(a+b)(c+d)+e Before factoring F=ac+ad+bc+bd+e (w:17,M:4,A:4) (w:9,M:1,A:3)

Topic2:FPGA Design with Verilog FPGA Design Method Design flow tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples 。RTL level design Components of Datapath Components of Controller Supplementary 。Synthesizable ·Some experiences 。Other syntax rules 2021/1/13 ASIC Design,by Yan Bo 8

ASIC Design, by Yan Bo Topic2: FPGA Design with Verilog FPGA Design Method Design flow & tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples • RTL level design • Components of Datapath • Components of Controller Supplementary • Synthesizable • Some experiences • Other syntax rules 2021/1/13 8

Some experiences >Balance architecture Share resources Gated signal >Assignment statement Accident Intentional Latch 2021/1/13 ASIC Design,by Yan Bo 9

ASIC Design, by Yan Bo Some experiences 2021/1/13 9 ➢ Balance architecture ➢ Share resources ➢ Gated signal ➢Assignment statement ➢ Accident / Intentional Latch

Some experiences Balance architecture Share resources Gated signal >Assignment statement Accident Intentional Latch 2021/1/13 ASIC Design,by Yan Bo 10

ASIC Design, by Yan Bo Some experiences 2021/1/13 10 ➢ Balance architecture ➢ Share resources ➢ Gated signal ➢Assignment statement ➢ Accident / Intentional Latch

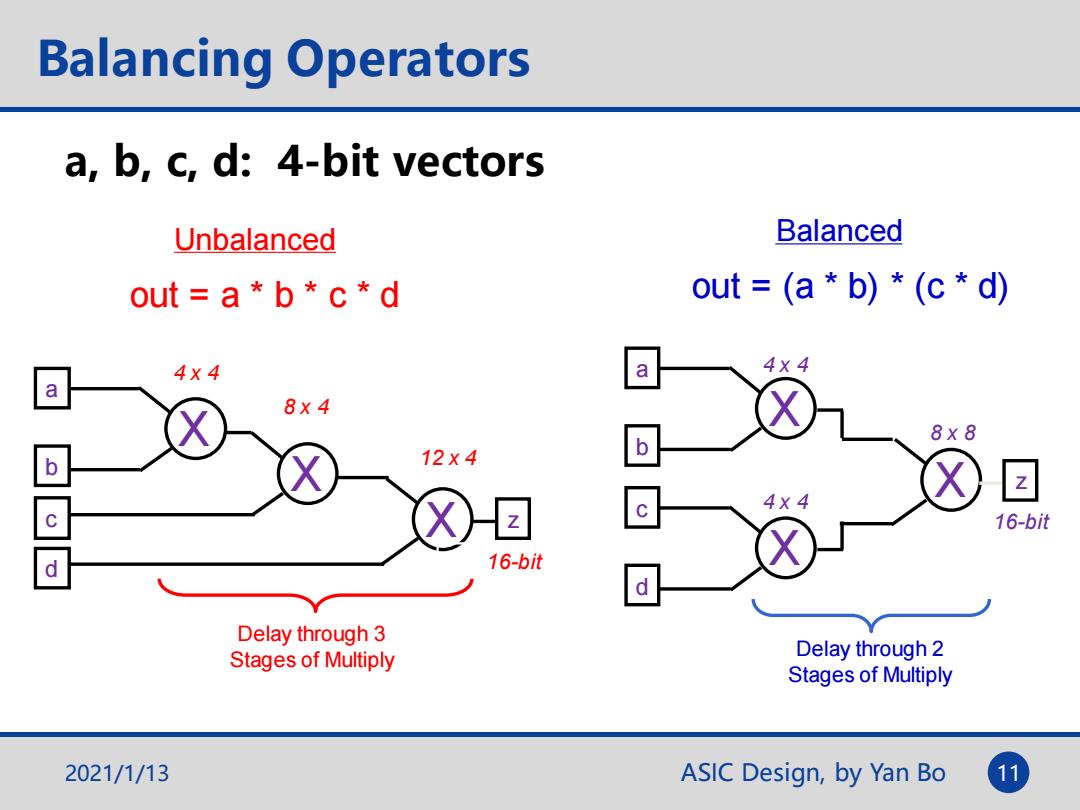

Balancing Operators a,b,c,d:4-bit vectors Unbalanced Balanced out a b c d out =(a b)*(c d) a 4X4 a 4X4 8X4 8X8 12x4 回 4X4 16-bit 16-bit Delay through 3 Stages of Multiply Delay through 2 Stages of Multiply 2021/1/13 ASIC Design,by Yan Bo 11

ASIC Design, by Yan Bo Balancing Operators a, b, c, d: 4-bit vectors out = a * b * c * d X a b X c X d z X a b out = (a * b) * (c * d) X c d X z Unbalanced Balanced 4 x 4 8 x 4 12 x 4 16-bit 4 x 4 4 x 4 8 x 8 16-bit Delay through 3 Stages of Multiply Delay through 2 Stages of Multiply 2021/1/13 11

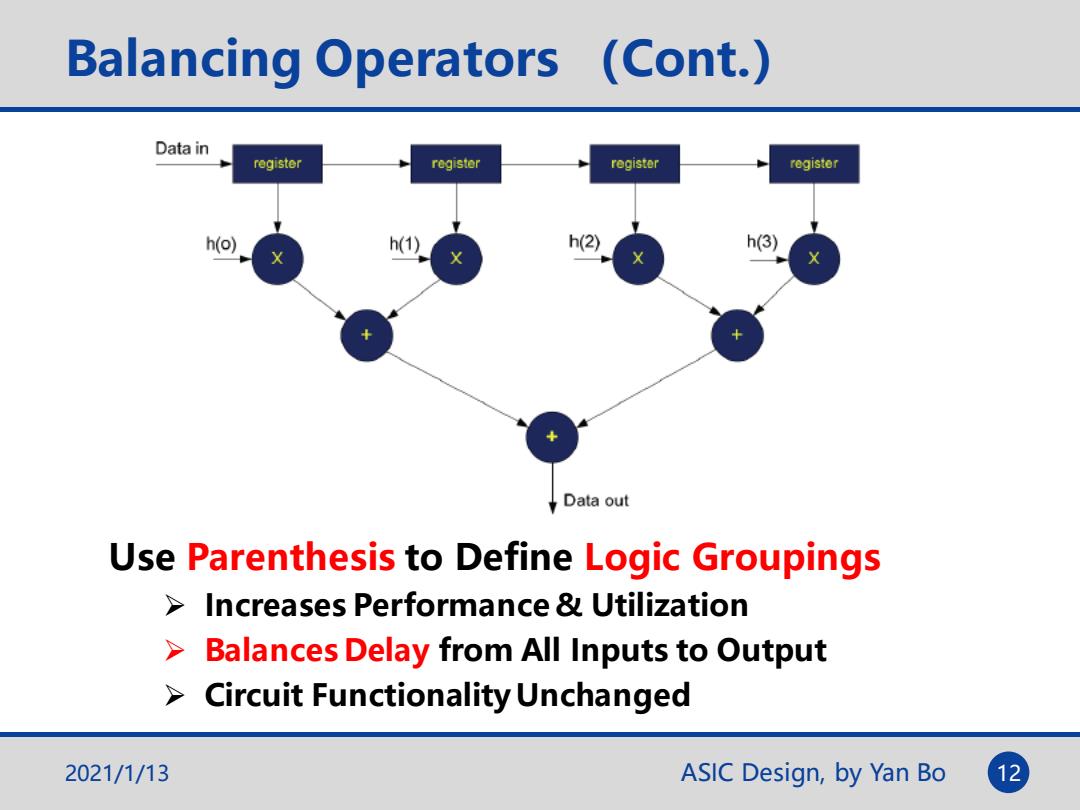

Balancing Operators (Cont.) Data in register register register register h(o) h(1) h(2) h(3) Data out Use Parenthesis to Define Logic Groupings Increases Performance Utilization >Balances Delay from All Inputs to Output Circuit Functionality Unchanged 2021/1/13 ASIC Design,by Yan Bo 12

ASIC Design, by Yan Bo Balancing Operators (Cont.) 2021/1/13 12 Use Parenthesis to Define Logic Groupings ➢ Increases Performance & Utilization ➢ Balances Delay from All Inputs to Output ➢ Circuit Functionality Unchanged