正在加载图片...

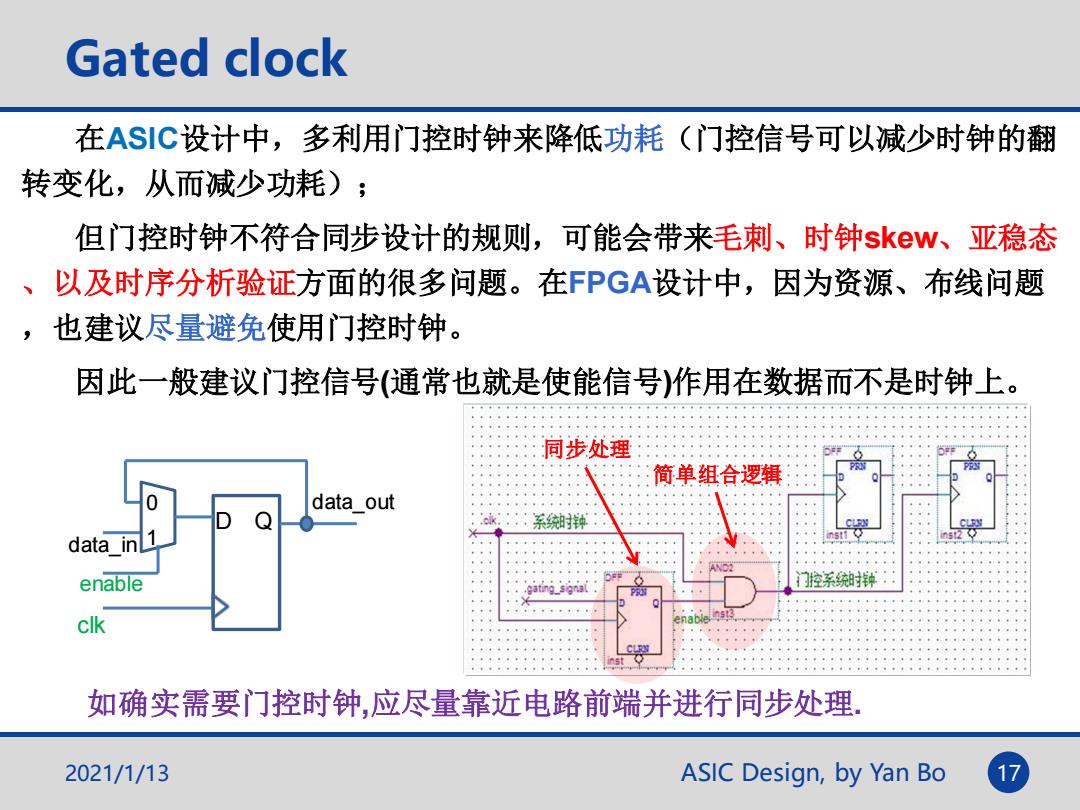

Gated clock 在ASIC设计中,多利用门控时钟来降低功耗(门控信号可以减少时钟的翻 转变化,从而减少功耗) 但门控时钟不符合同步设计的规则,可能会带来毛刺、时钟skw、亚稳态 、以及时序分析验证方面的很多问题。在FPGA设计中,因为资源、布线问题 也建议尽量避免使用门控时钟。 因此一般建议门控信号(通常也就是使能信号)作用在数据而不是时钟上。 同步处理 简单组合逻辑 data_out 系钟 data_inl enable gating_signal clk 如确实需要门控时钟,应尽量靠近电路前端并进行同步处理. 2021/1/13 ASIC Design,by Yan BoASIC Design, by Yan Bo Gated clock 在ASIC设计中,多利用门控时钟来降低功耗(门控信号可以减少时钟的翻 转变化,从而减少功耗); 但门控时钟不符合同步设计的规则,可能会带来毛刺、时钟skew、亚稳态 、以及时序分析验证方面的很多问题。在FPGA设计中,因为资源、布线问题 ,也建议尽量避免使用门控时钟。 因此一般建议门控信号(通常也就是使能信号)作用在数据而不是时钟上。 2021/1/13 17 1 0 data_out data_in enable clk D Q 简单组合逻辑 同步处理 如确实需要门控时钟,应尽量靠近电路前端并进行同步处理