正在加载图片...

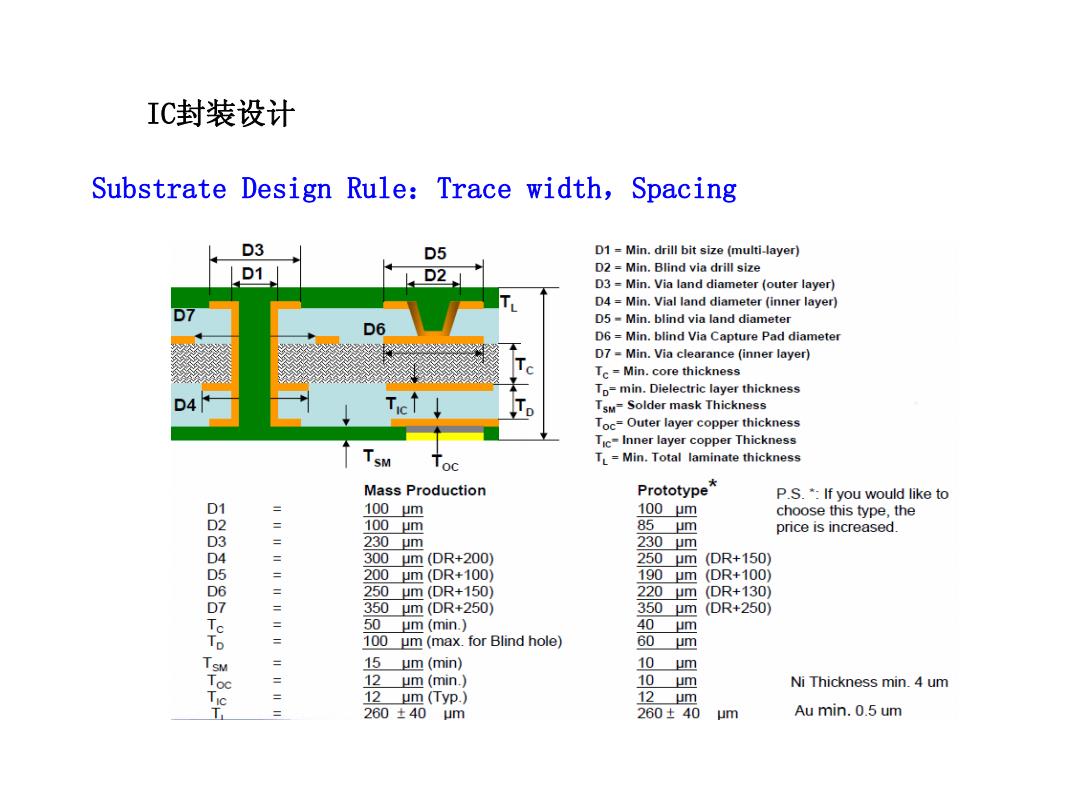

IC封装设计 Substrate Design Rule:Trace width,Spacing D3 D5 D1 =Min.drill bit size (multi-layer) D1 D2=Min.Blind via drill size D2 D3=Min.Via land diameter (outer layer) D4 Min.Vial land diameter (inner layer) D5-Min.blind via land diameter D6 D6=Min.blind Via Capture Pad diameter D7-Min.Via clearance (inner layer) Tc=Min.core thickness To=min.Dielectric layer thickness TsM-Solder mask Thickness Toc=Outer layer copper thickness Tic-Inner layer copper Thickness TsM Toc TL=Min.Total laminate thickness Mass Production Prototype* P.S.*If you would like to 100μm 100μm choose this type,the 100m 85μm price is increased. 8888888138 230μm 230μm 300μm(DR+200) 250m(DR+150) 200m(DR+100) 190m(DR+100 250Jm(DR+150) 220μm(DR+130) 350μm(DR+250) 350μm (DR+250) 50μm(min.) 40μm 100 um (max.for Blind hole) 60m 15 um (min) 10 m 12μm(min) 10m Ni Thickness min.4 um 12 um (Typ.) 12m 260±40um 260±40 um Au min.0.5 umwww.chinafastprint.com Substrate Design Rule:Trace width,Spacing IC封装设计