《IC封装设计与仿真》 ” QQ:402977009 群:24640973

www.chinafastprint.com 《IC封装设计与仿真》 QQ:402977009 群:24640973

1.IC封装设计 2.封装电磁仿真 3.封装热仿真 4.封装结构仿真

www.chinafastprint.com 1.IC封装设计 3.封装热仿真 2.封装电磁仿真 内容 4.封装结构仿真

1.IC封装设计

www.chinafastprint.com 1.IC封装设计

IC封装设计 IC封装内部结构: DIP (Dual In-line Package) SIP 正面 Pin脚 塑封 背面 SSOP Mold resin OKI JAPAN Chip 晶体 7578H (Shrink Small 5012902 Outline Package)Gold wire 芯片 5的的的的的的 Lead 金线 RLC元件 基板 QFP Chip // (Quad Flat Package) Gold wire 4 Mold resin Lead

www.chinafastprint.com IC封装内部结构: IC封装设计 塑封 金线 基板 芯片 RLC元件 晶体 Pin脚

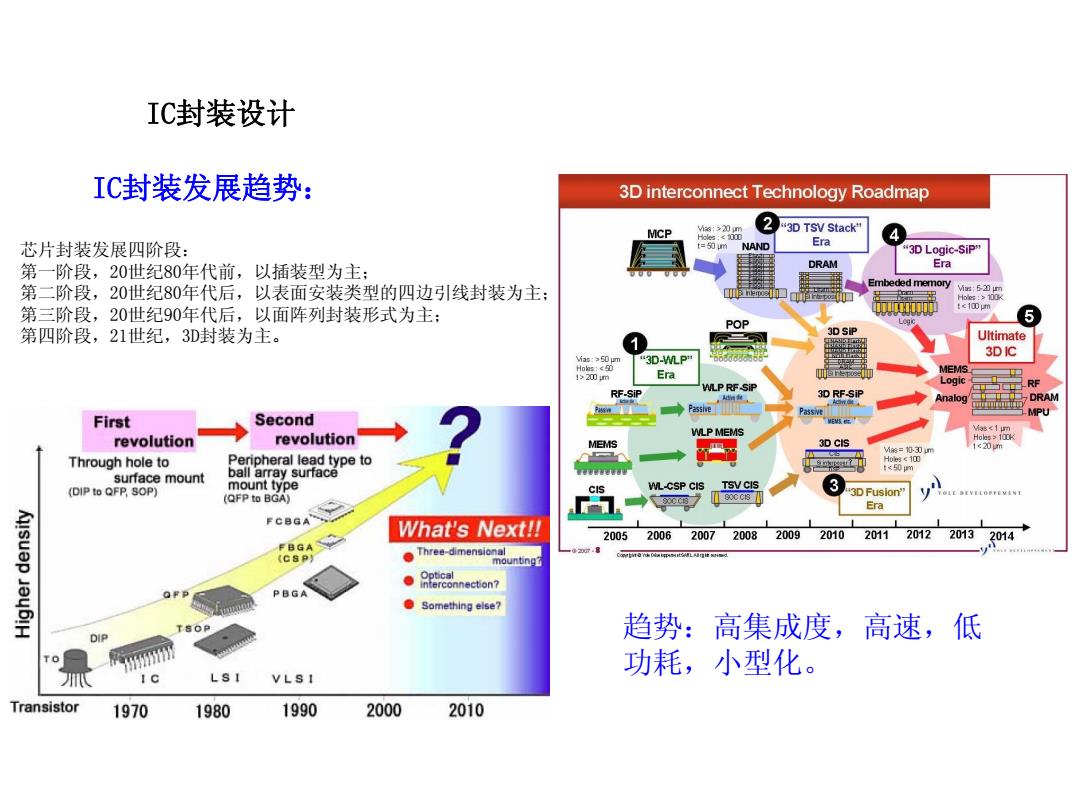

IC封装设计 IC封装发展趋势: 3D interconnect Technology Roadmap MCP Vis:>20 um 2“3 D TSV Stack' 4 芯片封装发展四阶段: t=5约mAND Era 3D Logic-SiP" 第一阶段,20世纪80年代前,以插装型为主: DRAM Era 第二阶段,20世纪80年代后,以表面安装类型的四边引线封装为主: Embeded memory 52』 第三阶段,20世纪90年代后,以面阵列封装形式为主: 0000007 POP 5 第四阶段,21世纪,3D封装为主。 3D SIP Ultimate 3D IC "3D-WLP" Era MEMS Logic RF-SiP WLP RF.SiP 3D RF.SiP Analog DRAM Psse Passive First Second E WLP MEMS Mas<1um revolution revolution Haks 100K ME日MS 3D CIs Vies=10-30 um 1e20m Through hole to Peripheral lead type to Hoesc10 nenn t<50m surface mount ball array surface (DIP to QFP,SOP) mount type CIS WL-CSP CIS TSVCIS 3 3D Fusion' (QFP to BGA) 9000s7 Era FCBGA What's Next!! F台GA 20052006 2007 2008 2009 2010 2011 20122013 2014 Three-dimensional (CSP) mounting? Optical interconnection? OF P PBGA ●Something else7 趋势:高集成度,高速,低 DIP 功耗,小型化。 LSI VLSI Transistor 1970 1980 1990 2000 2010

www.chinafastprint.com IC封装发展趋势: IC封装设计 趋势:高集成度,高速,低 功耗,小型化。 芯片封装发展四阶段: 第一阶段,20世纪80年代前,以插装型为主; 第二阶段,20世纪80年代后,以表面安装类型的四边引线封装为主; 第三阶段,20世纪90年代后,以面阵列封装形式为主; 第四阶段,21世纪,3D封装为主

IC封装设计 IC封装工艺(sip):SMT,DA,WB,Mold SMT Die Wafer Wafer Attaching Grinding Sawing Flip Chip Ball Wire Placement Molding Bonding Marking Singulation FT Packing

www.chinafastprint.com IC封装工艺(sip):SMT,DA,WB,Mold IC封装设计

IC封装设计 Substrate)加工工艺:HDI,Buiding up 绿油 金层 镍层 铜层 通孔 介电层 埋孔 盲孔 内层线路 Substrates结构

www.chinafastprint.com Substrate加工工艺:HDI,Buiding up IC封装设计 介电层 绿油 铜层 埋孔 盲孔 通孔 金层 镍层 内层线路 Substrate结构

IC封装设计 Substrate加工工艺: -. Cap Plating D/F Lamination Imaging Developing 3C: Etching Striping SR Printing Imaging Developing LPR or D/F Imaging Developing Gold Plating LPR Striping Etching Routing

www.chinafastprint.com Substrate加工工艺: IC封装设计

IC封装设计 ITEM UNIT HTCC HTCC LTCC LTCC LTCC LTCC LTCC A440 Ao600 G940 G1771 GL950 GL330 GL331 Substrate: 板材 【HITCE】 1 Dielectric Constant 1MHz 9.8 9.0 53 7.8 2G收 88 187 52 9.4 77 7.6 10GHz 87 18.8 52 9.4 7.6 介电系数, Bectrical Dielectric Loss Angle 1MHz 10e-4 、 10 2G收 10e-4 24 21 的 36 5 12 正切损耗角, 10G 10e-4 15 33 38 14 Conductor Material 、 W/Mo Cu/W Cu Ag Cu Cu 导热系数, Sheet Resistance mQ/▣ 10-12 40 3.0 3.0 3.0 3.0 3.0 Thermal Expansion RT≈ 10e-6/K 7.1 72 10.7 12.3 8.5 8.2 72 热膨胀系数, 400℃1 Thermal Conductivity W/mK 14 15 35 2 4.1 43 32 Specific Heat 10e+3J/KgK 0.77 0.77 0.62 绿色材料, Q78 Flexural Strength MPa 400 400 220 170 400 400 400 价格因素。 Young's Moddes of Elasticity GPa 310 260 188 74 172 178 150 XY Shrinkage Tolerance ±1.0 ±1.0 ±1.0 ±1.0 ±0.25 ±1.0 ±1.0 Thun Layer Thickness um 50 25 名 0 5035) 20 Tg CTE Dk Df Tg CTE Dk Supplier Model deeC ppardeg.C RoHS? JPCA? Lead free? Supplier Model deec ppi deg.C RoHS? JPCA? Lead free☒ DMA TMA Z-5 1GH业 @IGHz DMA TMA 5 @1G业 @IGHz MGC HL832MG 205 50 41 0.0090 Yes No Yes R-5755(Megtron 5) 210 3.5 0.0040 Yes No Yes HL832EX 210 0 4.4 0.0090 Yes No Yes R-5715(Megtron) 180 702 3.7 0.0120 Yes No Yes HL832NB 205 41 0.0090 Yes Ye Yes Risbo PPE(CS-3376A) 195 702 33 0.0050 No No Yes HΠ832NX-A 230 30 4.7 0.0130 Yes Yes Yes Fokimx(GMPL195) 包C-4781 190 175 45 4.0 0.0220 No Getek ML200D 180 59 3.9 0.0120 Yes No Yes ELC-4785GS 265 220 16 4.2 0.0070 No Getek II 200 45 3.8 0.0050 日C.478 SGSLE -38 -0.006 PCL-HF-571 165 Yes Yes Yes Rogeis R03003 24 3.0 0.0013 PCL-LD-621 210 55 3.5 0.0050 Yes Yes Yes R03006 24 6.15 0.0020 R03010 24 102 0.0023 Hitachl MCL-E679 173 55 4.2 0.0195 Yes No Yes 25 48 R03203 58 MCL-E679FGB 165 0.0120 Yes Yes Yes 3.02 0.0016 MCL-Z R03206 45 6.15 0.0027 Yes Yes MCL-LX-67 185 0 3.4H 0.0043 R03210 34 10.2 0.0027 MCF-6000E 165 80-90 38 0.0260 Yes Yes R03035 24 33 0.0017 MCF-6000G 160 80-90 0.0250 Yes Yes R/fex LCP36003850 150 29 0.0020 Resin Coated Foi 115 100~11035 0.0250 Yes Yes MCH7IG 200 0.0060 Yes Yes PTFE 100 45 2.4 0.0010

www.chinafastprint.com Substrate:板材 IC封装设计 介电系数, 正切损耗角, 导热系数, 热膨胀系数, 绿色材料, 价格因素

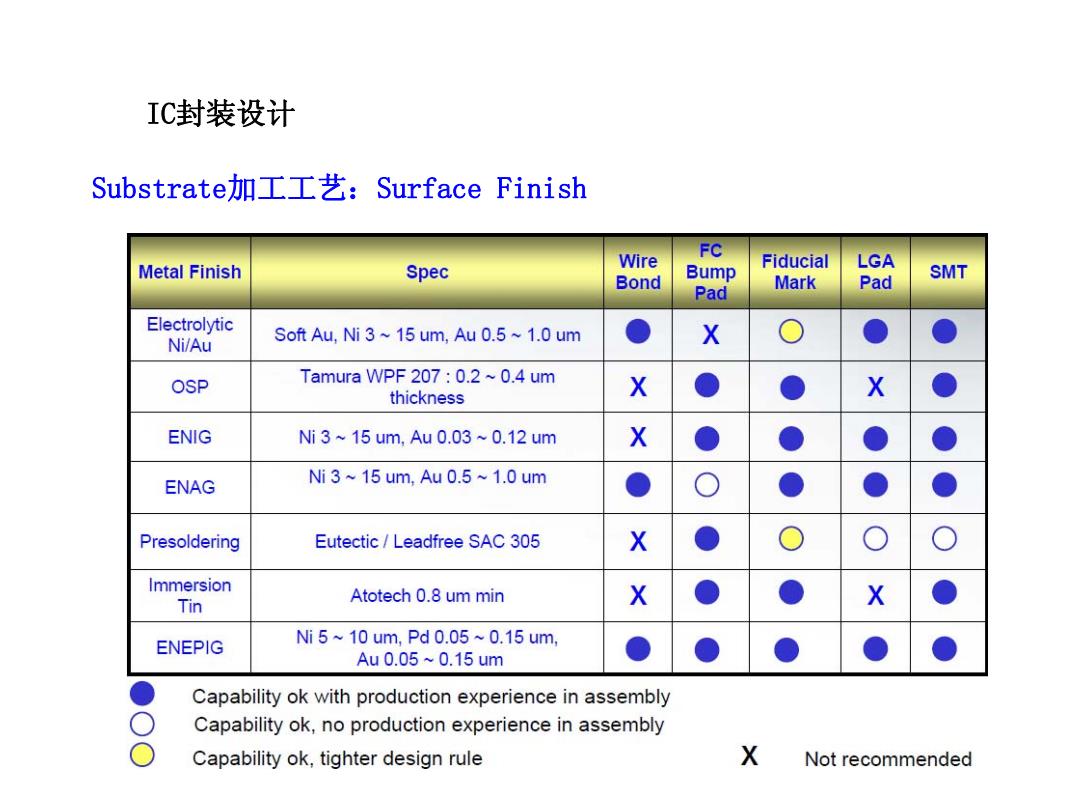

IC封装设计 Substrate加工工艺:Surface Finish FC Metal Finish Spec Wire Bond Bump Fiducial LGA Pad SMT Pad Mark Electrolytic Ni/Au Soft Au,Ni 3~15 um,Au 0.5~1.0 um X OSP Tamura WPF 207:0.2~0.4 um thickness X X ENIG Ni3~15um,Au0.03~0.12um X ENAG Ni 3~15 um,Au 0.5~1.0 um Presoldering Eutectic/Leadfree SAC 305 Immersion Tin Atotech 0.8 um min X X ENEPIG Ni5~10um,Pd0.05~0.15um, Au0.05~0.15um Capability ok with production experience in assembly Capability ok,no production experience in assembly Capability ok,tighter design rule X Not recommended

www.chinafastprint.com Substrate加工工艺:Surface Finish IC封装设计