第八章 常用组合逻辑器件及应用 8.1编码器 把二进制码按一定规律编排,使每组代码具 有一特定的含义,称为编码。 具有编码功能的逻辑电路称为编码器。 n位二进制代码有2n种组合,可以表示2n个信息。 要表示N个信息所需的二进制代码应满足2≥N

第八章 常用组合逻辑器件及应用 8.1 编码器 把二进制码按一定规律编排,使每组代码具 有一特定的含义,称为编码。 具有编码功能的逻辑电路称为编码器。 n 位二进制代码有 2 n种组合,可以表示 2 n个信息。 要表示N个信息所需的二进制代码应满足 2 n N

一.二进制编码器 将输入信号编成二进制代码的电路。 即用n位二进制代码表示N个信号的电路

一 . 二进制编码器 将输入信号编成二进制代码的电路。 即用n位二进制代码表示N个信号的电路

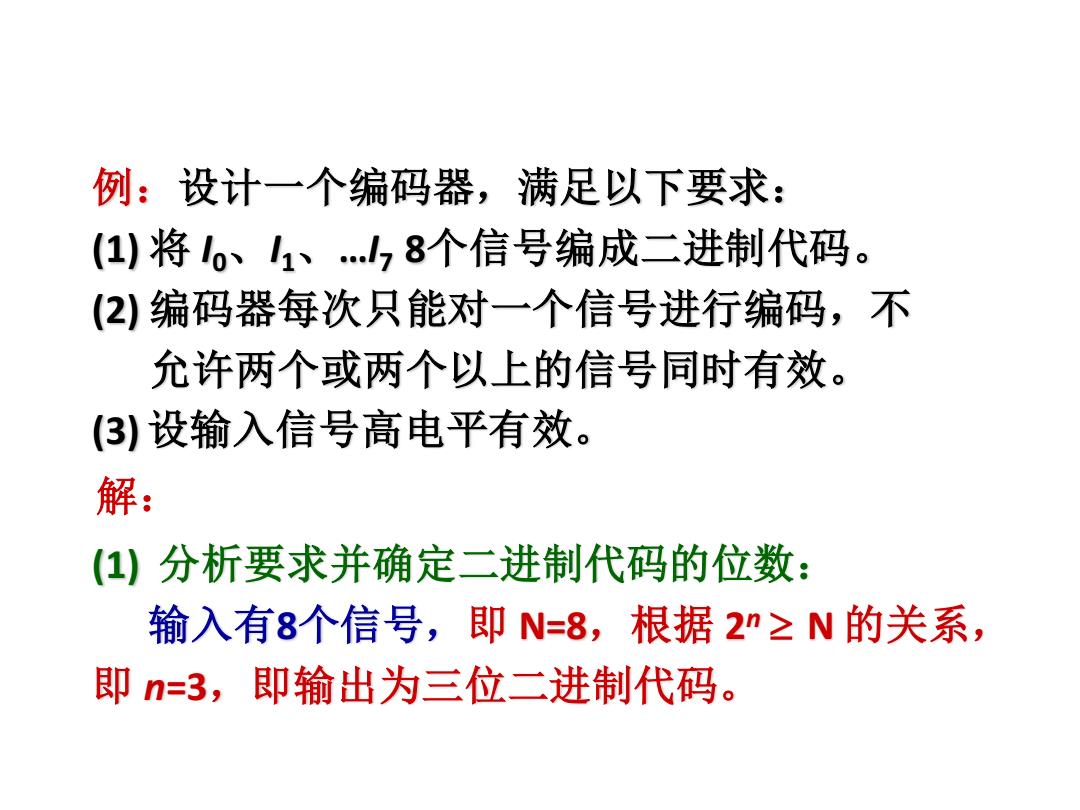

例:设计一个编码器,满足以下要求: (1)将10、11、山,8个信号编成二进制代码。 (2)编码器每次只能对一个信号进行编码,不 允许两个或两个以上的信号同时有效。 (3)设输入信号高电平有效。 解: (1)分析要求并确定二进制代码的位数: 输入有8个信号,即N=8,根据2n≥N的关系, 即n=3,即输出为三位二进制代码

(1) 分析要求并确定二进制代码的位数: 输入有8个信号,即 N=8,根据 2 n N 的关系, 即 n=3,即输出为三位二进制代码。 例:设计一个编码器,满足以下要求: (1) 将 I0、I1、…I7 8个信号编成二进制代码。 (2) 编码器每次只能对一个信号进行编码,不 允许两个或两个以上的信号同时有效。 (3) 设输入信号高电平有效。 解:

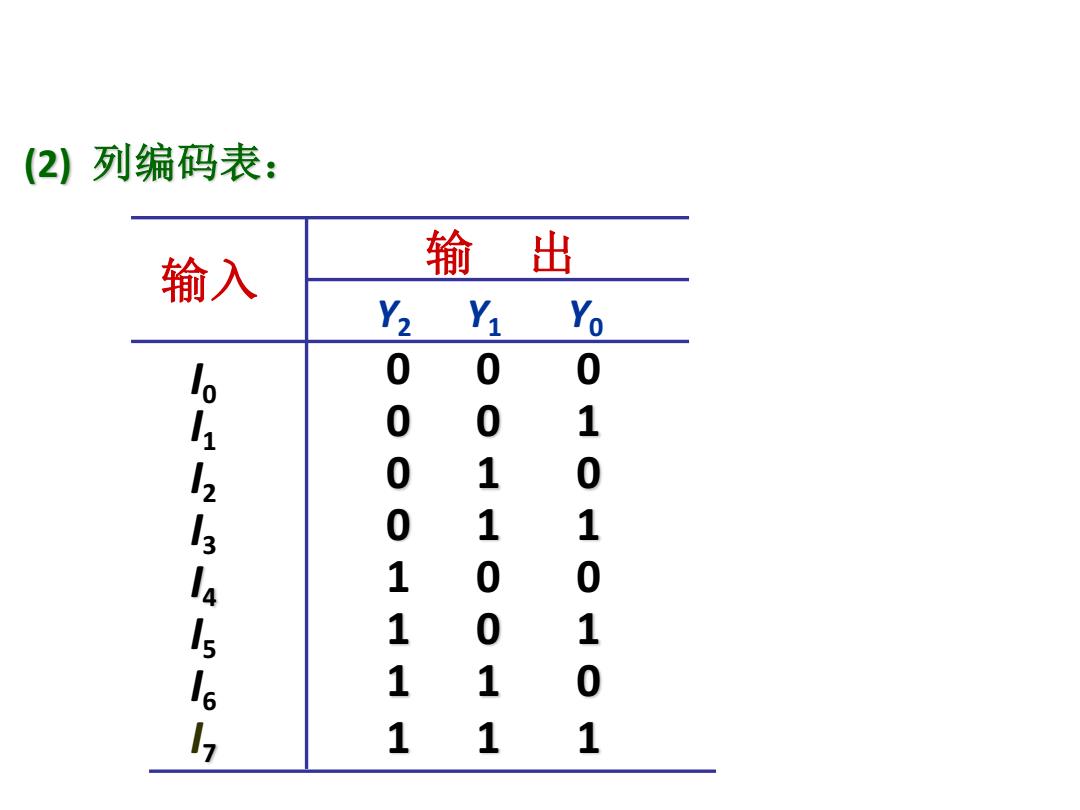

(2)列编码表: 输入 输出 Y2 Y1 Yo 1o 0 0 0 11 0 0 1 12 0 1 0 13 0 1 1 14 1 0 0 5 1 0 1 le 1 1 0 1 1 1

0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 1 0 0 1 1 0 1 1 1 I0I1I2I3I4I5I6I7 (2) 列编码表: 输入 输 出 Y2 Y1 Y0

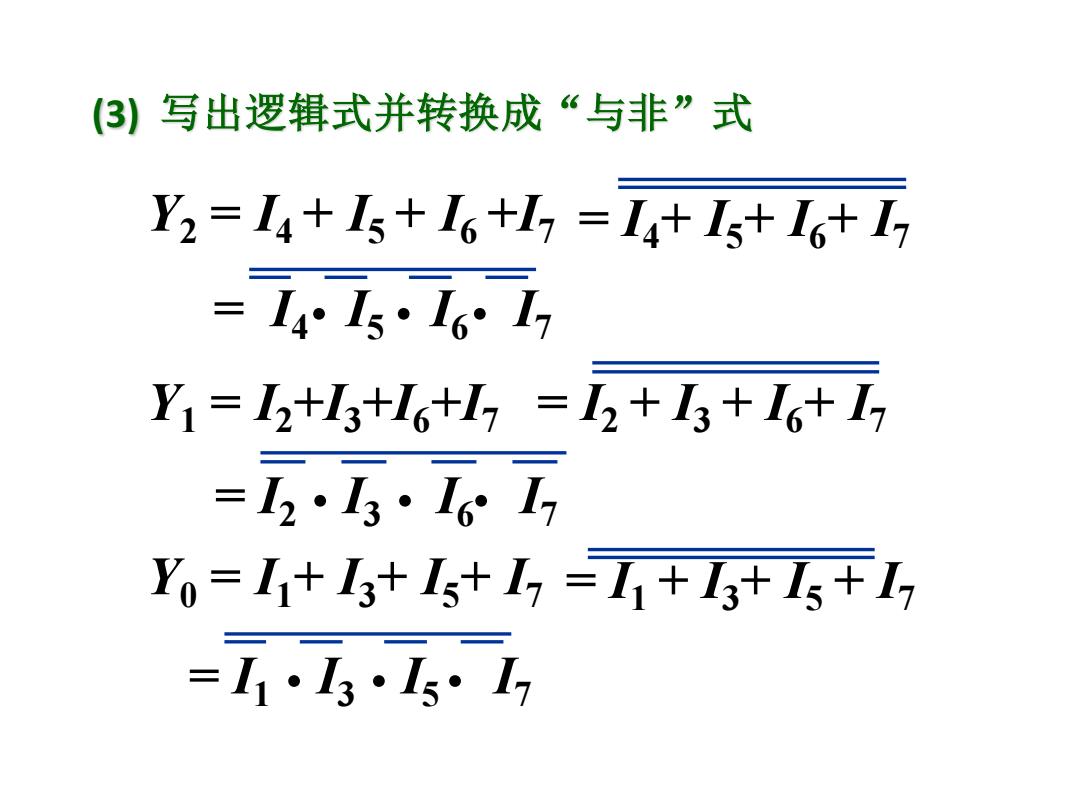

(3)写出逻辑式并转换成“与非”式 Y2=I4+I5+L6+I=I4+I5+I6+I7 =141316·77 Y1=2+l3+I6+I=2+I3+I6+I7 =2·3·16 Yo=11+3+5+I=I1+13+Is+I =L1·35·I7

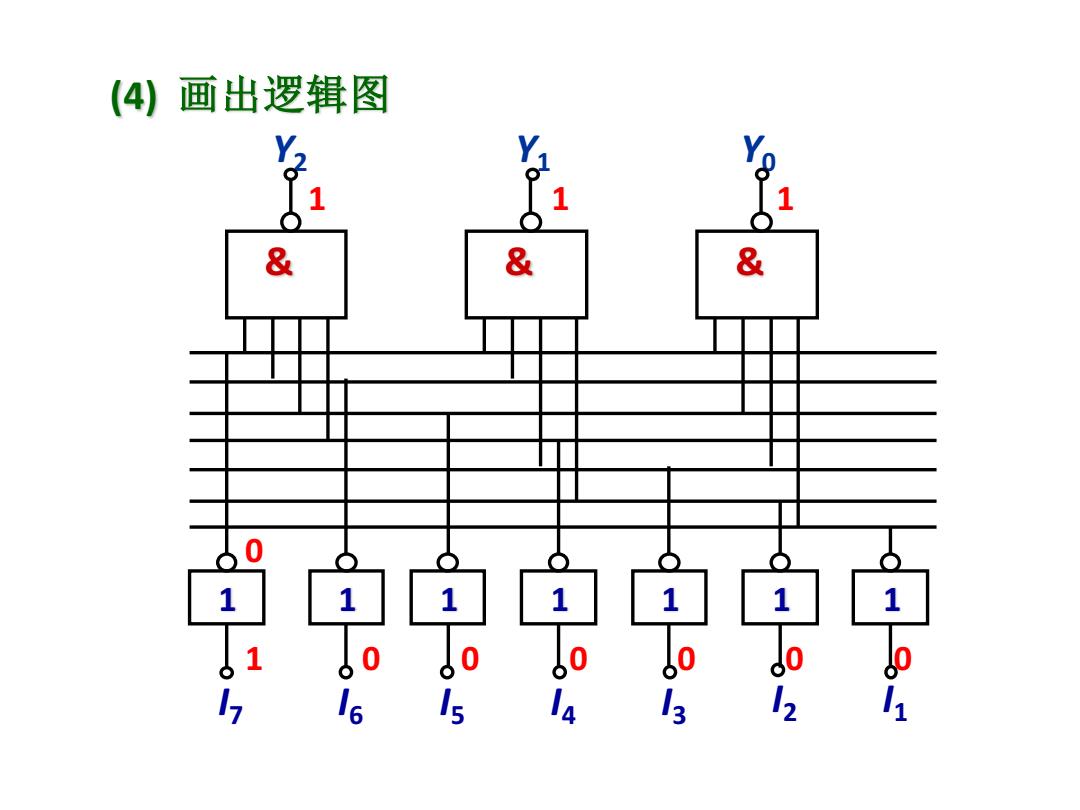

(3) 写出逻辑式并转换成“与非”式 Y2 = I4 + I5 + I6 +I7 = I4 I5 I6 I7 . . . = I4+ I5+ I6+ I7 Y1 = I2+I3+I6+I7 = I2 I3 I6 I7 . . . = I2 + I3 + I6+ I7 Y0 = I1+ I3+ I5+ I7 = I1 I3 I5 I7 . . . = I1 + I3+ I5 + I7

(4)画出逻辑图 1 & & & 0 1 1 1 1 &9 12

(4) 画出逻辑图 1 0 0 0 0 0 0 0 1 1 1 I7 I6 I5 I4 I3 I1 I2 & & & 1 1 1 1 1 1 1 Y2 Y1 Y0

二.二一十进制编码器 将十进制数0~9编成二进制代 码的电路 8421BCD码编码表 输出 输入 Y3 Y2 Y1 Yo 0(o) 0 0 0 0 列编码表: 1 ) 0 1 四位二进制代码 2 1 0 可以表示十六种 1 1 不同的状态,其 34 1 0 0 中任何十种状态 56 1 0 1 都可以表示09 1 1 0 7 1 1 1 十个数码,最常 8 1 0 0 0 用的是8421码。 9(Ug) 1 0 0 1

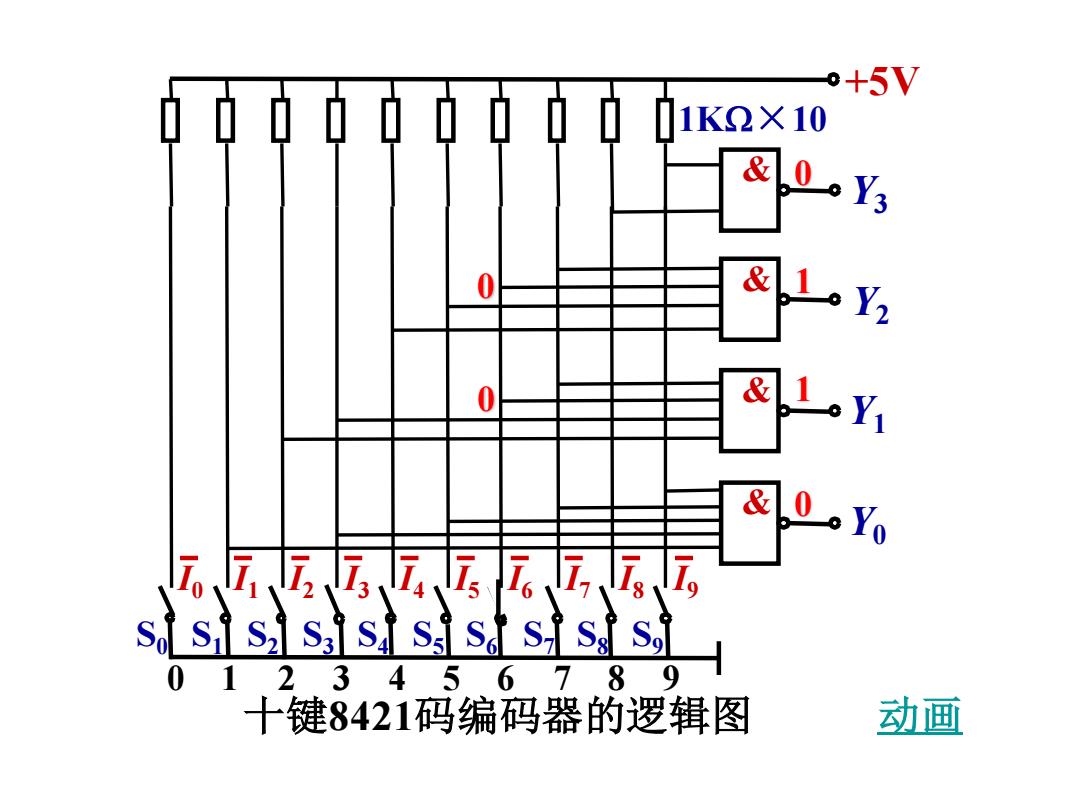

列编码表: 四位二进制代码 可以表示十六种 不同的状态,其 中任何十种状态 都可以表示0~9 十个数码,最常 用的是8421码。 8421BCD码编码表 0 0 0 输 出 输 入 Y2 Y1 Y0 0 (I0 ) 1 (I1 ) 2 (I2 ) 3 (I3 ) 4 (I4 ) 5 (I5 ) 6 (I6 ) 7 (I7 ) 8 (I8 ) 9 (I9 ) Y3 0 0 0 1 1 1 0 1 0 0 0 0 1 1 1 1 0 0 0 1 1 0 1 1 0 0 0 0 0 0 0 0 0 0 1 1 1 二. 二 – 十进制编码器 将十进制数 0~9 编成二进制代 码的电路

写出逻辑式并化成“与非”关系 Y3=Ig+Iy=Ig-I Y2=I4+I3+I。+I2=I4IL。I Y=I2+3+L6+1,=…I23L。I Y。=I1+I3+I5+I,+Ig =.I1I311,1g

写出逻辑式并化成 “与非”关系 3 8 9 8 9 Y = I + I = I .I 2 4 5 6 7 4 5 6 7 Y = I + I + I + I = I I I I 1 2 3 6 7 2 3 6 7 Y = I + I + I + I = I I I I 1 3 5 7 9 0 1 3 5 7 9 I I I I I Y I I I I I = = + + + +

+5V 11K2×10 &0。Y3 0 0 &L.Y 匠互,五五匠ZZ7 sisis sisisisisiss1 0123456789 十键8421码编码器的逻辑图 动画

十键8421码编码器的逻辑图 动画 +5V & Y3 & Y2 & Y1 & Y0 I0 I1 I2 I3 I4 I5 I6 I7 I8 I9 1K×10 S0 0 1 S1 2 S2 3 S3 4 S4 5 S5 6 S6 7 S7 8 S8 9 S9 0 0 1 1 0 0

三.优先编码器 当有两个或两个以上的信号同时输入编码电路, 电路只能对其中一个优先级别高的信号进行编码。 即允许几个信号同时有效,但电路只对其中 优先级别高的信号进行编码,而对其它优先级 别低的信号不予理睬

当有两个或两个以上的信号同时输入编码电路, 电路只能对其中一个优先级别高的信号进行编码。 即允许几个信号同时有效,但电路只对其中 优先级别高的信号进行编码,而对其它优先级 别低的信号不予理睬。 三. 优先编码器