第五章时序逻辑电路 第五章时序逻辑电路 5.1概述 5.2触发器 5.3时序逻辑电路的分析 5.4常用时序逻辑电路 5.5时序逻辑电路的设计 5.6用PLD实现时序逻辑电路

第五章 时序逻辑电路 第五章 时序逻辑电路 • 5.1 概 述 • 5.2 触发器 • 5.3 时序逻辑电路的分析 • 5.4 常用时序逻辑电路 • 5.5 时序逻辑电路的设计 • 5.6 用PLD实现时序逻辑电路

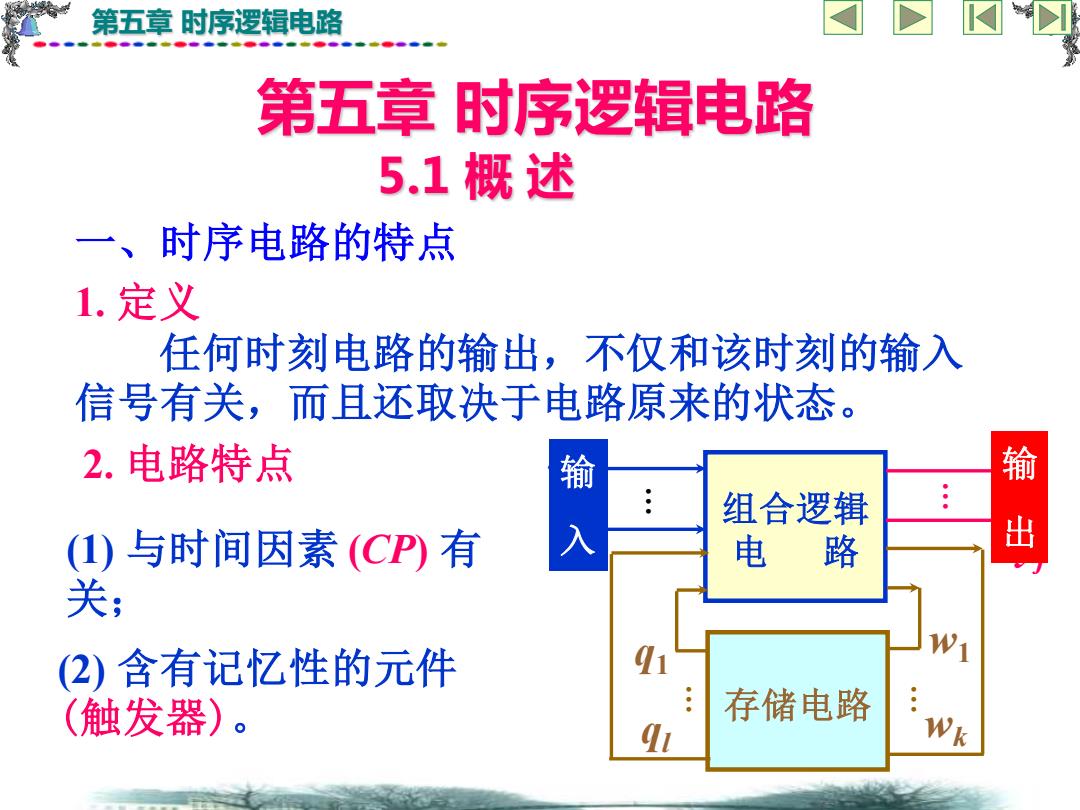

第五章时序逻辑电路 第五章时序逻辑电路 5.1概述 一、时序电路的特点 1.定义 任何时刻电路的输出,不仅和该时刻的输入 信号有关,而且还取决于电路原来的状态。 2.电路特点 输 输 : 组合逻辑 : (1)与时间因素(CP)有 电 路 出 关; (2)含有记忆性的元件 gi (触发器)。 存储电路 Wk

第五章 时序逻辑电路 5.1 概 述 一、时序电路的特点 1. 定义 任何时刻电路的输出,不仅和该时刻的输入 信号有关,而且还取决于电路原来的状态。 2. 电路特点 (1) 与时间因素 (CP) 有 关; (2) 含有记忆性的元件 (触发器)。 组合逻辑 电 路 存储电路 … … … … x1 … xi y1 … yj w1 wk q1 ql 输 入 输 出 第五章 时序逻辑电路

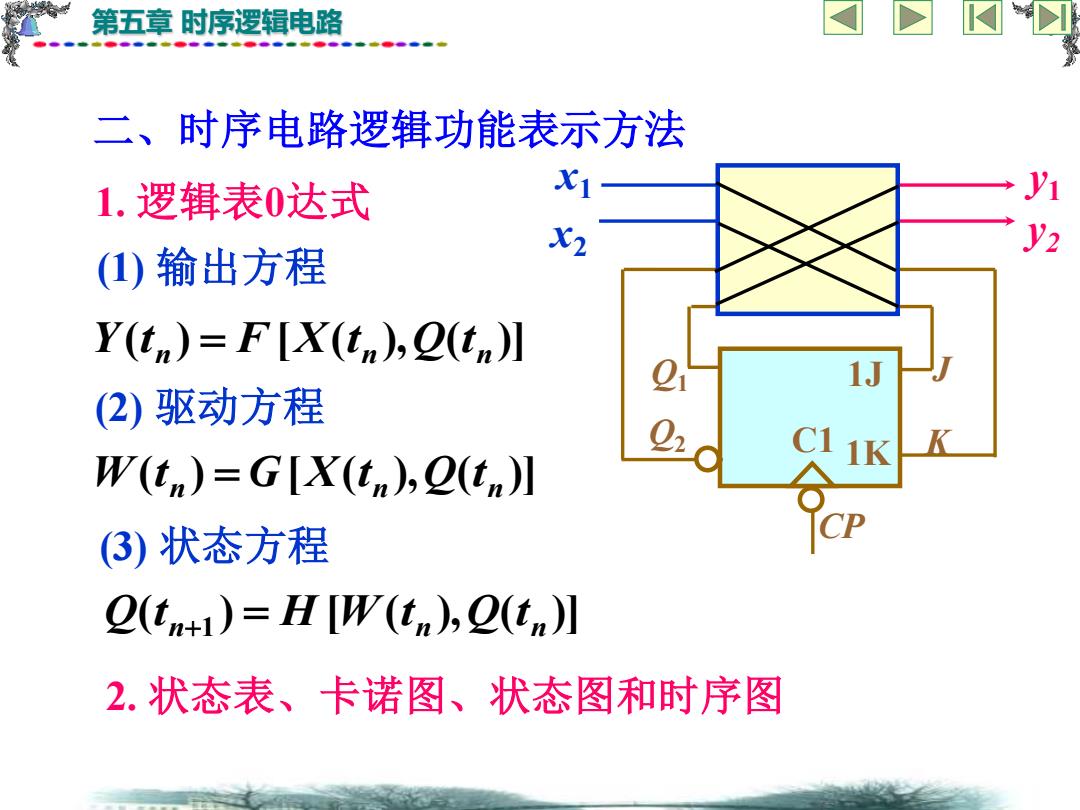

第五章时序逻辑电路 二、时序电路逻辑功能表示方法 1.逻辑表0达式 x1 X2 y2 (1)输出方程 Y(t)=F[X(t ),2(t (2)驱动方程 K w(t)=GIX(t),2(t) 3)状态方程 2(t)=HW(tn),2(tn) 2.状态表、卡诺图、状态图和时序图

第五章 时序逻辑电路 二、时序电路逻辑功能表示方法 1. 逻辑表0达式 (1) 输出方程 ( ) [ ( ), ( )] n n n Y t = F X t Q t (3) 状态方程 ( ) [ ( ), ( )] n 1 n n Q t = H W t Q t + (2) 驱动方程 ( ) [ ( ), ( )] n n n W t = G X t Q t 2. 状态表、卡诺图、状态图和时序图 组合逻辑 电 路 存储电路 … … … … x1 … xi y1 … yj w1 wk q1 ql x1 y1 y2 J K Q1 Q2 x2 1J C1 1K CP

第五章时序逻辑电路 三、时序逻辑电路分类 1.按逻辑功能划分:计数器、寄存器、读/写存储器、 顺序脉冲发生器等。 2.按时钟控制方式划分: 同步时序电路 触发器共用一个时钟CP,要更新 状态的触发器同时翻转 异步时序电路 电路中所有触发器没有共用一个CP。 3.按输出信号的特性划分: Meay型 Moore型 X(t)o 组合 Y(t) 输入 电路 输出 X(t 组合 存储 组合 电路 电路 电路 Y(t) 存储 输) 输出 电路 W CP CP Y(t )=F[(t Y(tn)=FX(tn),(tn)】

第五章 时序逻辑电路 三、时序逻辑电路分类 1. 按逻辑功能划分:计数器、寄存器、读/写存储器、 顺序脉冲发生器等。 2. 按时钟控制方式划分: 同步时序电路 触发器共用一个时钟 CP,要更新 状态的触发器同时翻转。 异步时序电路 电路中所有触发器没有共用一个 CP。 3. 按输出信号的特性划分: Moore型 ( ) [ ( )] n n Y t = F Q t Mealy型 ( ) [ ( ), ( )] n n n Y t = F X t Q t 存储 电路 Y(tn ) 输出 Q W X(tn ) 输入 组合 电路 CP Y(tn ) 输出 CP X(tn ) 输入 存储 电路 组合 电路 组合 电路

第五章时序逻辑电路 5.2 触发器 一、基本要求 1.有两个稳定的状态(0、1),以表示存储内容: 2.能够接收、保存和输出信号。 二、现态和次态 1.现态:Q”触发器接收输入信号之前的状态。 2.次态:2+1 触发器接收输入信号之后的状态。 三、分类 1.按电路结构和工作特点:基本、同步、主从和边沿。 2.按逻辑功能分:RS、JK、D和T(T)。 3.其他: TTL和CMOS,分立和集成

第五章 时序逻辑电路 一、基本要求 1. 有两个稳定的状态(0、1),以表示存储内容; 2. 能够接收、保存和输出信号。 二、现态和次态 1. 现态: 触发器接收输入信号之前的状态。 n Q 2. 次态: 触发器接收输入信号之后的状态。 n+1 Q 三、分类 1. 按电路结构和工作特点:基本、同步、主从和边沿。 2. 按逻辑功能分:RS、JK、D 和 T(T )。 3. 其他: TTL 和 CMOS,分立和集成。 5.2 触发器

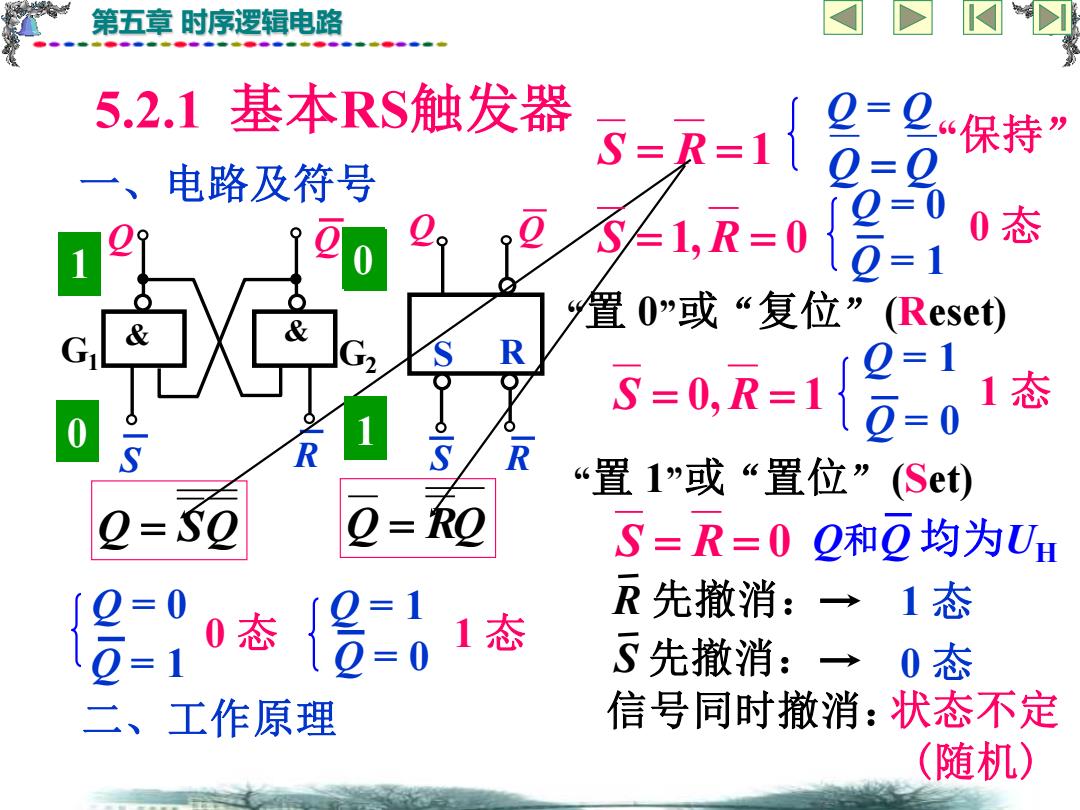

第五章时序逻辑电路 5.2.1 基本RS触发器 一、电路及符号 5-R-112 保持” 0态 0=1 y置0或“复位”(Reset) & & R 1态 R 置1”或“置位”(Set) =S2 RO S=R=02和2均为UH 810态8 R先撤消:→1态 1态 S先撤消:→0态 二、工作原理 信号同时撤消:状态不定 (随机)

第五章 时序逻辑电路 G2 5.2.1 基本RS触发器 一、电路及符号 Q G1 R & & S Q Q Q S R S R Q = SQ Q = RQ Q = 0 Q = 1 0 态 Q = 1 Q = 0 1 态 二、工作原理 S = R = 1 Q = Q Q = Q “保持” S = 1,R = 0 1 0 0 1 Q = 0 Q = 1 0 态 “置 0”或“复位”(Reset) S = 0,R = 1 0 1 1 0 Q = 1 Q = 0 1 态 “置 1”或“置位”(Set) S = R = 0 Q和Q 均为UH R 先撤消: 1 态 S 先撤消: 0 态 信号同时撤消:状态不定 (随机)

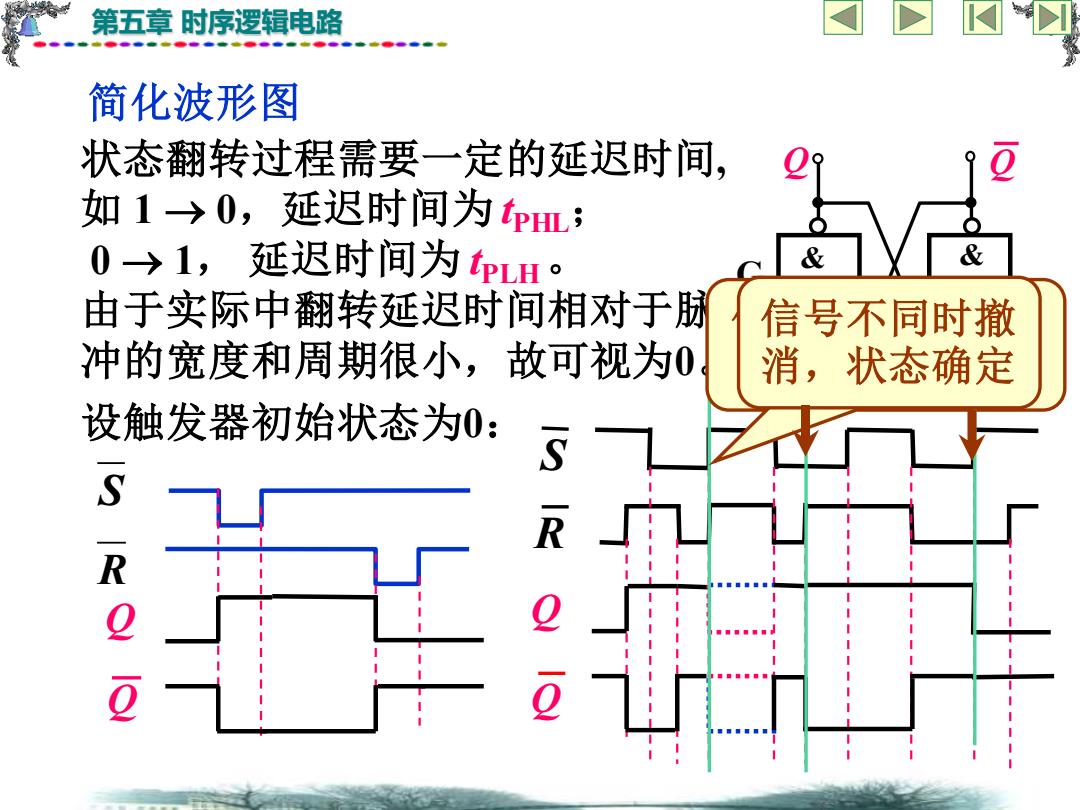

第五章时序逻辑电路 简化波形图 状态翻转过程需要一定的延迟时间, 如1→0,延迟时间为p 0→1,延迟时间为pH。 & & 由于实际中翻转延迟时间相对于脉 信号不同时撤 冲的宽度和周期很小,故可视为0 消,状态确定 设触发器初始状态为0: 5 S 反 R I

第五章 时序逻辑电路 简化波形图 状态翻转过程需要一定的延迟时间, 如 1 → 0,延迟时间为 tPHL; 0 → 1, 延迟时间为 tPLH 。 由于实际中翻转延迟时间相对于脉 冲的宽度和周期很小,故可视为0。 Q G1 R & & S Q 设触发器初始状态为0: S R Q Q S R Q Q 信号同时撤消,出 现不确定状态 信号不同时撤 消,状态确定

第五章时序逻辑电路 三、特性表和特性方程 RS n+1 1.特性表: 00 2 保持 01 1 置1 R SOn +1 0 1 0 置0 0 0 11 不用 不允许 0 0 0 3.特性方程: 0 +1 1 RS 10 0 0 00 011110 10 1 0 0 11 0 不用 111 不用 1 0 2.简化特性表 1-S+F0 RS=0约束条件

第五章 时序逻辑电路 三、特性表和特性方程 1. 特性表: R S Qn Q n+1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 1 1 1 0 0 不用 不用 2. 简化特性表 R S Q n+1 0 0 0 1 1 0 1 1 Q n 保持 1 置 1 0 置 0 不用 不允许 3. 特性方程: RS 0 1 Q n 00 01 11 10 Q n+1 0 1 1 1 0 0 Q n+1 = S + RQ n RS = 0 约束条件

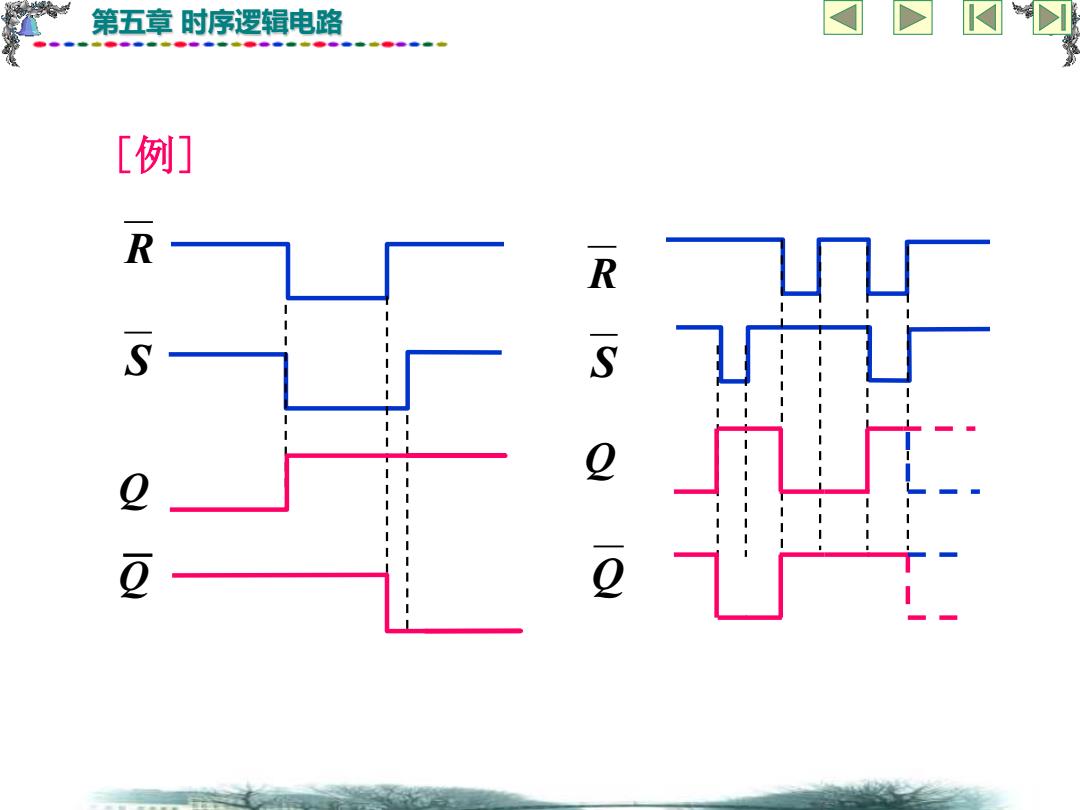

第五章时序逻辑电路 [例们 R R S n Q Q ② o 入

第五章 时序逻辑电路 [例] S R Q Q R S Q Q

第五章时序逻辑电路 四.由或非门组成RS触发器 1.电路及符号 2.工作原理 R S R R=S=0 2m+1=2”,2+1=” “保持” R=0,S=1 2+1=1,2+1=0 “置1” R=1,S=0 22+1=0,Q"+1=1 “置0” R=S=1 Qm+1、2m+均为U “不允许” 若高电平同时撤消,则状态不定

第五章 时序逻辑电路 四. 由或非门组成RS触发器 1.电路及符号 Q Q R S R S G2 Q G1 R S Q >1 >1 2.工作原理 R = S = 0 n n n n Q = Q Q = Q +1 +1 , R = 0, S = 1 1, 0 1 1 = = n+ n+ Q Q R = 1, S = 0 0, 1 1 1 = = n+ n+ Q Q R = S = 1 L 1 1 Q Q U n+ 、 n+ 均为 “保持” “置 0” “置 1” “不允许” 若高电平同时撤消,则状态不定