第六章半导体存储器 第六章半导体存储器 6.1概述 6.2顺序存取存储器 SAM 6.3随机存取存储器(RAM) 6.4只读存储器(ROM)

第六章 半导体存储器 第六章 半导体存储器 • 6.1 概述 • 6.2 顺序存取存储器( SAM) • 6.3 随机存取存储器( RAM) • 6.4 只读存储器(ROM)

第六章半导体存储器 第六章半导体存储器 6.1概述 存储器是存储信息的器件,主要用来存放二进制数 据、程序和信息,是计算机等数字系统中不可缺少的组 成部分。 6.1.1半导体存储器的特点 集成度高,体积小 可靠性高,价格低 外围电路简单易于批量生产

第六章 半导体存储器 第六章 半导体存储器 6.1 概述 存储器是存储信息的器件,主要用来存放二进制数 据、程序和信息,是计算机等数字系统中不可缺少的组 成部分。 6.1.1 半导体存储器的特点 集成度高,体积小 可靠性高,价格低 外围电路简单易于批量生产

第六章半导体存储器 6.1.2半导体存储器的分类 按存取功能,半导体存储器可分为: 只读存储器ROM(Read-only memory) 随机存取存储器RAM(Random access memory) 顺序存取存储器SAM(Sequential access memory)。 按器件类型,半导体存储器可分为: 双极型存储器和MOS型存储器

第六章 半导体存储器 6.1.2 半导体存储器的分类 按存取功能,半导体存储器可分为: 顺序存取存储器SAM(Sequential access memory)。 按器件类型,半导体存储器可分为: 双极型存储器和MOS型存储器 只读存储器ROM(Read-only memory ) 随机存取存储器RAM(Random access memory)

第六章半导体存储器 6.2顺序存取存储器(SAM) SAM是一种按顺序串行地写入或读出 的存储器,也成为串行存储器,由于SAM 的数据是按一定顺序串行写入或读出,所以 它实质上就是移位寄存器。 SAM按数据读出的顺序分为先入先出和 先入后出型

第六章 半导体存储器 6.2 顺序存取存储器( SAM) SAM 是一种按顺序串行地写入或读出 的存储器,也成为串行存储器,由于SAM 的数据是按一定顺序串行写入或读出,所以 它实质上就是移位寄存器。 SAM按数据读出的顺序分为先入先出和 先入后出型

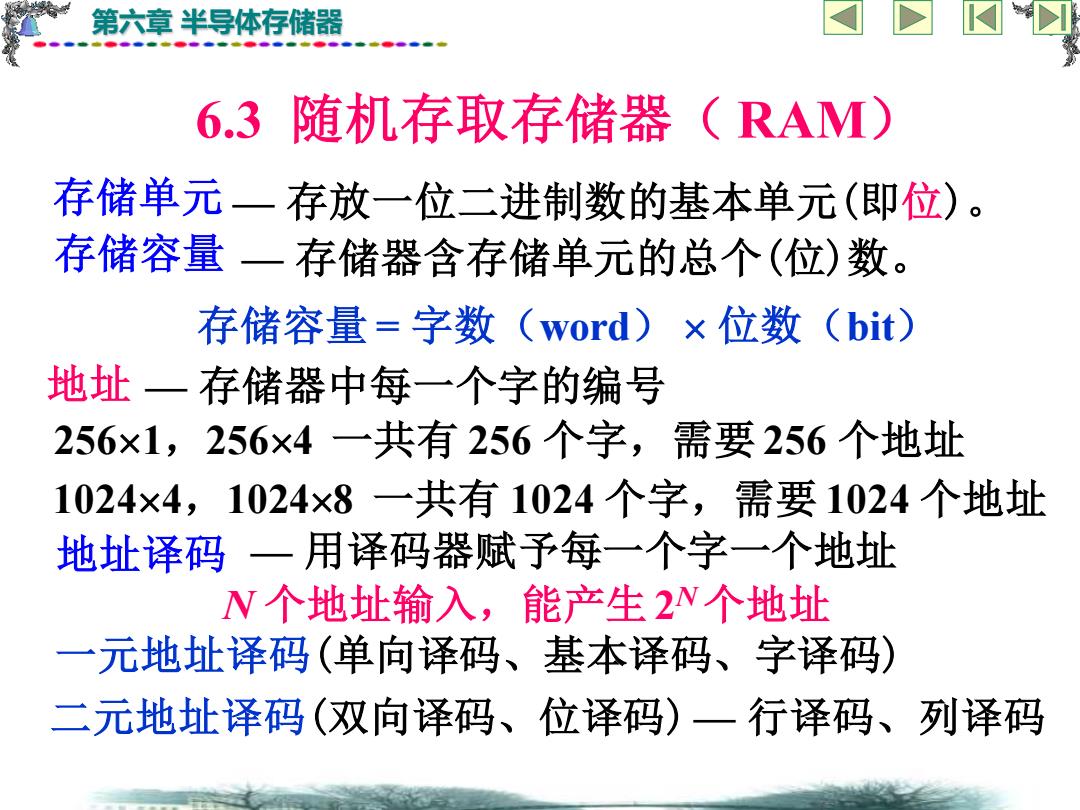

第六章半导体存储器 6.3随机存取存储器(RAM) 存储单元一存放一位二进制数的基本单元(即位)。 存储容量一存储器含存储单元的总个(位)数。 存储容量=字数(word)×位数(bit) 地址一存储器中每一个字的编号 256×1,256×4一共有256个字,需要256个地址 1024×4,1024× 3一共有1024个字,需要1024个地址 地址译码一用译码器赋予每一个字一个地址 N个地址输入,能产生2N个地址 一元地址译码(单向译码、基本译码、字译码) 二元地址译码(双向译码、位译码)一行译码、列译码

第六章 半导体存储器 6.3 随机存取存储器( RAM) 存储单元 — 存放一位二进制数的基本单元(即位)。 存储容量 — 存储器含存储单元的总个(位)数。 存储容量 = 字数(word) 位数(bit) 地址 — 存储器中每一个字的编号 2561,2564 一共有 256 个字,需要 256 个地址 10244,10248 一共有 1024 个字,需要 1024 个地址 地址译码 — 用译码器赋予每一个字一个地址 N 个地址输入,能产生 2 N 个地址 一元地址译码(单向译码、基本译码、字译码) 二元地址译码(双向译码、位译码) — 行译码、列译码

第六章半导体存储器 6.3.1RAM的结构与工作原理 地 地址码输入1SF : 址译码器 存储矩阵 R/) 读/写 控制器

第六章 半导体存储器 6.3.1 RAM 的结构与工作原理 … 存储矩阵 读/写 控制器 地 址 译 码 器 … 地 址 码 输 入 片选 读/写控制 输入/输出 CS R / W I / O

第六章半导体存储器 [例]对256×4存储矩阵进行地址译码 元地址译码 二元地址译码 0 1 译码器 010 0 行译码器 out W256 0111 X15 8线一 256线 1 0 0 4线一-16线 列译码器 缺点: 10.. 0 n位地址输入的 8位地址输入的 译码器,需要2n条 地址译码器,只有32 输出线。 条输出线

第六章 半导体存储器 [例] 对 256 4 存储矩阵进行地址译码 一元地址译码 … … … D3D2D1D0 W0 W1 W256 译 码 器 0 0 1 1 1 0 1 0 0 1 1 1 A0 A1 A7 1 0 . . . 0 W1 1 0 1 0 8线 — 256线 缺点: n 位地址输入的 译码器,需要 2 n 条 输出线。 1 0 1 0 二元地址译码 Y0Y1 Y15 … A0 A1 A2 A3 X0 X1 X15 行 译 码 器 A4 A5 A6 A7 … 列译码器 Dout 4线 —16线 1 0 . . . 0 1 0 … 0 8 位地址输入的 地址译码器,只有 32 条输出线

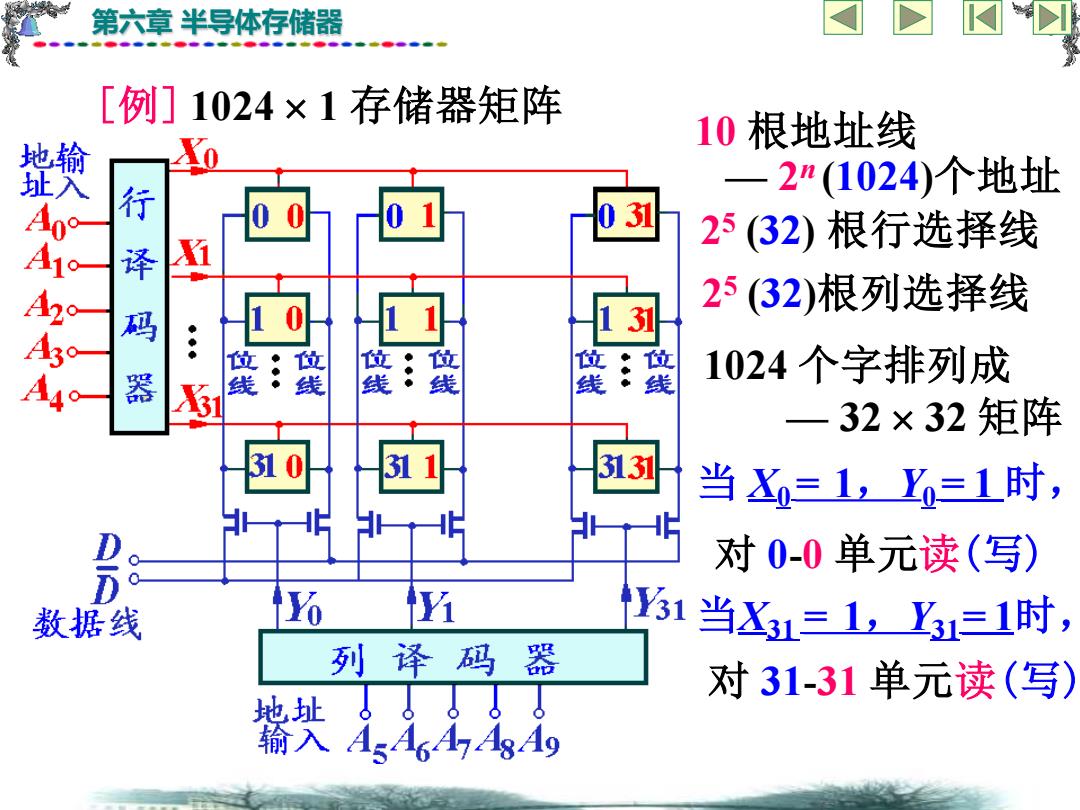

第六章半导体存储器 [例]1024×1存储器矩阵 10根地址线 紫 一 2"(1024)个地址 0 行译码器 0 25(32)根行选择线 10 25(32)根列选择线 131 位位 位: 1024个字排列成 1 线· 线 一32×32矩阵 3131 当X=1,Y=1时, 对0-0单元读(写) D 数据 i 1 当X1=1,Y1=1时, 列译码器 对31-31单元读(写) 地址。。。。。 输入AsA64gA9

第六章 半导体存储器 2 5 (32) 根行选择线 10 根地址线 — 2 n (1024)个地址 2 5 (32)根列选择线 1024 个字排列成 — 32 32 矩阵 当 X0= 1,Y0= 1 时, 对 0-0 单元读(写) 当X31 = 1,Y31= 1时, 对 31-31 单元读(写) [例] 1024 1 存储器矩阵

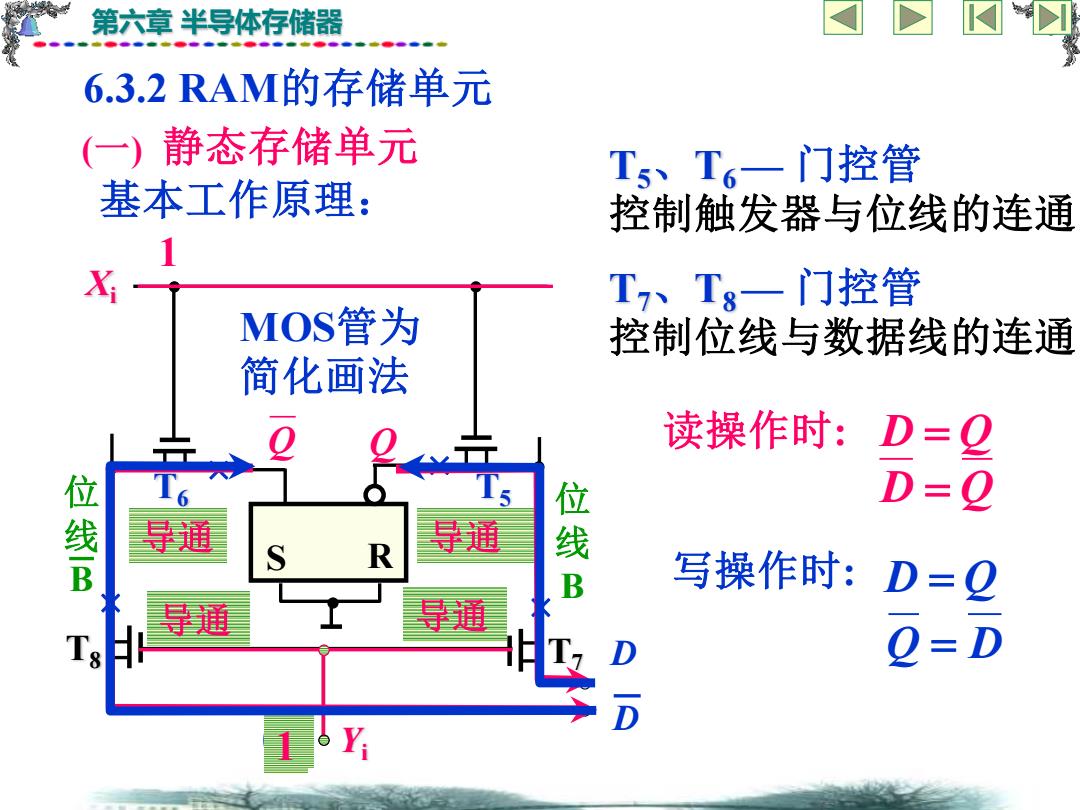

第六章半导体存储器 6.3.2RAM的存储单元 (一)静态存储单元 T5、T6一门控管 基本工作原理: 控制触发器与位线的连通 1 X T、T8一门控管 MOS管为 控制位线与数据线的连通 简化画法 读操作时: D= 位 D= 位线B Q 导通 导通 线 B 写操作时:D=2 导通 导通 O=D 16

第六章 半导体存储器 6.3.2 RAM的存储单元 (一) 静态存储单元 基本工作原理: T6 T5 T8 T7 D D Xi Yi S R Q Q 位 线 B 位 线 B T5、T6— 门控管 控制触发器与位线的连通 截止 截止 导通 导通 0 截止 截止 10 导通 导通 读操作时: D = Q D = Q 写操作时: D = Q Q = D T7、T8— 门控管 控制位线与数据线的连通 010 MOS管为 简化画法

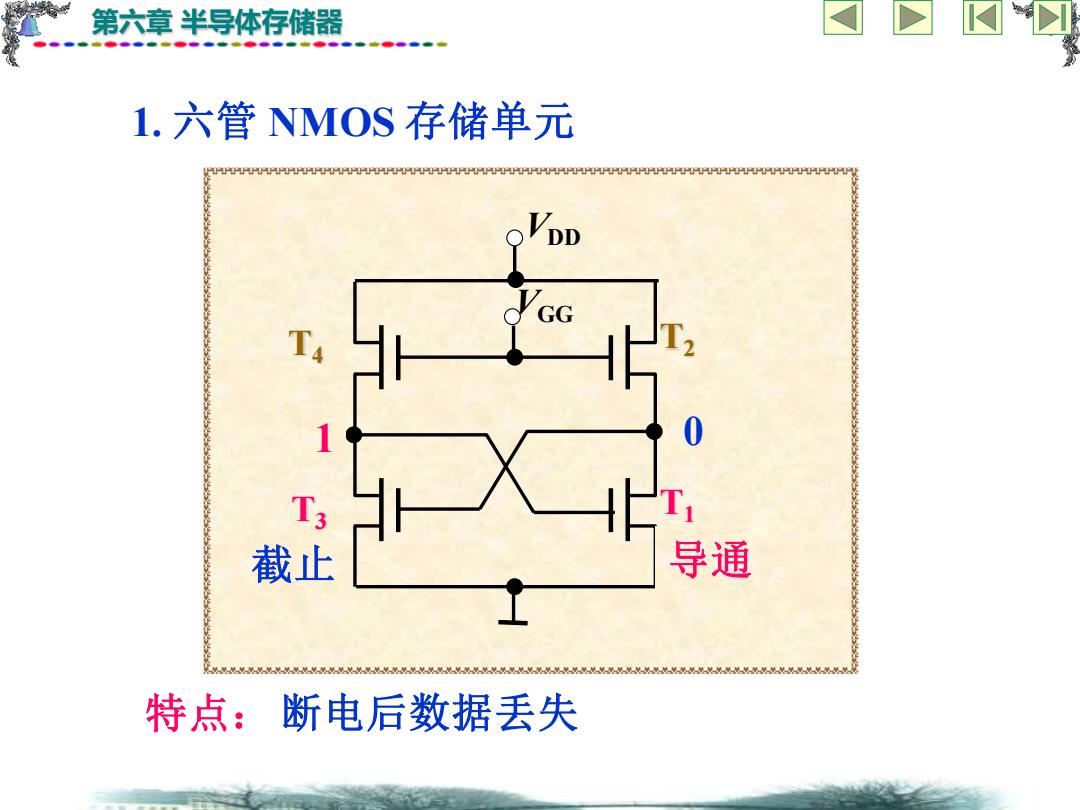

第六章半导体存储器 1.六管NMOS存储单元 DD G T 0 T; HE 截止 导通 特点:断电后数据丢失

第六章 半导体存储器 T3 T1 T4 T2 T6 T5 T8 T7 VDD VGG D D Xi Yi 1. 六管 NMOS 存储单元 基本RS 触发器 T T1 3 T T2 4 VDD VGG 1 导通 0 截止 0 截止 1 导通 特点: 断电后数据丢失