第十章 常用时序逻辑电路及其应用 10.1寄存器 寄存器是数字系统常用的逻辑部件,它用来存放 数码或指令等。它由触发器和门电路组成。一个触 发器只能存放一位二进制数,存放位二进制时, 要n个触发器。 数码寄存器 按功能分 移位寄存器

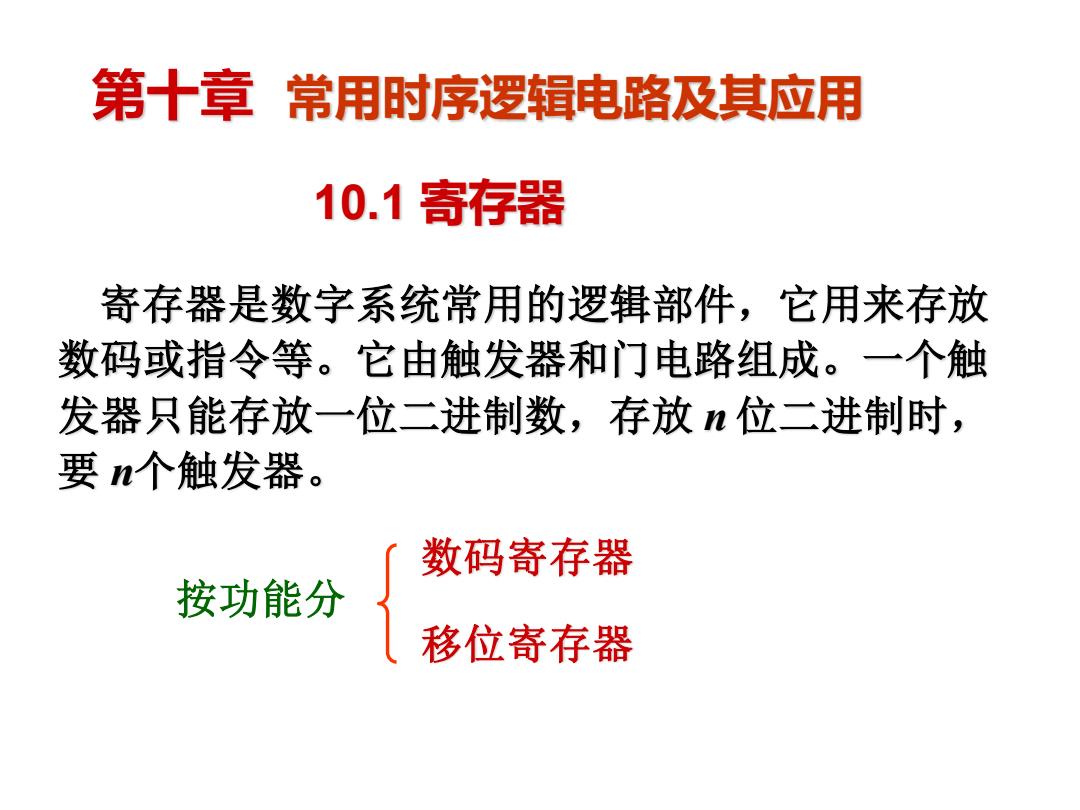

10.1 寄存器 寄存器是数字系统常用的逻辑部件,它用来存放 数码或指令等。它由触发器和门电路组成。一个触 发器只能存放一位二进制数,存放 n 位二进制时, 要 n个触发器。 按功能分 数码寄存器 移位寄存器 第十章 常用时序逻辑电路及其应用

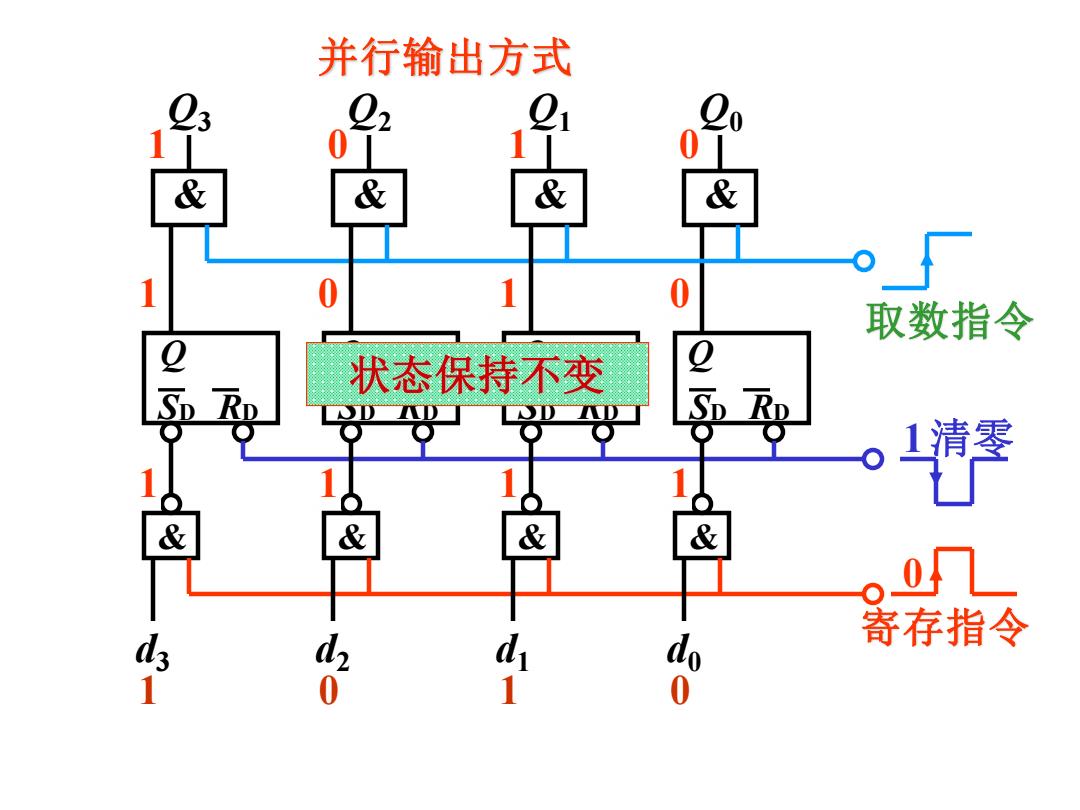

并行输出方式 0 & & & & 0 1 0 取数指令 状态保持不变 。1清墨 & & & & o0几 寄存指令 41 d do 0

SD RD d3 SD RD d2 SD RD d1 SD RD d0 1 0 清零 1 0 1 0 寄存指令 & Q0 & Q1 & Q2 & Q3 取数指令 1 0 1 0 并行输出方式 & & & & Q Q Q Q 0 0 0 0 0 1 0 1 状态保持不变 1 0 1 0 1 1 1 1

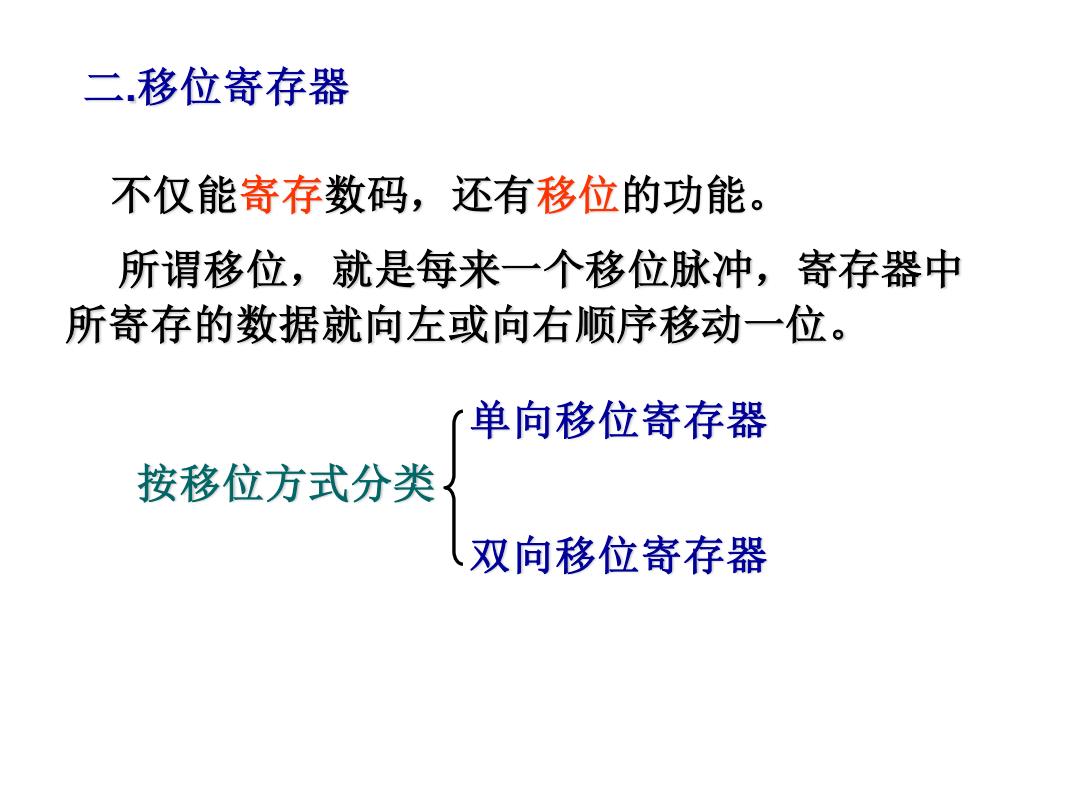

二.移位寄存器 不仅能寄存数码,还有移位的功能。 所谓移位,就是每来一个移位脉冲,寄存器中 所寄存的数据就向左或向右顺序移动一位。 单向移位寄存器 按移位方式分类 双向移位寄存器

二.移位寄存器 不仅能寄存数码,还有移位的功能。 所谓移位,就是每来一个移位脉冲,寄存器中 所寄存的数据就向左或向右顺序移动一位。 按移位方式分类 单向移位寄存器 双向移位寄存器

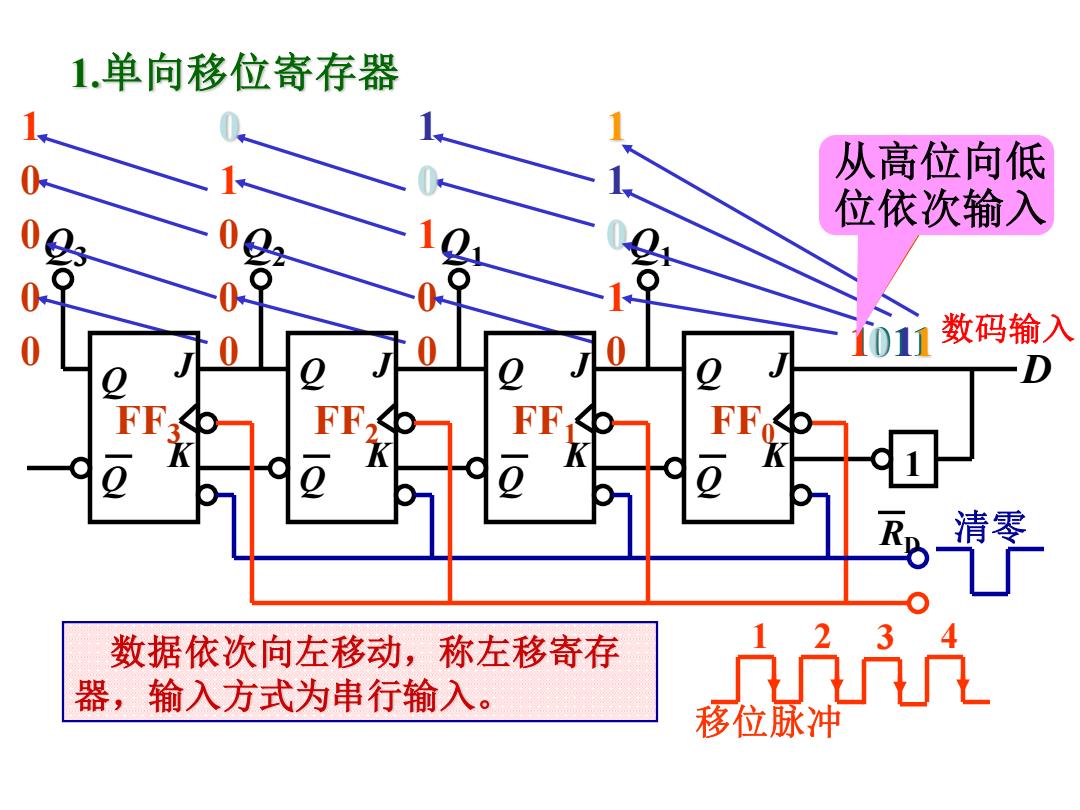

1.单向移位寄存器 从高位向低 位依次输入 101 数码输入 风清零 数据依次向左移动,称左移寄存 器,输入方式为串行输入。 移位脉冲

寄存数码 1.单向移位寄存器 清零 D 1 移位脉冲 2 3 4 1011 1 Q Q3 Q2 Q1 RD 0 0 0 0 0 0 0 1 0 0 1 0 1 0 1 1 0 1 0 1 1011 0 Q J K FF0 Q1 Q J K FF2 Q J K FF1 Q J K FF3 数据依次向左移动,称左移寄存 器,输入方式为串行输入。 Q Q Q 从高位向低 位依次输入 数码输入

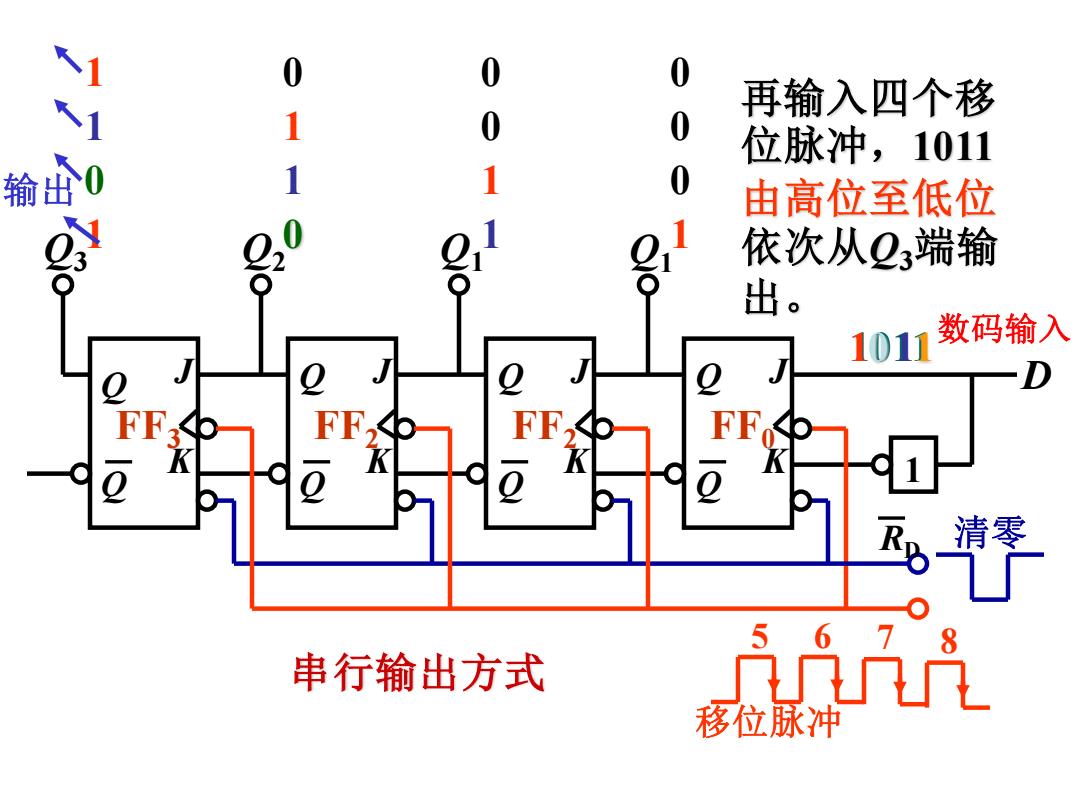

0 0 0 再输入四个移 1 0 0 位脉冲,1011 1 0 由高位至低位 g 依次从Q3端输 出。 1011 数码输入 清零 5678 串行输出方式 六几u 移位脉冲

1 0 1 1 0 1 1 0 1 1 0 0 1 0 0 0 输出 再输入四个移 位脉冲,1011 由高位至低位 依次从Q3端输 出。 串行输出方式 清零 D 1011 1 Q Q3 Q2 Q1 RD 1011 0 Q J K FF0 Q1 Q J K FF2 Q J K FF2 Q J K FF3 Q Q Q 5 移位脉冲 6 7 8 数码输入

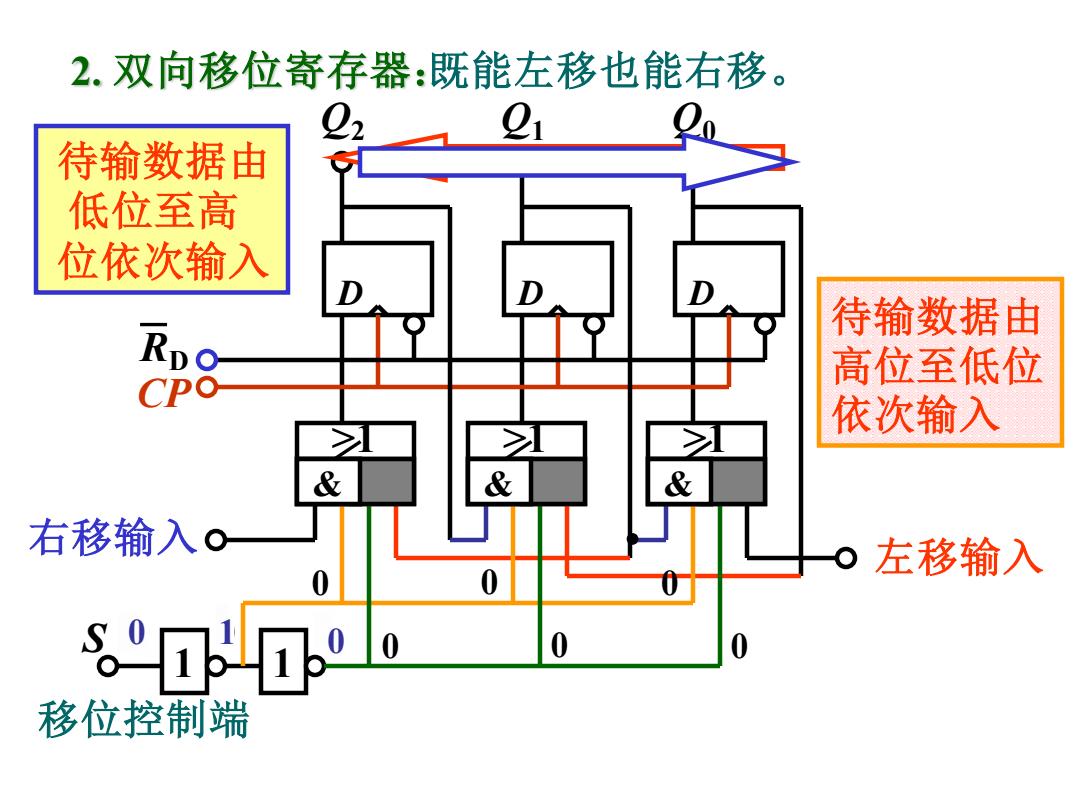

2.双向移位寄存器:既能左移也能右移。 21 待输数据由 低位至高 位依次输入 待输数据由 88 高位至低位 依次输入 & & & 右移输入0 左移输入 8 0 移位控制端

2. 双向移位寄存器:既能左移也能右移。 D Q2 D Q1 D Q0 >1 & 1 1 >1 & >1 & . RD CP S 左移输入 待输数据由 低位至高 位依次输入 待输数据由 高位至低位 依次输入 1 0 1 右移输入 移位控制端 0 0 0 0 0 0 & & & & & & 0 0 1

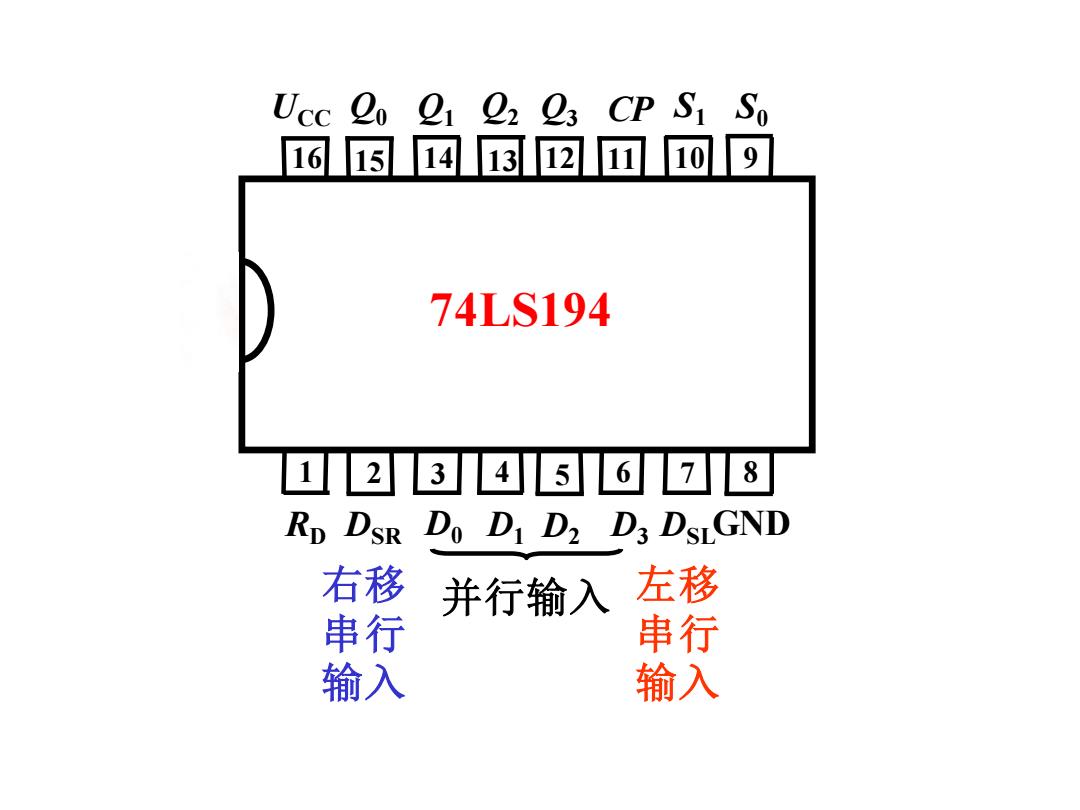

Ucc 2021 22 23 CP S1 So 16151413121团109 74LS194 12345678 RD DSR Do D1 D2 D3 DSLGND 右移 我我 并行输入 左移 串行 输入

右移 串行 输入 左移 串行 输入 UCC Q0 Q1 Q2 Q3 CP S1 S0 16 15 14 13 12 11 10 9 1 2 3 4 5 6 7 8 RD DSR D0 D1 D2 D3 DSLGND 74LS194 并行输入

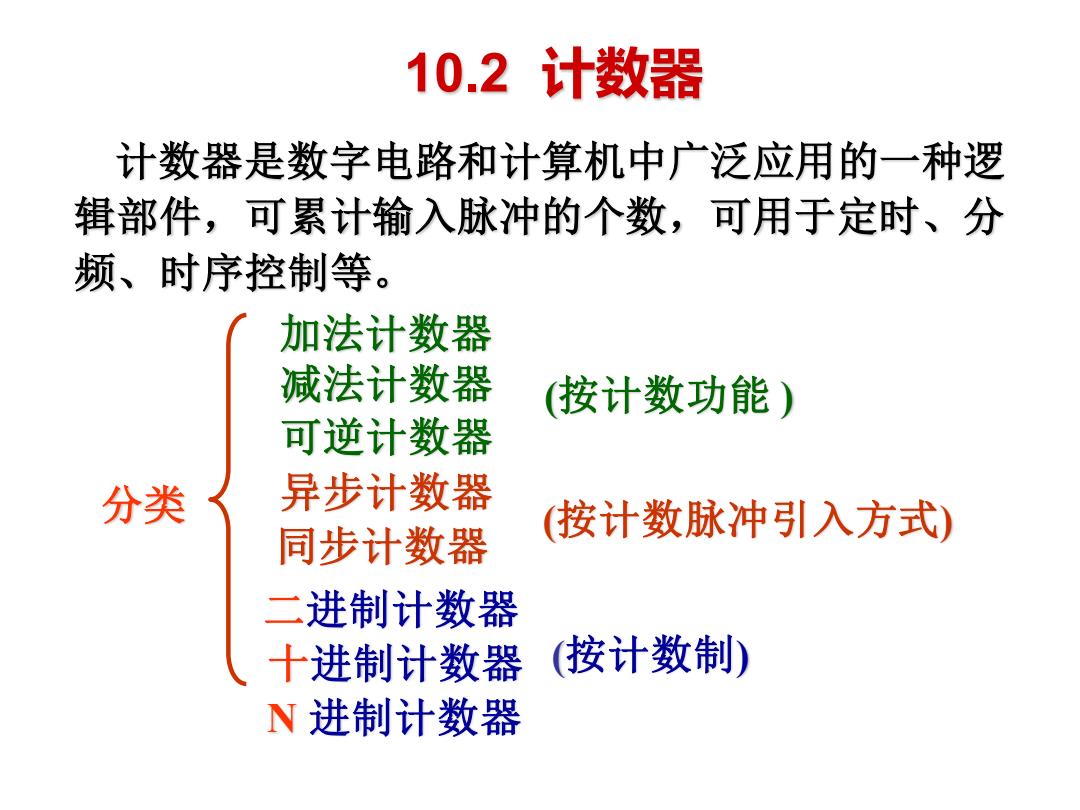

10.2计数器 计数器是数字电路和计算机中广泛应用的一种逻 辑部件,可累计输入脉冲的个数,可用于定时、分 频、时序控制等。 加法计数器 减法计数器 按计数功能) 可逆计数器 分类 异步计数器 按计数脉冲引入方式) 同步计数器 二进制计数器 十进制计数器 (按计数制) N进制计数器

10.2 计数器 计数器是数字电路和计算机中广泛应用的一种逻 辑部件,可累计输入脉冲的个数,可用于定时、分 频、时序控制等。 分类 加法计数器 减法计数器 可逆计数器 (按计数功能 ) 异步计数器 同步计数器 (按计数脉冲引入方式) 二进制计数器 十进制计数器 N 进制计数器 (按计数制)

一.二进制计数器 按二进制的规律累计脉冲个数,它也是构成其 它进制计数器的基础。要构成位二进制计数器, 需用n个具有计数功能的触发器。 同步计数器:计数脉冲同时接到各位触发器,各触 发器状态的变换与计数脉冲同步。 异步计数器:计数脉冲只加在一个触发器的CP端, 其他各触发器的CP脉冲,均由相邻触发器的输出提 供,各触发器状态的变换有先有后

一. 二进制计数器 按二进制的规律累计脉冲个数,它也是构成其 它进制计数器的基础。要构成 n位二进制计数器, 需用 n个具有计数功能的触发器。 同步计数器:计数脉冲同时接到各位触发器,各触 发器状态的变换与计数脉冲同步。 异步计数器:计数脉冲只加在一个触发器的CP端, 其他各触发器的CP脉冲,均由相邻触发器的输出提 供,各触发器状态的变换有先有后

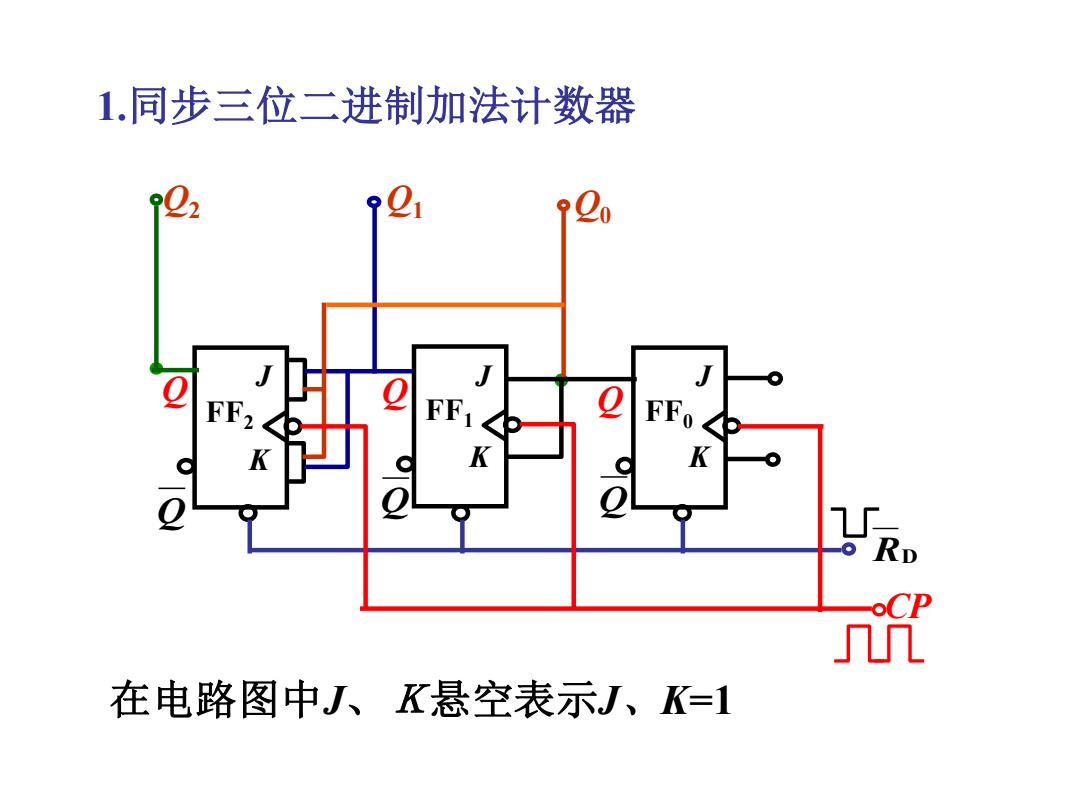

1.同步三位二进制加法计数器 ?C. 0 FF, FF FF。 K 在电路图中J、K悬空表示J、K=1

1.同步三位二进制加法计数器 Q Q FF2 Q Q FF1 Q Q FF0 Q2 Q1 Q0 RD CP J K J K J K 在电路图中J、K悬空表示J、K=1