触发器和时序逻辑电路

触发器和时序逻辑电路

一.什么是触发器 触发器应具有两个 具有二个稳定状态: 能够存贮一位二值 “0”状态和“1”状 (逻辑0和逻辑器1) 态(分别对应逻辑0 信号的基本单元电路 和逻辑1); 统称为触发器 另外,它还必须具有保存和修改功能 可通过基本RS触发器来理解

一.什么是触发器 另外,它还必须具有保存和修改功能 能够存贮一位二值 (逻辑0和逻辑器1) 信号的基本单元电路, 统称为触发器 触发器应具有两个 具有二个稳定状态: “0”状态和“1”状 态(分别对应逻辑0 和逻辑1); 可通过基本RS触发器来理解

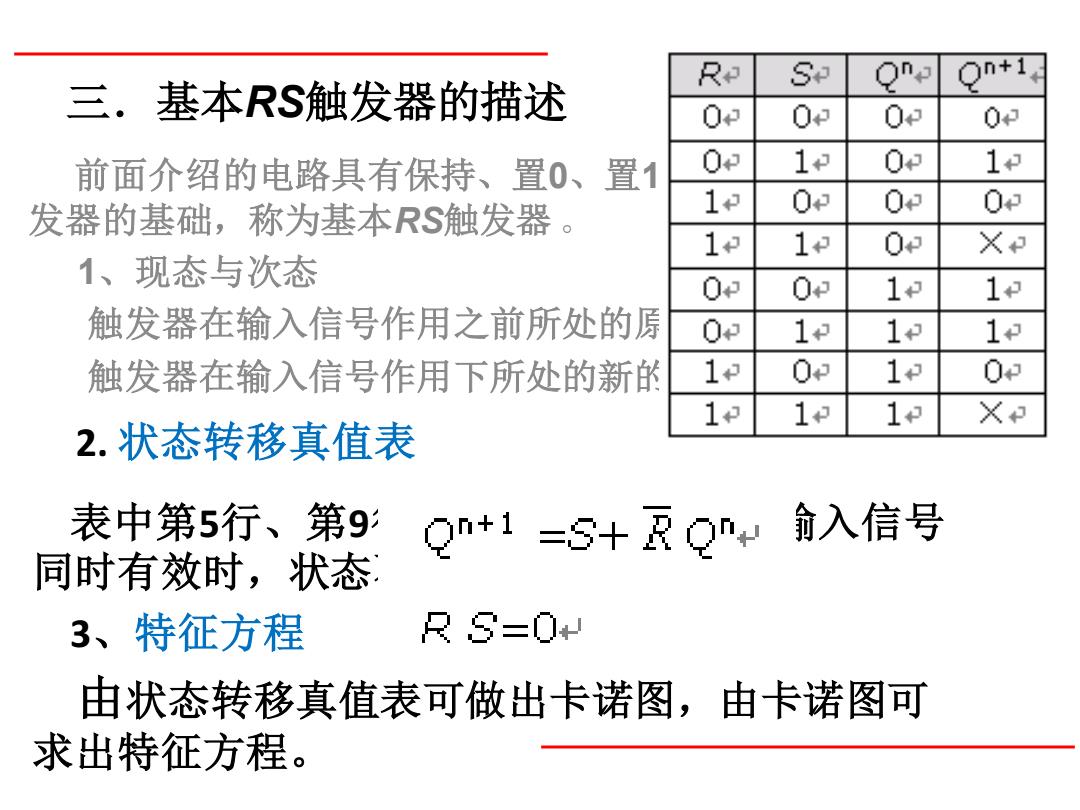

R S Qne On+1 三.基本RS触发器的描述 0p 0 0p 0 前面介绍的电路具有保持、置0、置1 0 1 0 1 发器的基础,称为基本RS触发器 1 0 0 0 1 0 ×和 1、现态与次态 0 0 1 1 触发器在输入信号作用之前所处的厚 1 1 1 触发器在输入信号作用下所处的新的 1 0 1 0 1 1 1 X 2.状态转移真值表 表中第5行、第9 Qn+1 =5+RQn 俞入信号 同时有效时,状态 3、特征方程 RS=0+ 由状态转移真值表可做出卡诺图,由卡诺图可 求出特征方程

三.基本RS触发器的描述 前面介绍的电路具有保持、置0、置1功能,是组成其它触 发器的基础,称为基本RS触发器 。 1、现态与次态 触发器在输入信号作用之前所处的原稳定状态称为现态; 触发器在输入信号作用下所处的新的状态称为次态 2. 状态转移真值表 表中第5行、第9行的“×”表示当两个输入信号 同时有效时,状态不定。 3、特征方程 由状态转移真值表可做出卡诺图,由卡诺图可 求出特征方程

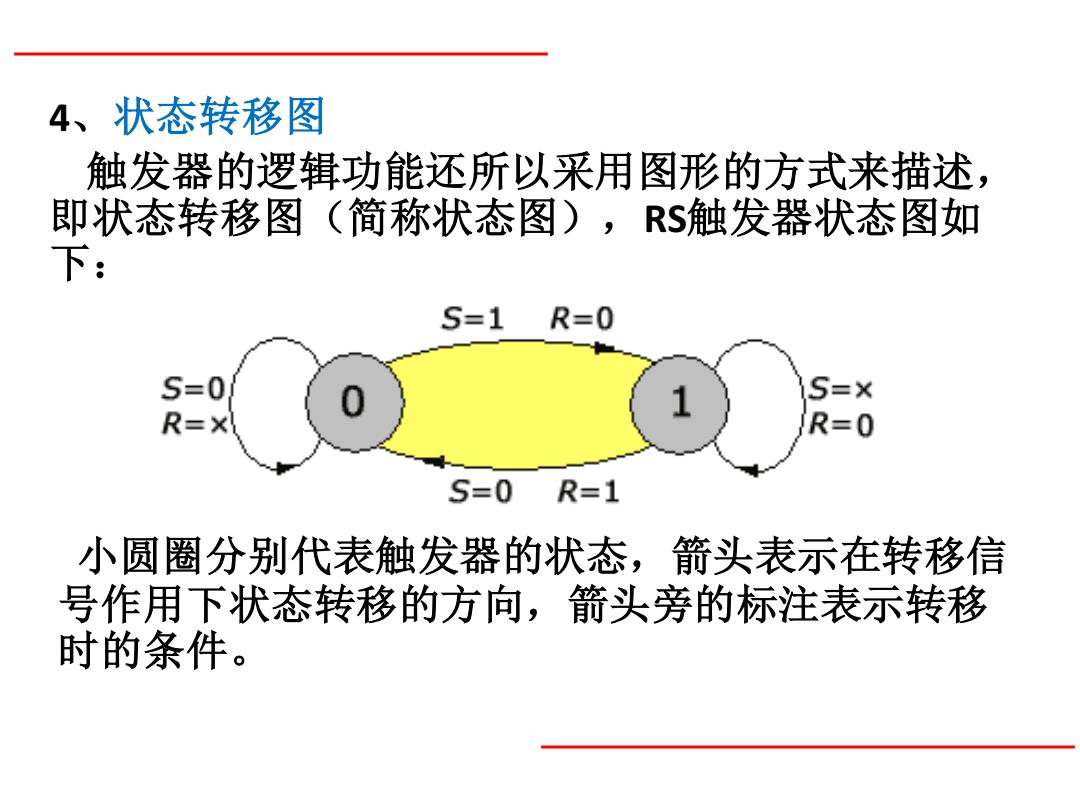

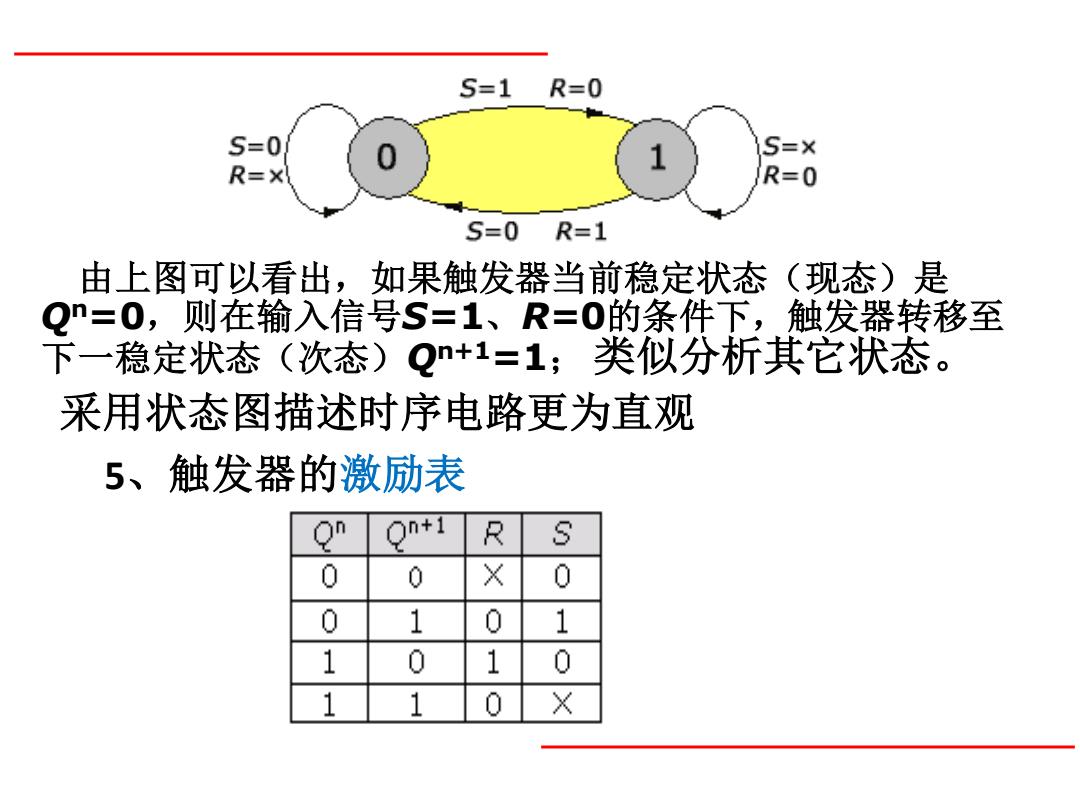

4、状态转移图 触发器的逻辑功能还所以采用图形的方式来描述, 即状态转移图(简称状态图),S触发器状态图如 下: S=1 R=0 S=0 S=x R=x R=0 S=0 R=1 小圆圈分别代表触发器的状态,箭头表示在转移信 号作用下状态转移的方向,箭头旁的标注表示转移 时的条件

4、状态转移图 触发器的逻辑功能还所以采用图形的方式来描述, 即状态转移图(简称状态图),RS触发器状态图如 下: 小圆圈分别代表触发器的状态,箭头表示在转移信 号作用下状态转移的方向,箭头旁的标注表示转移 时的条件

S=1R=0 S=0 S=x R=x 0 1 R=0 S=0R=1 由上图可以看出,如果触发器当前稳定状态 (现态)是 Q=0,则在输入信号S=1、R=0的条件下,触发器转移至 下一稳定状态(次态)Qn+1=1;类似分析其它状态。 采用状态图描述时序电路更为直观 5、触发器的激励表 On on+1 R S 0 X 0 0 1 0 1 1 0 1 0 1 1 0 ×

5、触发器的激励表 由上图可以看出,如果触发器当前稳定状态(现态)是 Qn=0,则在输入信号S=1、R=0的条件下,触发器转移至 下一稳定状态(次态)Qn+1=1; 类似分析其它状态。 采用状态图描述时序电路更为直观

四、触发器逻辑功能 触发器是构成时序电路的基本单元电路。按照触发器 逻辑功能的不同,触发器又可分为S功能触发器、JK 功能触发器,D功能触发器、功能触发器等 1、RS触发器 特征方程、状态图如下。 S=1R=0 S=0 S=x Qn+i =S+RO R=x R=0 R3=0 S=0R=1 2、K触发器(见下页)

四、触发器逻辑功能 触发器是构成时序电路的基本单元电路。按照触发器 逻辑功能的不同,触发器又可分为RS功能触发器、JK 功能触发器,D功能触发器、T功能触发器等 1、RS触发器 特征方程、状态图如下。 2、JK触发器(见下页)

JK触发器 凡在时钟信号作用下逻辑功能符合表13.1.4所规 定的逻辑功能者,叫做JK触发器 特征方程、状态图;真值表、激励表。 on K On+1 0 0 0 Qn+i=70m+on 0 0 1 0 0 1 0 1 0 1 1 1 1 0 0 1 1 0 0 J=1K=× 1 1 0 1 1 1 1 0 J=0 K=0 Q On+1 K K=X 】=X 0 0 0 0 1 1 J=×K=1 1 0 1 1 1 X 0

JK触发器 • 凡在时钟信号作用下逻辑功能符合表13.1.4所规 定的逻辑功能者,叫做JK触发器 • 特征方程、状态图;真值表、激励表

3、D触发器 凡在时钟信号作用下逻辑功能符合表13.1.3(下表)所规定的 逻辑功能者,叫做D触发器。 On+1 0 0 0 0 1 1 D=1 1 0 0 1 1 1 D=0 D=1 特征方程: D=0 Qn+1=D状态图如右 可知,当输入信号D=1时,Qn+1=1;当输入信号D=0, Qn+1=0;因此,D触发器具有置0、置1两种功能;保持功能 则是通过控制状态转移的控制信号是否有效来实现。 D触发器功能简单,应用时无输入约束,因此,应用土分广泛

3、D触发器 凡在时钟信号作用下逻辑功能符合表13.1.3(下表)所规定的 逻辑功能者,叫做D触发器。 特征方程: Qn+1=D 状态图如右 可知,当输入信号D=1时,Qn+1=1;当输入信号D=0, Qn+1=0;因此,D触发器具有置0、置1两种功能;保持功能 则是通过控制状态转移的控制信号是否有效来实现。 D触发器功能简单,应用时无输入约束,因此,应用十分广泛

三、边沿触发器 Name: 25.0ms 50.0ms 的一次变 CP 化问 w-S 便出现了 边沿 R 边 Q 边沿触发 控制 如上图所示为上升沿触发的RS触发器。由 于触发器只在CP信号上升沿到来时接收输入 信号,因此,触发器状态为1

为了克服主从JK触发器主触发器的一次变 化问题,增强电路工作的可靠性,便出现了 边沿触发器。 边沿触发器的电路形式较多,但边沿触发 控制的特点却是相同的。 如上图所示为上升沿触发的RS触发器。由 于触发器只在CP信号上升沿到来时接收输入 信号,因此,触发器状态为1。 三、边沿触发器

2、时序电路 电路在任一时刻输出的逻辑值不仅取决于该时刻电 路输入的逻辑值,而且还取决于电路的原来状态, 这种电路称为时序逻辑电路。简称时序电路。 可通过下图理解 时序电路通常包含组合 电路和存储电路两个组 组合电路 出 成部分 存储电路的输出状态必 W 须反馈到组合电路的输 入端,与输入信号一起, 存储单元 共同决定组合逻辑电路 的输出

2、时序电路 电路在任一时刻输出的逻辑值不仅取决于该时刻电 路输入的逻辑值,而且还取决于电路的原来状态, 这种电路称为时序逻辑电路。简称时序电路。 可通过下图理解 时序电路通常包含组合 电路和存储电路两个组 成部分 存储电路的输出状态必 须反馈到组合电路的输 入端,与输入信号一起, 共同决定组合逻辑电路 的输出