第二节AD转换器 主要要求 理解AVD转换的原理与过程 了解AD的基本参数及应用 退出

退出 第二节 A/D 转换器 主要要求: 理解 A/D 转换的原理与过程 了解 A/D 的基本参数及应用

A/D转换的基本原理 A/D转换器(ADC)是将输入模拟信号转换成数字信号的装 置。模拟信号特点是时间和幅值都连续,数字信号的特点时 间城和幅值城都离散。时间离散化须经过采样、保持两步骤 ;幅值离散化须经过量化、编码两步骤。 输入模拟,量 nn 输出数字量 (0。 量化编 '() 码 D Do 采样保持电路 退出

退出 A/D 转换器 (ADC) 是将输入模拟信号转换成数字信号的装 置。模拟信号特点是时间和幅值都连续,数字信号的特点时 间域和幅值域都离散。时间离散化须经过采样、保持两步骤 ;幅值离散化须经过量化、编码两步骤。 一、 A/D 转换的基本原理

1.采样和保持 由于输入信号是连续变化的,而转换需要一定时间, 为使转换正常进行,每进行一次转换,需要对输入信 号进行一次采样,以获得确定输入,并将这个输入保 持到转换结束,这个过程称为采样和保持。 脉冲控制开关 CPs 采样频率越高,信号 u()与u就越接近 4) () ADC的数字 数字量输出 转换误差越小,采样 化编码电路 X (n位) 频率f必须满足 f。≥2fmax max (采样定 ADC 输入模拟电压 采样一保持电路采样展宽信号 理) [max是u,频谱的最高 电容保持 频率分量。 退出

退出 1. 采样和保持 由于输入信号是连续变化的,而转换需要一定时间, 为使转换正常进行,每进行一次转换,需要对输入信 号进行一次采样,以获得确定输入,并将这个输入保 持到转换结束,这个过程称为采样和保持。 脉冲控制开关 电容保持 采样频率越高,信号 u`I (t) 与 uI 就越接近, 转换误差越小,采样 频率 f s 必须满足 f s≥2fmax (采样定 理) fmax 是 uI 频谱的最高 频率分量

2.量化和编码 将采样一保持后的电压化为某个规定的最小单位电压 整数倍的过程称为量化。把量化的数值用二进制代码 表示,称为编码。 量化所规定的最小单位电压称为量化单位,用△表示。由于输 入模拟电压幅值连续,不一定能被△整除,因而量化过程中不 可避免会引入误差,称此误差为量化误差,最大可达△。一般 有只舍不入法和有舍有入法两种 退出

退出 2. 量化和编码 将采样-保持后的电压化为某个规定的最小单位电压 整数倍的过程称为量化。把量化的数值用二进制代码 表示,称为编码。 量化所规定的最小单位电压称为量化单位,用 Δ 表示。由于输 入模拟电压幅值连续,不一定能被 Δ 整除,因而量化过程中不 可避免会引入误差,称此误差为量化误差,最大可达 Δ 。一般 有只舍不入法和有舍有入法两种

2.量化和编码 量化 编码 量化 输码 IV IV 111 }111 7/8V 13/15V 110 110 68V 11/15VM 101 5/8V 915V 100 100 4/SV 7/15V 011 011 38V 5/15V 010 010 28V 3/15V 001 001 1/8V 1/15V 000 000 W W (a) (b) 图12-9 两种量化编码 (a)只舍不入法(b)有舍有入法 退出

退出 2. 量化和编码 图 12-9 两种量化编码 ( a )只舍不入法 ( b )有舍有入法

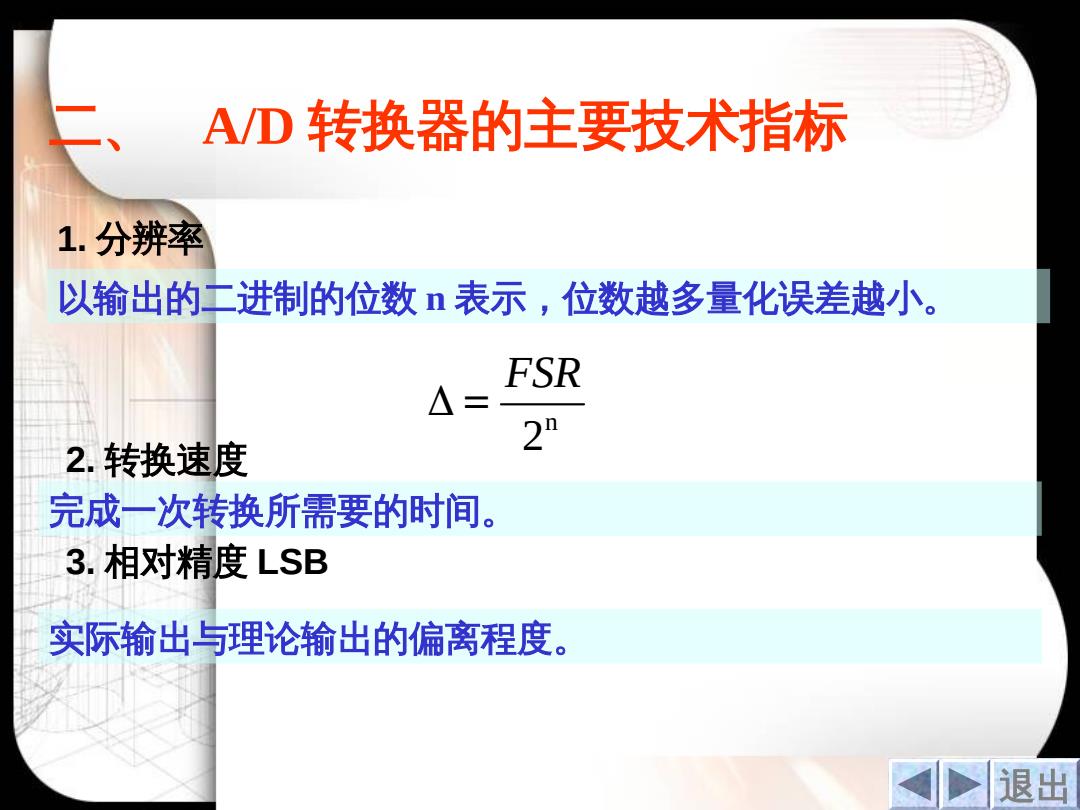

AD转换器的主要技术指标 1.分辨率 以输出的工进制的位数表示,位数越多量化误差越小。 FSR △= 2.转换速度 20 完成一次转换所需要的时间。 3.相对精度LSB 实际输出与理论输出的偏离程度。 退出

退出 二、 A/D 转换器的主要技术指标 1. 分辨率 以输出的二进制的位数 n 表示,位数越多量化误差越小。 n 2 FSR = 2. 转换速度 完成一次转换所需要的时间。 3. 相对精度 LSB 实际输出与理论输出的偏离程度

三、 逐次逼近型ADC 1.电路组成 DAC 00 D…D 数字量输出 逐次逼近 ST 制 时钟信号源 菁存器 @DA转换器,将数据寄存器中数字量转换成相应的模拟电压去与被测电压 比较。 ②数据寄存器,根据比较器中与输入量的比较结果决定最高位留下还是清除 ,逐位进行,所有位比较完毕后统一输出。 ③电压比较器A,比较数据寄存器中数据对应电压与输入电压; ④时钟,用于实现整机的逻辑控制。 退出

退出 三、 逐次逼近型 ADC 1. 电路组成 ①D/A 转换器,将数据寄存器中数字量转换成相应的模拟电压去与被测电压 比较。 ②数据寄存器,根据比较器中与输入量的比较结果决定最高位留下还是清除 ,逐位进行,所有位比较完毕后统一输出。 ③电压比较器 A ,比较数据寄存器中数据对应电压与输入电压; ④时钟,用于实现整机的逻辑控制

三、 逐次逼近型ADC 2.工作原理 它由电压比较器A、DAC、逐次逼近寄存器、时钟 信号源和控制逻辑组成,能将转换的模拟电压与一系列 的基准电压比较。比较是从高位到低位逐位进行的,并依次 确定各位数码是1还是0。转换开始前,先将控制逻辑输入 ST=0,使逐次逼近寄存器(SAR)清0,开始转换后,控 制逻辑输入ST=1,将逐次逼近寄存器(SAR)的最高位 (MSB)置1,使其输出为100..000,这个数码被D/A 转换器转换成相应的模拟电压 ,送至比较器与输入 比较。 退出

退出 三、 逐次逼近型 ADC 2. 工作原理 它由电压比较器 A 、 DAC 、逐次逼近寄存器、时钟 信号源和控制逻辑组成,能将转换的模拟电压 与一系列 的基准电压比较。比较是从高位到低位逐位进行的,并依次 确定各位数码是 1 还是 0 。转换开始前,先将控制逻辑输入 ST=0 ,使逐次逼近寄存器( SAR )清 0 ,开始转换后,控 制逻辑输入 ST=1 ,将逐次逼近寄存器( SAR )的最高位 ( MSB )置 1 ,使其输出为 100…000 ,这个数码被 D/A 转换器转换成相应的模拟电压 ,送至比较器与输入 比较。 I u I u I u uO

四、集成ADC0809简介 1.ADC0809的结构 由8位AD转换电路、8路模拟开关、地址锁存与译码电路、 以及三态输出锁存器组成。 DAC0809 引图 DAC0832内部结构 I N 12827255 恐 8路模拟似输入 START CLK 234 IN EOC 八路 START▣ 56 ADC 2④ 模拟量 0808 ▣ADDC 开关 三态 上D(2-8) EOC口 7 0809 ▣ALE IN 输出 2-5日 8 2 2-(MSB) 锁存器 0p2-2 3 电路 8 CLK 10 19 2-3 A 地址 Ucc 11 18p24 锁存」 十D(2 UR趣RH12 17p2-8(LSB) ALE 与译码 Ucc GND日13 16中URr( GND 2-7日 14 15p26 UREF(+)UREF(-) OE (a) 模拟输入的通道选 (b 通由地址ABC控 退出

退出 1.ADC0809 的结构 由 8 位 A/D 转换电路、 8 路模拟开关、地址锁存与译码电路、 以及三态输出锁存器组成。 DAC0809 引脚图 DAC0832 内部结构 8 路模拟输入 模拟输入的通道选 通由地址 ABC 控 制 四、集成 ADC0809 简介

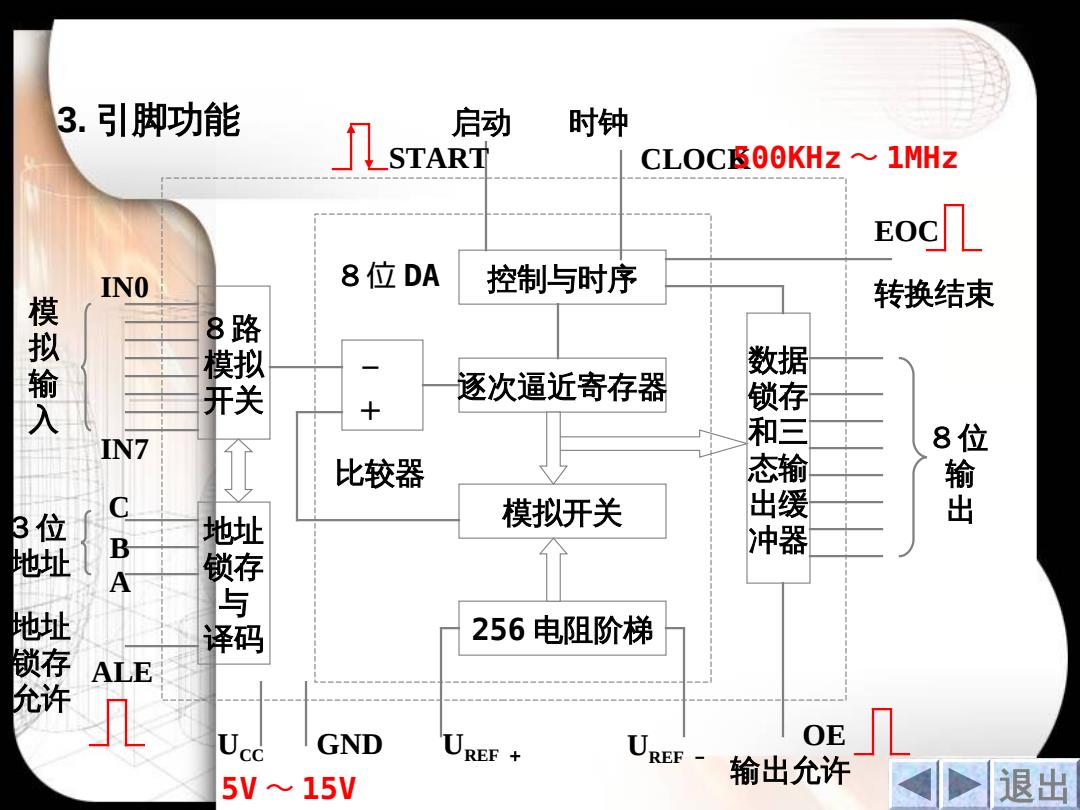

3.引脚功能 启动 时钟 START CLOC00KHz≈1MHz EOC INO 8位DA 控制与时序 转换结束 模拟输 8 拟 开 逐次逼近寄存器 授 IN7 和三 8位 比较器 位 C 模拟开关 恤 B 地址 A 麟 256电阻阶梯 ALE Ucc GND U OE REF REF一 输出允许 5V~15V 退出

退出 3. 引脚功能 控制与时序 逐次逼近寄存器 模拟开关 256 电阻阶梯 数据 锁存 和三 态输 出缓 冲器 8 路 模拟 开关 地址 锁存 与 译码 - + 比较器 8 位 DA 模 拟 输 入 IN0 IN7 3 位 地址 C B A 地址 锁存 允许 ALE UCC GND UREF + UREF - OE 输出允许 8 位 输 出 EOC 启动 START 时钟 CLOCK 5V ~ 15V 500KHz ~ 1MHz 转换结束