正在加载图片...

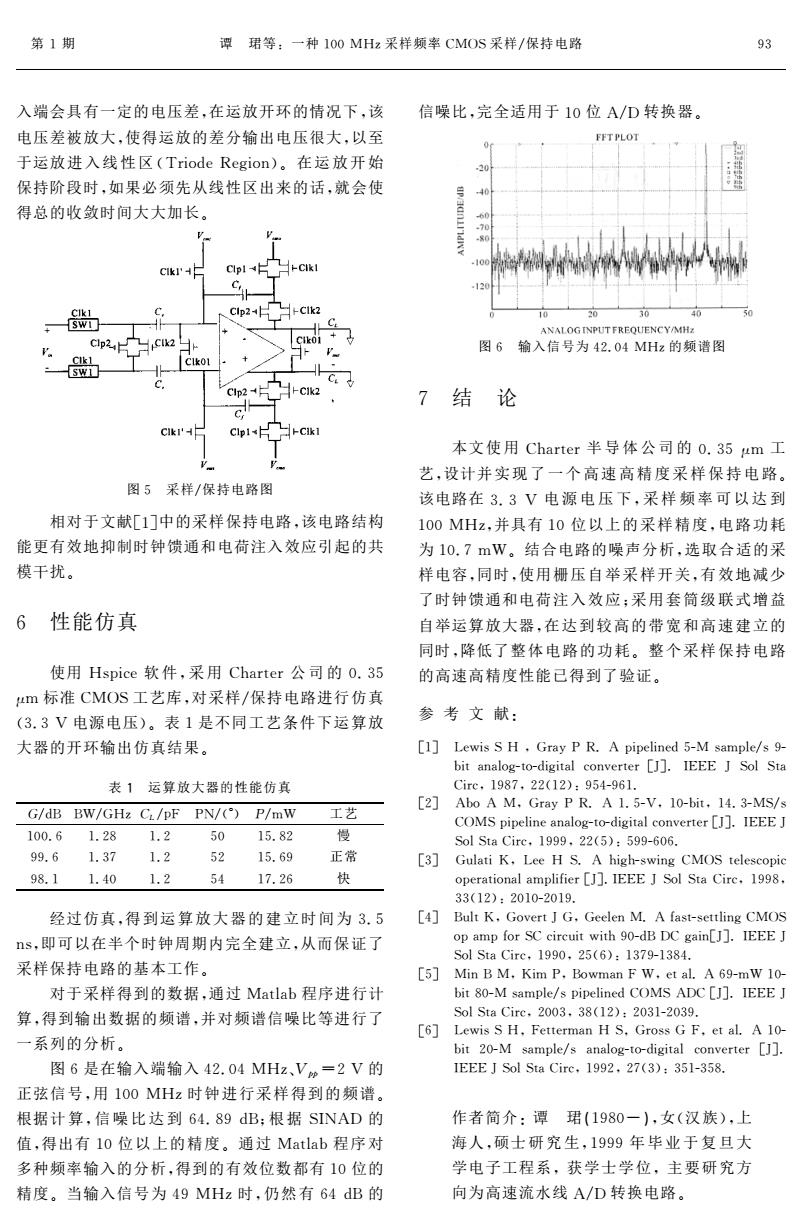

第1期 谭裙等:一种100MHz采样频率CMOS采样/保持电路 93 入端会具有一定的电压差,在运放开环的情况下,该 信噪比,完全适用于10位A/D转换器。 电压差被放大,使得运放的差分输出电压很大,以至 FFTPLOT 0 于运放进入线性区(Triode Region)。在运放开始 保持阶段时,如果必须先从线性区出来的话,就会使 % 得总的收敛时间大大加长。 V Clkl'- 12 Clp2 +C1k2 30 30 SWI ANALOGINPUT FREQUENCY/MHz Clp2 图6输入信号为42.04MHz的频谱图 C1k01 7 结论 Clp1 本文使用Charter半导体公司的0.35um工 艺,设计并实现了一个高速高精度采样保持电路。 图5采样/保持电路图 该电路在3.3V电源电压下,采样频率可以达到 相对于文献[1]中的采样保持电路,该电路结构 100MHz,并具有10位以上的采样精度,电路功耗 能更有效地抑制时钟馈通和电荷注入效应引起的共 为10.7mW。结合电路的噪声分析,选取合适的采 模干扰。 样电容,同时,使用栅压自举采样开关,有效地减少 了时钟馈通和电荷注入效应;采用套筒级联式增益 6 性能仿真 自举运算放大器,在达到较高的带宽和高速建立的 同时,降低了整体电路的功耗。整个采样保持电路 使用Hspice软件,采用Charter公司的0.35 的高速高精度性能已得到了验证。 am标准CMOS工艺库,对采样/保持电路进行仿真 (3.3V电源电压)。表1是不同工艺条件下运算放 参考文献: 大器的开环输出仿真结果。 [1]Lewis S H.Gray P R.A pipelined 5-M sample/s 9- bit analog-to-digital converter [J].IEEE J Sol Sta 表1运算放大器的性能仿真 Circ,1987,22(12):954-961. [2]Abo A M.Gray P R.A 1.5-V.10-bit,14.3-MS/s G/dB BW/GHz CL/pF PN/()P/mW 工艺 COMS pipeline analog-to-digital converter [J].IEEE J 100.6 1.28 1.2 50 15.82 慢 Sol Sta Cire,.1999,22(5):599-606. 99.6 1.371.2 52 15.69 正常 [3] Gulati K,Lee H S.A high-swing CMOS telescopic 98.11.401.25417.26 快 operational amplifier [J].IEEE J Sol Sta Circ.1998. 33(12):2010-2019. 经过仿真,得到运算放大器的建立时间为3.5 [4] Bult K.Govert J G.Geelen M.A fast-settling CMOS ns,即可以在半个时钟周期内完全建立,从而保证了 op amp for SC circuit with 90-dB DC gain[J].IEEE J Sol Sta Cire,1990,25(6):1379-1384. 采样保持电路的基本工作。 [5] Min B M.Kim P.Bowman F W,et al.A 69-mW 10- 对于采样得到的数据,通过Matlab程序进行计 bit 80-M sample/s pipelined COMS ADC [J].IEEE J 算,得到输出数据的频谱,并对频谱信噪比等进行了 Sol Sta Cire,2003,38(12):2031-2039. [6]Lewis S H,Fetterman H S.Gross G F,et al.A 10- 一系列的分析。 bit 20-M sample/s analog-to-digital converter [J]. 图6是在输入端输入42.04MHz、Vp=2V的 IEEE J Sol Sta Circ.1992.27(3):351-358. 正弦信号,用100MHz时钟进行采样得到的频谱。 根据计算,信噪比达到64.89dB;根据SINAD的 作者简介:谭珺(1980一),女(汉族),上 值,得出有10位以上的精度。通过Matlab程序对 海人,硕士研究生,1999年毕业于复旦大 多种频率输入的分析,得到的有效位数都有10位的 学电子工程系,获学士学位,主要研究方 精度。当输入信号为49MHz时,仍然有64dB的 向为高速流水线A/D转换电路。入端会具有一定的电压差,在运放开环的情况下,该 电压差被放大,使得运放的差分输出电压很大,以至 于运放进入线性区(TriodeRegion)。在运放开始 保持阶段时,如果必须先从线性区出来的话,就会使 得总的收敛时间大大加长。 图5 采样/保持电路图 相对于文献[1]中的采样保持电路,该电路结构 能更有效地抑制时钟馈通和电荷注入效应引起的共 模干扰。 6 性能仿真 使用 Hspice软 件,采 用 Charter公 司 的 0.35 µm 标准 CMOS工艺库,对采样/保持电路进行仿真 (3.3V 电源电压)。表1是不同工艺条件下运算放 大器的开环输出仿真结果。 表1 运算放大器的性能仿真 G/dB BW/GHz CL/pF PN/(º) P/mW 工艺 100.6 1.28 1.2 50 15.82 慢 99.6 1.37 1.2 52 15.69 正常 98.1 1.40 1.2 54 17.26 快 经过仿真,得到运算放大器的建立时间为3.5 ns,即可以在半个时钟周期内完全建立,从而保证了 采样保持电路的基本工作。 对于采样得到的数据,通过 Matlab程序进行计 算,得到输出数据的频谱,并对频谱信噪比等进行了 一系列的分析。 图6是在输入端输入42.04MHz、Vpp =2V 的 正弦信号,用100 MHz时钟进行采样得到的频谱。 根据计算,信噪比达到 64.89dB;根据 SINAD 的 值,得出有10位以上的精度。通过 Matlab程序对 多种频率输入的分析,得到的有效位数都有10位的 精度。当输入信号为49 MHz时,仍然有64dB 的 信噪比,完全适用于10位 A/D转换器。 图6 输入信号为42.04MHz的频谱图 7 结 论 本文使用 Charter半导体公司的 0.35µm 工 艺,设计并实现了一个高速高精度采样保持电路。 该电路在3.3 V 电 源 电 压 下,采 样 频 率 可 以 达 到 100MHz,并具有10 位以上的采样精度,电路功耗 为10.7mW。结合电路的噪声分析,选取合适的采 样电容,同时,使用栅压自举采样开关,有效地减少 了时钟馈通和电荷注入效应;采用套筒级联式增益 自举运算放大器,在达到较高的带宽和高速建立的 同时,降低了整体电路的功耗。整个采样保持电路 的高速高精度性能已得到了验证。 参 考 文 献: [1] LewisSH ,GrayPR.Apipelined5-Msample/s9- bitanalog-to-digitalconverter [J].IEEE J SolSta Circ,1987,22(12):954-961. [2] AboA M,GrayPR.A1.5-V,10-bit,14.3-MS/s COMSpipelineanalog-to-digitalconverter[J].IEEEJ SolStaCirc,1999,22(5):599-606. [3] GulatiK,Lee H S.A high-swingCMOStelescopic operationalamplifier[J].IEEEJSolStaCirc,1998, 33(12):2010-2019. [4] BultK,GovertJG,GeelenM.Afast-settlingCMOS opampforSCcircuitwith90-dBDCgain[J].IEEEJ SolStaCirc,1990,25(6):1379-1384. [5] MinB M,KimP,BowmanF W,etal.A69-mW10- bit80-Msample/spipelinedCOMSADC[J].IEEEJ SolStaCirc,2003,38(12):2031-2039. [6] LewisSH,FettermanHS,GrossGF,etal.A10- bit20-M sample/s analog-to-digitalconverter [J]. IEEEJSolStaCirc,1992,27(3):351-358. 作者简介:谭 珺(1980-),女(汉族),上 海人,硕士研究生,1999 年毕业于复旦大 学电子工程系,获学士学位,主要研究方 向为高速流水线 A/D转换电路。 第 1 期 谭 珺等:一种100MHz采样频率 CMOS采样/保持电路 93