正在加载图片...

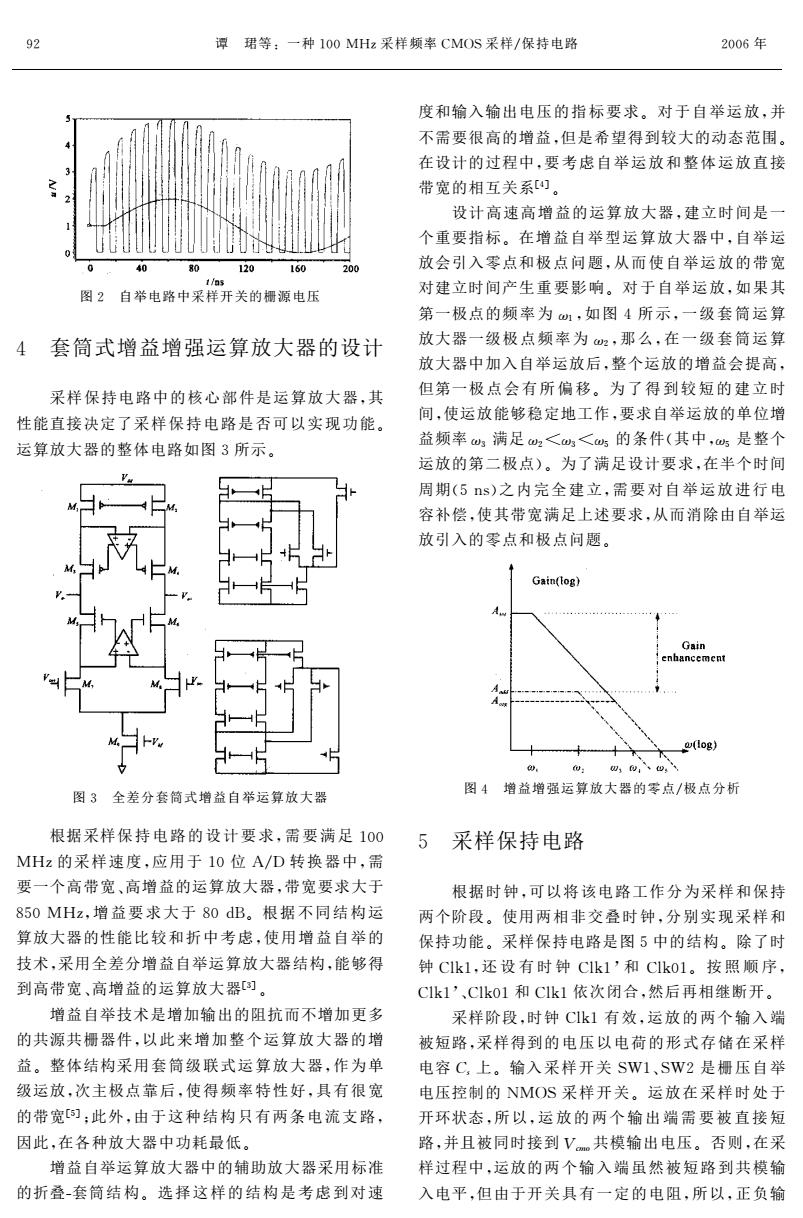

92 谭珺等:一种100MHz采样顿率CMOS采样/保持电路 2006年 度和输入输出电压的指标要求。对于自举运放,并 不需要很高的增益,但是希望得到较大的动态范围。 在设计的过程中,要考虑自举运放和整体运放直接 带宽的相互关系[)。 设计高速高增益的运算放大器,建立时间是一 个重要指标。在增益自举型运算放大器中,自举运 80 120 160 200 放会引入零点和极点问题,从而使自举运放的带宽 1/ns 图2自举电路中采样开关的栅源电压 对建立时间产生重要影响。对于自举运放,如果其 第一极点的频率为1,如图4所示,一级套筒运算 4套筒式增益增强运算放大器的设计 放大器一级极点频率为2,那么,在一级套筒运算 放大器中加入自举运放后,整个运放的增益会提高, 采样保持电路中的核心部件是运算放大器,其 但第一极点会有所偏移。为了得到较短的建立时 性能直接决定了采样保持电路是否可以实现功能。 间,使运放能够稳定地工作,要求自举运放的单位增 运算放大器的整体电路如图3所示。 益频率w满足2<w<a5的条件(其中,5是整个 运放的第二极点)。为了满足设计要求,在半个时间 周期(5ns)之内完全建立,需要对自举运放进行电 容补偿,使其带宽满足上述要求,从而消除由自举运 放引入的零点和极点问题。 Gain(tog) Gain o(log) 图3全差分套筒式增益自举运算放大器 图4增益增强运算放大器的零点/极点分析 根据采样保持电路的设计要求,需要满足100 5 采样保持电路 MHz的采样速度,应用于10位A/D转换器中,需 要一个高带宽、高增益的运算放大器,带宽要求大于 根据时钟,可以将该电路工作分为采样和保持 850MHz,增益要求大于80dB。根据不同结构运 两个阶段。使用两相非交叠时钟,分别实现采样和 算放大器的性能比较和折中考虑,使用增益自举的 保持功能。采样保持电路是图5中的结构。除了时 技术,采用全差分增益自举运算放大器结构,能够得 钟Ck1,还设有时钟CIk1’和CIk01。按照顺序, 到高带宽、高增益的运算放大器[)。 CIk1’、C1k01和C1k1依次闭合,然后再相继断开。 增益自举技术是增加输出的阻抗而不增加更多 采样阶段,时钟Ck1有效,运放的两个输入端 的共源共栅器件,以此来增加整个运算放大器的增 被短路,采样得到的电压以电荷的形式存储在采样 益。整体结构采用套筒级联式运算放大器,作为单 电容C,上。输入采样开关SW1、SW2是栅压自举 级运放,次主极点靠后,使得频率特性好,具有很宽 电压控制的NMOS采样开关。运放在采样时处于 的带宽[):此外,由于这种结构只有两条电流支路, 开环状态,所以,运放的两个输出端需要被直接短 因此,在各种放大器中功耗最低。 路,并且被同时接到V共模输出电压。否则,在采 增益自举运算放大器中的辅助放大器采用标准 样过程中,运放的两个输入端虽然被短路到共模输 的折叠-套筒结构。选择这样的结构是考虑到对速 入电平,但由于开关具有一定的电阻,所以,正负输图2 自举电路中采样开关的栅源电压 4 套筒式增益增强运算放大器的设计 采样保持电路中的核心部件是运算放大器,其 性能直接决定了采样保持电路是否可以实现功能。 运算放大器的整体电路如图3所示。 图3 全差分套筒式增益自举运算放大器 根据采样保持电路的设计要求,需要满足100 MHz的采样速度,应用于10位 A/D 转换器中,需 要一个高带宽、高增益的运算放大器,带宽要求大于 850MHz,增益要求大于80dB。根据不同结构运 算放大器的性能比较和折中考虑,使用增益自举的 技术,采用全差分增益自举运算放大器结构,能够得 到高带宽、高增益的运算放大器[3]。 增益自举技术是增加输出的阻抗而不增加更多 的共源共栅器件,以此来增加整个运算放大器的增 益。整体结构采用套筒级联式运算放大器,作为单 级运放,次主极点靠后,使得频率特性好,具有很宽 的带宽[5];此外,由于这种结构只有两条电流支路, 因此,在各种放大器中功耗最低。 增益自举运算放大器中的辅助放大器采用标准 的折叠-套筒结构。选择这样的结构是考虑到对速 度和输入输出电压的指标要求。对于自举运放,并 不需要很高的增益,但是希望得到较大的动态范围。 在设计的过程中,要考虑自举运放和整体运放直接 带宽的相互关系[4]。 设计高速高增益的运算放大器,建立时间是一 个重要指标。在增益自举型运算放大器中,自举运 放会引入零点和极点问题,从而使自举运放的带宽 对建立时间产生重要影响。对于自举运放,如果其 第一极点的频率为+1,如图4所示,一级套筒运算 放大器一级极点频率为+2,那么,在一级套筒运算 放大器中加入自举运放后,整个运放的增益会提高, 但第一极点会有所偏移。为了得到较短的建立时 间,使运放能够稳定地工作,要求自举运放的单位增 益频率+3 满足+2<+3<+5 的条件(其中,+5 是整个 运放的第二极点)。为了满足设计要求,在半个时间 周期(5ns)之内完全建立,需要对自举运放进行电 容补偿,使其带宽满足上述要求,从而消除由自举运 放引入的零点和极点问题。 图4 增益增强运算放大器的零点/极点分析 5 采样保持电路 根据时钟,可以将该电路工作分为采样和保持 两个阶段。使用两相非交叠时钟,分别实现采样和 保持功能。采样保持电路是图5中的结构。除了时 钟 Clk1,还 设 有 时 钟 Clk1’和 Clk01。按 照 顺 序, Clk1’、Clk01和 Clk1依次闭合,然后再相继断开。 采样阶段,时钟 Clk1有效,运放的两个输入端 被短路,采样得到的电压以电荷的形式存储在采样 电容Cs 上。输入采样开关 SW1、SW2是栅压自举 电压控制的 NMOS采样开关。运放在采样时处于 开环状态,所以,运放的两个输出端需要被直接短 路,并且被同时接到Vcmo共模输出电压。否则,在采 样过程中,运放的两个输入端虽然被短路到共模输 入电平,但由于开关具有一定的电阻,所以,正负输 92 谭 珺等:一种100MHz采样频率 CMOS采样/保持电路 2006年