正在加载图片...

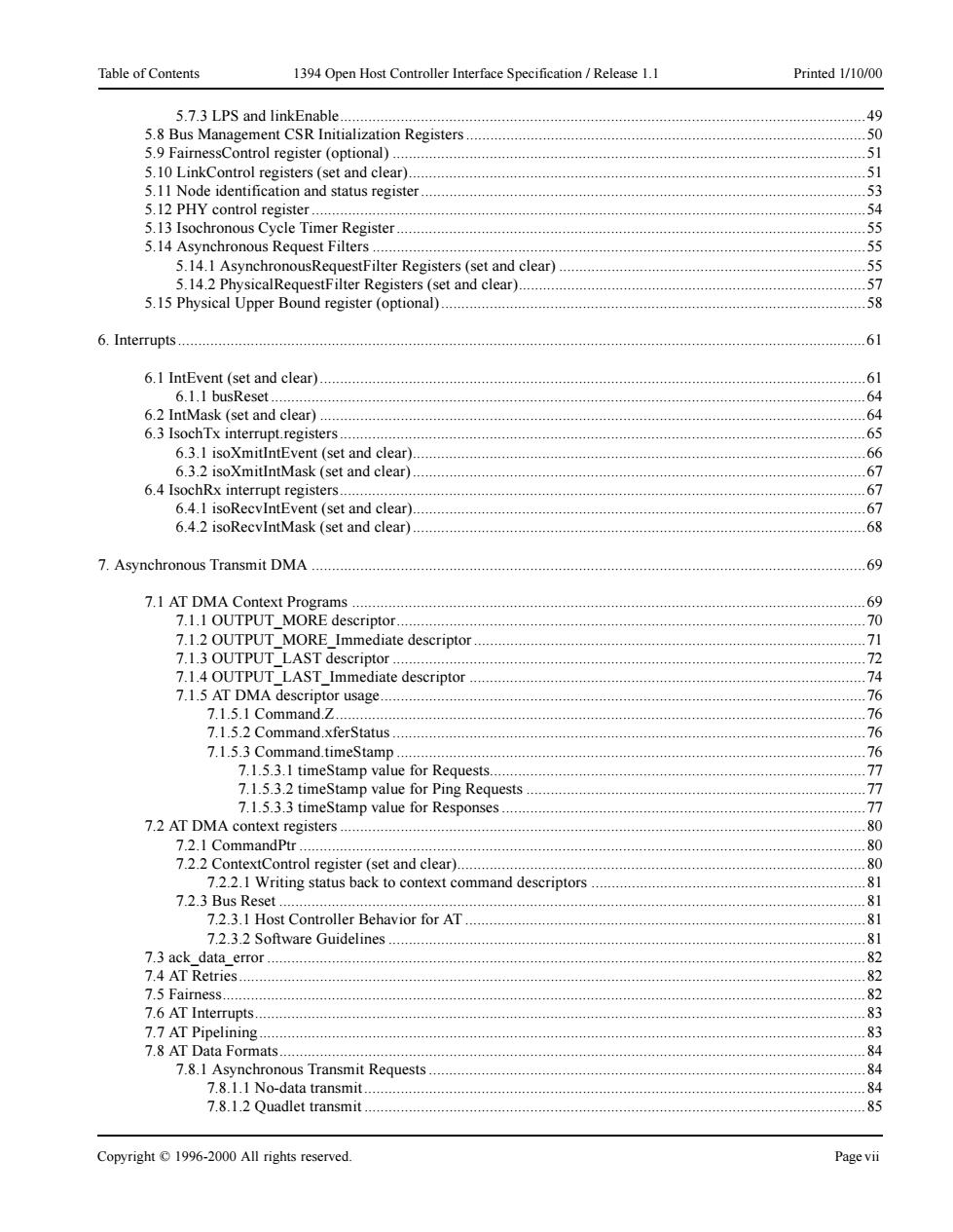

Table of Contents 1394 Open Host Controller Interface Specification /Release 1.1 Printed 1/10/00 5.7.3 LPS and linkEnable.......... 49 5.8 Bus Management CSR Initialization Registers. .50 5.9 FairnessControl register (optional)..... 51 5.10 LinkControl registers(set and clear)........ 51 5.11 Node identification and status register 53 5.12 PHY control register....... 54 5.13 Isochronous Cycle Timer Register.................... 55 5.14 Asynchronous Request Filters............ 55 5.14.1 AsynchronousRequestFilter Registers(set and clear) 55 5.14.2 PhysicalRequestFilter Registers (set and clear)....... 57 5.15 Physical Upper Bound register (optional)...... 58 6.Interrupts 61 6.1 IntEvent (set and clear)................ .61 6.1.I busReset.. 64 6.2 IntMask (set and clear)..... 64 6.3 IsochTx interrupt.registers.......... 65 6.3.1 isoXmitIntEvent (set and clear).. 66 6.3.2 isoXmitIntMask (set and clear) 67 6.4 IsochRx interrupt registers....... 67 6.4.1 isoRecvIntEvent(set and clear)... 67 6.4.2 isoRecvIntMask (set and clear).... 68 7.Asynchronous Transmit DMA...... .69 7.1 AT DMA Context Programs.......... 69 7.1.1 OUTPUT_MORE descriptor.... .70 7.1.2 OUTPUT MORE Immediate descriptor .71 7.1.3 OUTPUT_LAST descriptor... 72 7.1.4 OUTPUT LAST Immediate descriptor 74 7.1.5 AT DMA descriptor usage............ 76 7.1.5.1C0 nmand.Z… 76 7.1.5.2 Command.xferStatus.... 76 7.1.5.3 Command.timeStamp............ 76 7.1.5.3.I timeStamp value for Requests...... .77 7.1.5.3.2 timeStamp value for Ping Requests 77 7.1.5.3.3 timeStamp value for Responses 77 7.2 AT DMA context registers...... 80 7.2.1 CommandPtr........ 80 7.2.2 ContextControl register (set and clear)......... 80 7.2.2.1 Writing status back to context command descriptors. 81 7.2.3 Bus Reset.… 81 7.2.3.1 Host Controller Behavior for AT........ .81 7.2.3.2 Software Guidelines............... 81 7.3 ack data_error… 82 7.4 AT Retries.… 82 7.5 Fairness...... 82 7.6 AT Interrupts. 83 7.7AT Pipelining. 83 7.8 AT Data Formats..... 84 7.8.1 Asynchronous Transmit Requests 84 7.8.1.1 No-data transmit.... .84 7.8.1.2 Quadlet transmit..... 85 Copyright1996-2000 All rights reserved Page viiCopyright © 1996-2000 All rights reserved. Page vii Table of Contents 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00 5.7.3 LPS and linkEnable..................................................................................................................................49 5.8 Bus Management CSR Initialization Registers ...................................................................................................50 5.9 FairnessControl register (optional) .....................................................................................................................51 5.10 LinkControl registers (set and clear).................................................................................................................51 5.11 Node identification and status register ..............................................................................................................53 5.12 PHY control register .........................................................................................................................................54 5.13 Isochronous Cycle Timer Register ....................................................................................................................55 5.14 Asynchronous Request Filters ..........................................................................................................................55 5.14.1 AsynchronousRequestFilter Registers (set and clear) ............................................................................55 5.14.2 PhysicalRequestFilter Registers (set and clear)......................................................................................57 5.15 Physical Upper Bound register (optional) .........................................................................................................58 6. Interrupts ..........................................................................................................................................................................61 6.1 IntEvent (set and clear) .......................................................................................................................................61 6.1.1 busReset ...................................................................................................................................................64 6.2 IntMask (set and clear) .......................................................................................................................................64 6.3 IsochTx interrupt.registers ..................................................................................................................................65 6.3.1 isoXmitIntEvent (set and clear)................................................................................................................66 6.3.2 isoXmitIntMask (set and clear) ................................................................................................................67 6.4 IsochRx interrupt registers..................................................................................................................................67 6.4.1 isoRecvIntEvent (set and clear)................................................................................................................67 6.4.2 isoRecvIntMask (set and clear) ................................................................................................................68 7. Asynchronous Transmit DMA .........................................................................................................................................69 7.1 AT DMA Context Programs ...............................................................................................................................69 7.1.1 OUTPUT_MORE descriptor....................................................................................................................70 7.1.2 OUTPUT_MORE_Immediate descriptor .................................................................................................71 7.1.3 OUTPUT_LAST descriptor .....................................................................................................................72 7.1.4 OUTPUT_LAST_Immediate descriptor ..................................................................................................74 7.1.5 AT DMA descriptor usage........................................................................................................................76 7.1.5.1 Command.Z...................................................................................................................................76 7.1.5.2 Command.xferStatus .....................................................................................................................76 7.1.5.3 Command.timeStamp ....................................................................................................................76 7.1.5.3.1 timeStamp value for Requests.............................................................................................77 7.1.5.3.2 timeStamp value for Ping Requests ....................................................................................77 7.1.5.3.3 timeStamp value for Responses ..........................................................................................77 7.2 AT DMA context registers ..................................................................................................................................80 7.2.1 CommandPtr ............................................................................................................................................80 7.2.2 ContextControl register (set and clear).....................................................................................................80 7.2.2.1 Writing status back to context command descriptors ....................................................................81 7.2.3 Bus Reset .................................................................................................................................................81 7.2.3.1 Host Controller Behavior for AT ...................................................................................................81 7.2.3.2 Software Guidelines ......................................................................................................................81 7.3 ack_data_error ....................................................................................................................................................82 7.4 AT Retries...........................................................................................................................................................82 7.5 Fairness...............................................................................................................................................................82 7.6 AT Interrupts.......................................................................................................................................................83 7.7 AT Pipelining......................................................................................................................................................83 7.8 AT Data Formats.................................................................................................................................................84 7.8.1 Asynchronous Transmit Requests ............................................................................................................84 7.8.1.1 No-data transmit............................................................................................................................84 7.8.1.2 Quadlet transmit ............................................................................................................................85