正在加载图片...

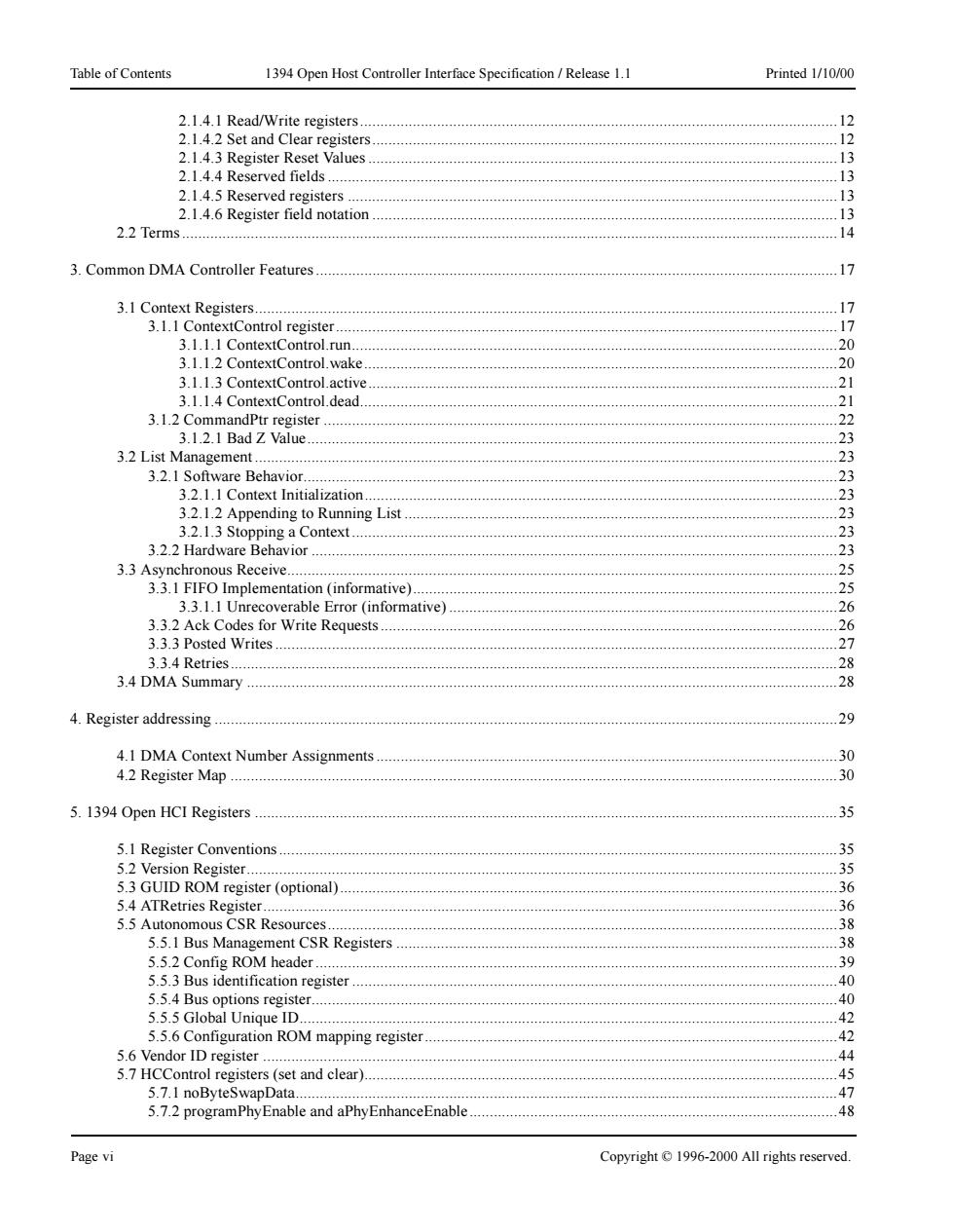

Table of Contents 1394 Open Host Controller Interface Specification Release 1.1 Printed 1/10/00 2.1.4.1 Read/Write registers.......... .12 2.1.4.2 Set and Clear registers.. 12 2.1.4.3 Register Reset Values....... ..13 2.1.4.4 Reserved fields .13 2.1.4.5 Reserved registers 2.1.4.6 Register field notation 13 .13 2.2 Terms 14 3.Common DMA Controller Features........ 17 3.I Context Registers.... 3.1.1 ContextControl register........... 17 .17 3.1.1.1 ContextControl.run.......... 20 3.1.1.2 ContextControl.wake.... .20 3.1.1.3 ContextControl.active............ 21 3.1.1.4 ContextControl.dead. 21 3.1.2 CommandPtr register........ .22 3.1.2.1 Bad Z Value............. 23 3.2 List Management. .23 3.2.1 Software Behavior.... 23 3.2.1.1 Context Initialization..... 23 3.2.1.2 Appending to Running List... .23 3.2.1.3 Stopping a Context.. 23 3.2.2 Hardware Behavior .23 3.3 Asynchronous Receive............. 3.3.1 FIFO Implementation (informative)........ .25 25 3.3.1.1 Unrecoverable Error (informative) .26 3.3.2 Ack Codes for Write Requests... .26 3.3.3 Posted Writes.... 27 3.3.4 Retries.… .28 3.4 DMA Summary........ 28 4.Register addressing...... .29 4.1 DMA Context Number Assignments .30 4.2 Register Map.… .30 5.1394 Open HCI Registers ,35 5.1 Register Conventions........... .35 5.2 Version Register....... .35 5.3 GUID ROM register(optional). .36 5.4 ATRetries Register.......... .36 5.5 Autonomous CSR Resources..... 38 5.5.1 Bus Management CSR Registers......... 38 5.5.2 Config ROM header.................. 39 5.5.3 Bus identification register............. 40 5.5.4 Bus options register..... .…40 5.5.5 Global Unique ID... 42 5.5.6 Configuration ROM mapping register...... .42 5.6 Vendor ID register......... 44 5.7 HCControl registers (set and clear)........... 45 5.7.1 noByteSwapData...... ..47 5.7.2 programPhy Enable and aPhyEnhanceEnable. 48 Page vi Copyright1996-2000 All rights reserved.Page vi Copyright © 1996-2000 All rights reserved. Table of Contents 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00 2.1.4.1 Read/Write registers ......................................................................................................................12 2.1.4.2 Set and Clear registers...................................................................................................................12 2.1.4.3 Register Reset Values ....................................................................................................................13 2.1.4.4 Reserved fields ..............................................................................................................................13 2.1.4.5 Reserved registers .........................................................................................................................13 2.1.4.6 Register field notation ...................................................................................................................13 2.2 Terms ..................................................................................................................................................................14 3. Common DMA Controller Features .................................................................................................................................17 3.1 Context Registers................................................................................................................................................17 3.1.1 ContextControl register............................................................................................................................17 3.1.1.1 ContextControl.run........................................................................................................................20 3.1.1.2 ContextControl.wake.....................................................................................................................20 3.1.1.3 ContextControl.active....................................................................................................................21 3.1.1.4 ContextControl.dead......................................................................................................................21 3.1.2 CommandPtr register ...............................................................................................................................22 3.1.2.1 Bad Z Value...................................................................................................................................23 3.2 List Management ................................................................................................................................................23 3.2.1 Software Behavior....................................................................................................................................23 3.2.1.1 Context Initialization.....................................................................................................................23 3.2.1.2 Appending to Running List ...........................................................................................................23 3.2.1.3 Stopping a Context ........................................................................................................................23 3.2.2 Hardware Behavior ..................................................................................................................................23 3.3 Asynchronous Receive........................................................................................................................................25 3.3.1 FIFO Implementation (informative).........................................................................................................25 3.3.1.1 Unrecoverable Error (informative) ................................................................................................26 3.3.2 Ack Codes for Write Requests .................................................................................................................26 3.3.3 Posted Writes ...........................................................................................................................................27 3.3.4 Retries......................................................................................................................................................28 3.4 DMA Summary ..................................................................................................................................................28 4. Register addressing ..........................................................................................................................................................29 4.1 DMA Context Number Assignments ..................................................................................................................30 4.2 Register Map ......................................................................................................................................................30 5. 1394 Open HCI Registers ................................................................................................................................................35 5.1 Register Conventions ..........................................................................................................................................35 5.2 Version Register..................................................................................................................................................35 5.3 GUID ROM register (optional) ...........................................................................................................................36 5.4 ATRetries Register..............................................................................................................................................36 5.5 Autonomous CSR Resources..............................................................................................................................38 5.5.1 Bus Management CSR Registers .............................................................................................................38 5.5.2 Config ROM header .................................................................................................................................39 5.5.3 Bus identification register ........................................................................................................................40 5.5.4 Bus options register..................................................................................................................................40 5.5.5 Global Unique ID.....................................................................................................................................42 5.5.6 Configuration ROM mapping register......................................................................................................42 5.6 Vendor ID register ..............................................................................................................................................44 5.7 HCControl registers (set and clear).....................................................................................................................45 5.7.1 noByteSwapData......................................................................................................................................47 5.7.2 programPhyEnable and aPhyEnhanceEnable...........................................................................................48