正在加载图片...

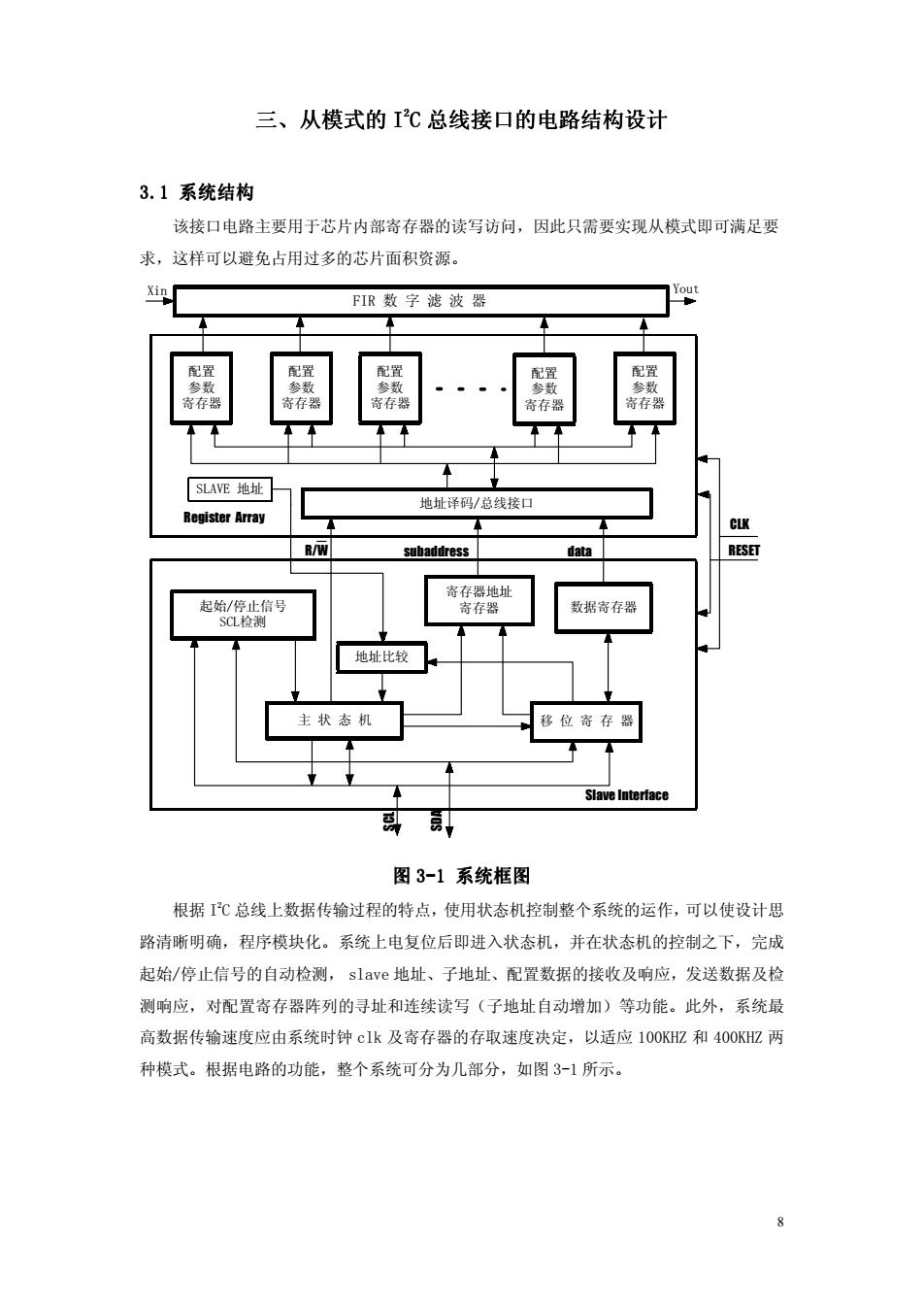

三、从模式的I℃总线接口的电路结构设计 3.1系统结构 该接口电路主要用于芯片内部寄存器的读写访问,因此只需要实现从模式即可满足要 求,这样可以避免占用过多的芯片面积资源。 Xin Yout FIR数字滤波器 配置 配置 配置 配置 配置 参数 参数 参数 参数 参数 寄存器 寄存器 寄存器 寄存器 寄存器 SLAVE地址 地址译码/总线接口 Register Array CLK /丽 subaddress data RESET 寄存器地址 起始/停止信号 寄存器 数据寄存器 SCL检测 地址比较 主状态机 移位寄存器 Slave Interface 图3-1系统框图 根据℃总线上数据传输过程的特点,使用状态机控制整个系统的运作,可以使设计思 路清晰明确,程序模块化。系统上电复位后即进入状态机,并在状态机的控制之下,完成 起始/停止信号的自动检测,slave地址、子地址、配置数据的接收及响应,发送数据及检 测响应,对配置寄存器阵列的寻址和连续读写(子地址自动增加)等功能。此外,系统最 高数据传输速度应由系统时钟c1k及寄存器的存取速度决定,以适应100KHZ和400KH忆两 种模式。根据电路的功能,整个系统可分为几部分,如图3-1所示。 8

": ;<=> U-Ð!"ÎäÏá

XYËÌÕ&N,- Y)ßà- 6 )5°±¸7S

!"»¼èé% SCL SDA R/W Slave Interface Register Array CLK subaddress data RESET

!" #$%& '( )*+ ,-./ " ;<? á«

I

«¬7

Úâ'uvwWX

st

aI)5' ãäåæC z%stI?YMuvwDFuvw

WX¥®Ù 7ý¡¢

ç y|z ·¨<y·¨<#$

«

x¸ãw

«ç ¸#$Ïá ÐÑ

§¨[£¶XY¼y·¨½¢ÑÒ%& st ÷

«¬øÒstB> èú Ïá

á/øÒ,5é gKKêdë [ nKKêdë %á«

ÑÒ

st)å9ìäåÚ~ ojg +P%������������