正在加载图片...

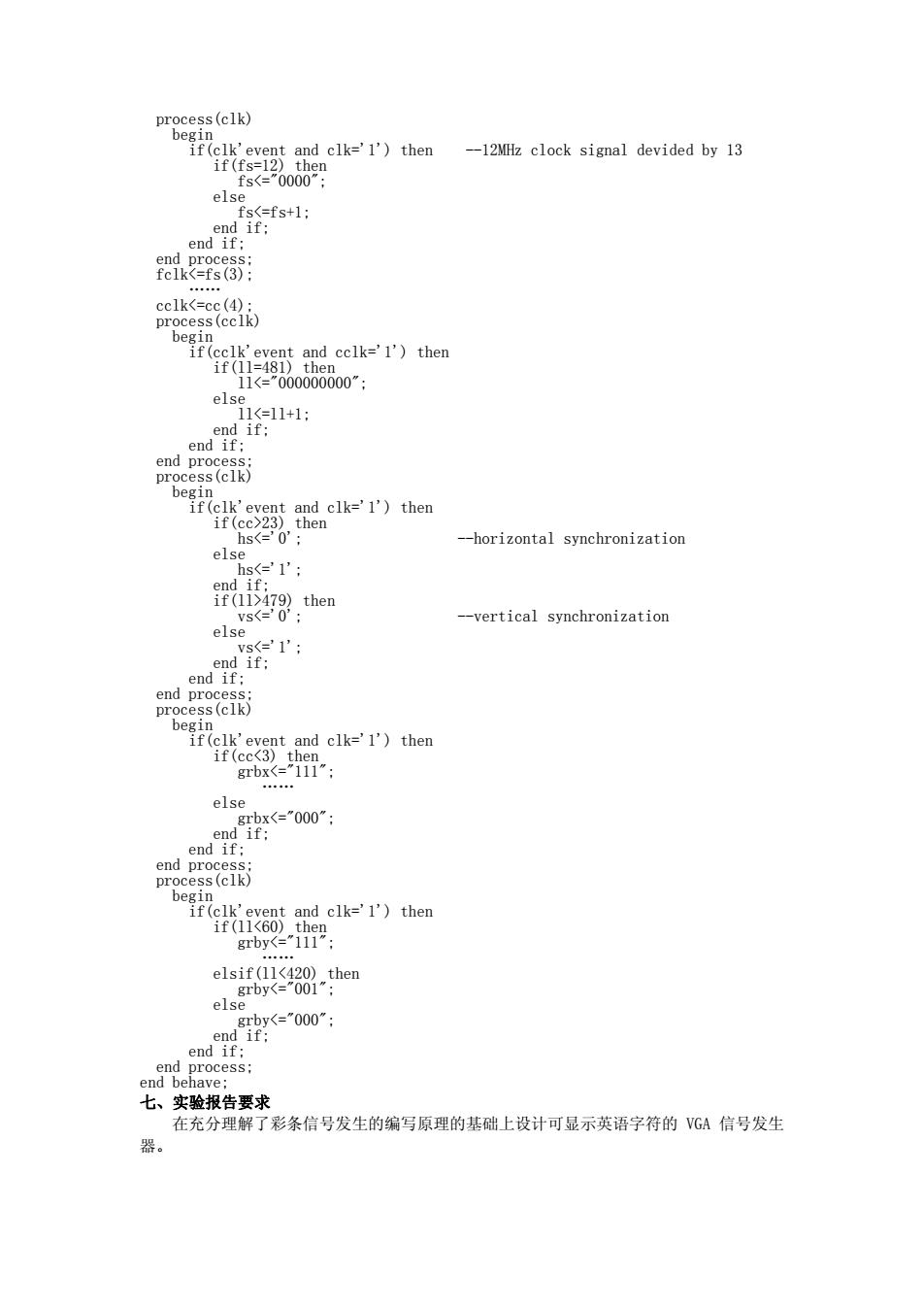

process(clk) begin if(clk'event and clk='1')then -12MHz clock signal devided by 13 if(fs=12)then fs<="0000"; else fs<=fs+l: end if; end if; end process: fclk<=fs(3); 中中年。年 cclk<=cc(4): process(cclk) begin if(cclk'event and cclk='1')then if(11=481)then 11<="000000000": else 11<=11+1: end if; end if: end process; process(clk) begin if(clk'event and clk='1')then if (cc>23)then hs<='0: --horizontal synchronization els hs<=1'; end if. if(11>479)then vs=0; --vertical synchronization else vs<e'1'; end if; end if; end process: process(clk) begin if(clk'event and clk='1')then if(cc<3)then grbx<="111”: ee中。 else grbx<="000”: end if; end if; end process: process(clk) begin if(clk'event and clk='1')then if(11<60)then grby<="111": elsif(11<420)then grby<="001"; els grby<="000": end if: end if; end process; end behave; 七、实验报告要求 在充分理解了彩条信号发生的编写原理的基础上设计可显示英语字符的VGA信号发生 器。process(clk) begin if(clk'event and clk='1') then --12MHz clock signal devided by 13 if(fs=12) then fs<="0000"; else fs<=fs+1; end if; end if; end process; fclk<=fs(3); …… cclk<=cc(4); process(cclk) begin if(cclk'event and cclk='1') then if(ll=481) then ll<="000000000"; else ll<=ll+1; end if; end if; end process; process(clk) begin if(clk'event and clk='1') then if(cc>23) then hs<='0'; --horizontal synchronization else hs<='1'; end if; if(ll>479) then vs<='0'; --vertical synchronization else vs<='1'; end if; end if; end process; process(clk) begin if(clk'event and clk='1') then if(cc<3) then grbx<="111"; …… else grbx<="000"; end if; end if; end process; process(clk) begin if(clk'event and clk='1') then if(ll<60) then grby<="111"; …… elsif(ll<420) then grby<="001"; else grby<="000"; end if; end if; end process; end behave; 七、实验报告要求 在充分理解了彩条信号发生的编写原理的基础上设计可显示英语字符的 VGA 信号发生 器