正在加载图片...

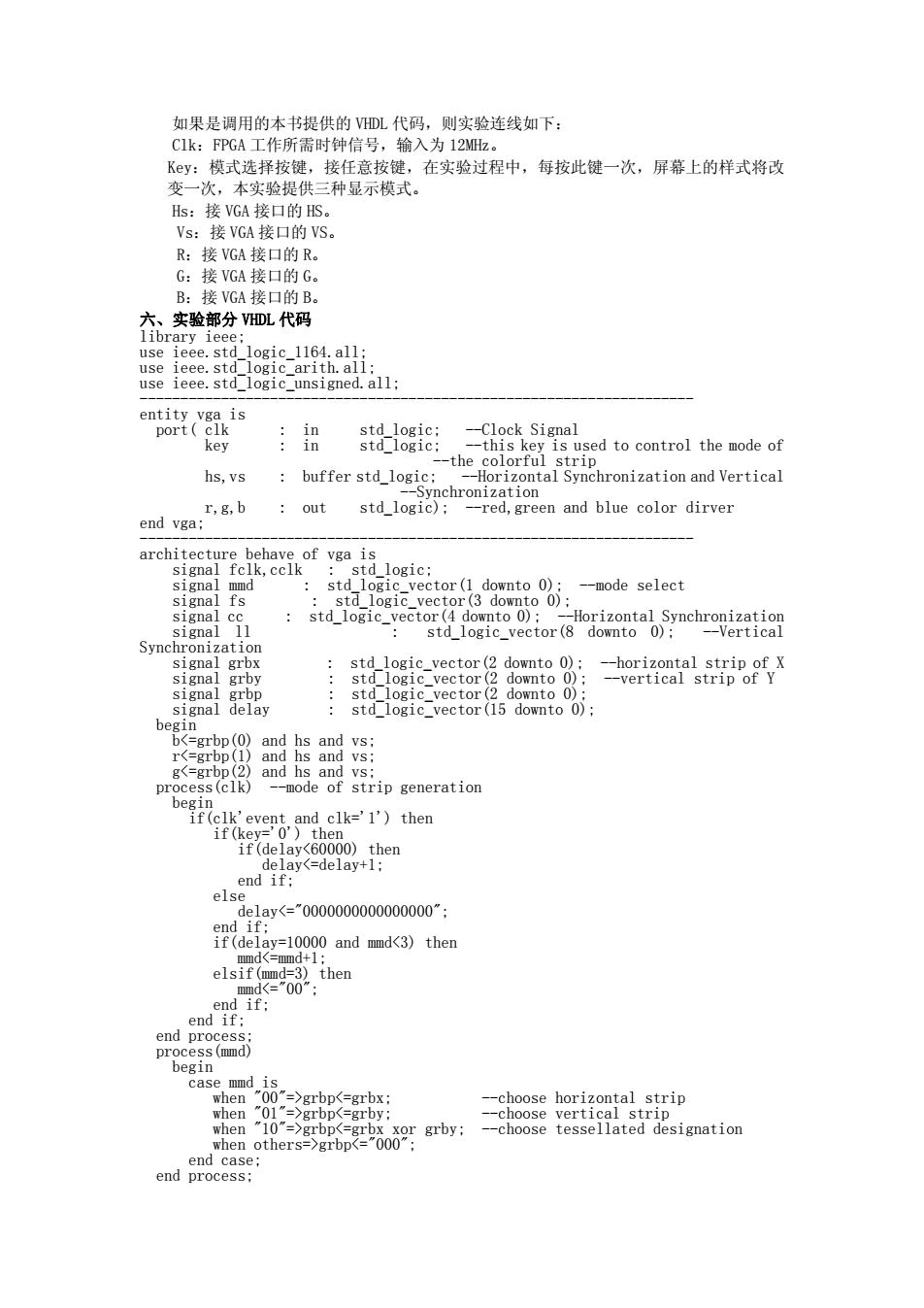

如果是调用的本书提供的VDL代码,则实验连线如下: C1k:FPGA工作所需时钟信号,输入为12Mz。 Ky:模式选择按键,接任意按键,在实验过程中,每按此键一次,屏幕上的样式将改 变一次,本实验提供三种显示模式。 Hs:接VGA接口的HS。 Vs:接VGA接▣的VS R:接VGA接口的R。 G:接VGA接口的G。 B:接VGA接口的B。 六、实验部分DL代码 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all: use ieee.std_logic_unsigned.all; entity vga is port(clk in std logic; -Clock Signal key in std logic; -this key is used to control the mode of --the colorful strip hs,vs buffer std_logic: --Horizontal Synchronization and Vertical --Synchronization r,g,b out std logic); -red,green and blue color dirver end vga: architecture behave of vga is signal fclk,cclk std logic; signal mmd std logic vector(1 downto 0); --mode select signal fs std logic vector(3 downto 0); signal cc std logic vector(4 downto 0); --Horizontal Synchronization signal ll 。 std logic vector(8 downto 0): --Vertical Synchronization signal grbx std logic vector(2 downto 0); --horizontal strip of X signal grby std logic_vector(2 downto 0); --vertical strip of Y signal grbp std logic vector(2 downto 0); signal delay std_logic_vector(15 downto 0); begin b<=grbp(0) and hs and vs; r<=grbp(1) and hs and vs: g<=grbp(2) and hs and vs; process(clk) --mode of strip generation begin if(clk'event and clk='1')then if (key='0)then if(delay<60000)then delay<=delay+1; end if; else de1ay<="0000000000000000": end if; if(delay=10000 and mmd<3)then mmd<=mmd+1; elsif(mmd=3)then mmdK="00”: end if; end if; end process; process (mmd) begin case mmd is when "00"=>grbp<=grbx: --choose horizontal strip when "01"=>grbp<-grby; --choose vertical strip when "10"=>grbp<=grbx xor grby: --choose tessellated designation when others=>grbp<="000": end case; end process;如果是调用的本书提供的 VHDL 代码,则实验连线如下: Clk:FPGA 工作所需时钟信号,输入为 12MHz。 Key:模式选择按键,接任意按键,在实验过程中,每按此键一次,屏幕上的样式将改 变一次,本实验提供三种显示模式。 Hs:接 VGA 接口的 HS。 Vs:接 VGA 接口的 VS。 R:接 VGA 接口的 R。 G:接 VGA 接口的 G。 B:接 VGA 接口的 B。 六、实验部分 VHDL 代码 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; -------------------------------------------------------------------- entity vga is port( clk : in std_logic; --Clock Signal key : in std_logic; --this key is used to control the mode of --the colorful strip hs,vs : buffer std_logic; --Horizontal Synchronization and Vertical --Synchronization r,g,b : out std_logic); --red,green and blue color dirver end vga; -------------------------------------------------------------------- architecture behave of vga is signal fclk,cclk : std_logic; signal mmd : std_logic_vector(1 downto 0); --mode select signal fs : std_logic_vector(3 downto 0); signal cc : std_logic_vector(4 downto 0); --Horizontal Synchronization signal ll : std_logic_vector(8 downto 0); --Vertical Synchronization signal grbx : std_logic_vector(2 downto 0); --horizontal strip of X signal grby : std_logic_vector(2 downto 0); --vertical strip of Y signal grbp : std_logic_vector(2 downto 0); signal delay : std_logic_vector(15 downto 0); begin b<=grbp(0) and hs and vs; r<=grbp(1) and hs and vs; g<=grbp(2) and hs and vs; process(clk) --mode of strip generation begin if(clk'event and clk='1') then if(key='0') then if(delay<60000) then delay<=delay+1; end if; else delay<="0000000000000000"; end if; if(delay=10000 and mmd<3) then mmd<=mmd+1; elsif(mmd=3) then mmd<="00"; end if; end if; end process; process(mmd) begin case mmd is when "00"=>grbp<=grbx; --choose horizontal strip when "01"=>grbp<=grby; --choose vertical strip when "10"=>grbp<=grbx xor grby; --choose tessellated designation when others=>grbp<="000"; end case; end process;