正在加载图片...

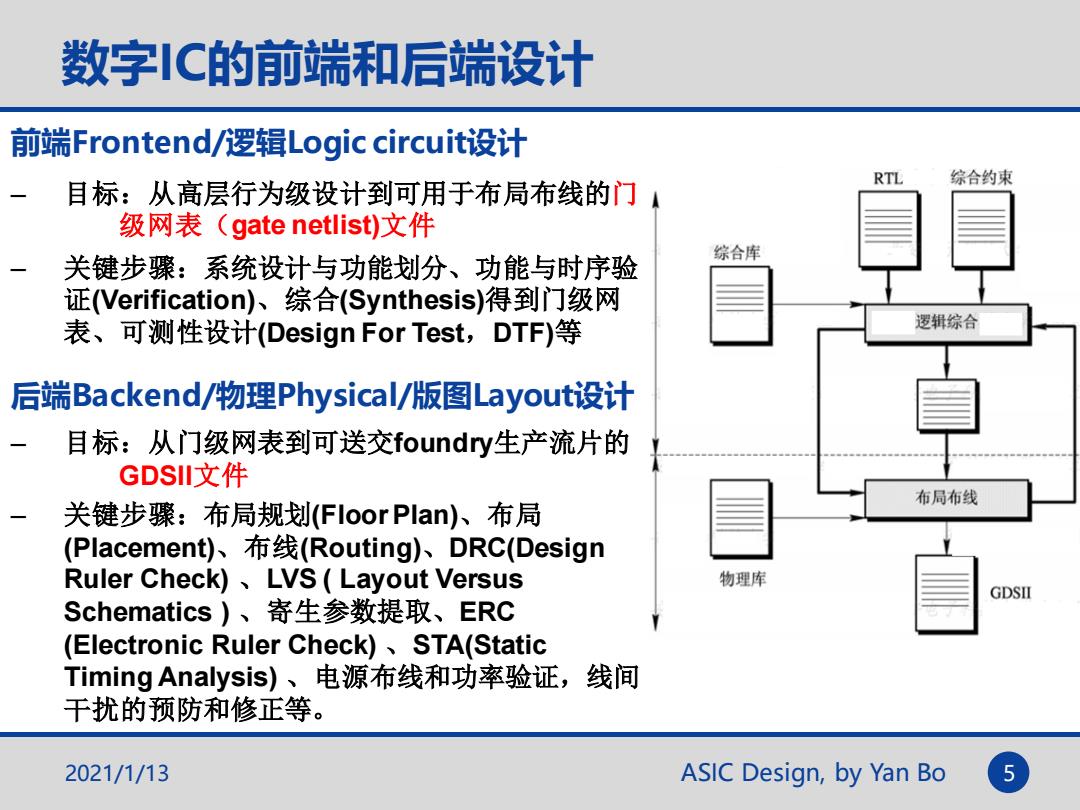

数字IC的前端和后端设计 前端Frontend/逻辑Logic circuit设计 RTL 综合约束 目标:从高层行为级设计到可用于布局布线的门 级网表(gate netlist)文件 综合库 关键步骤:系统设计与功能划分、功能与时序验 证(Verification)、综合(Synthesis)得到门级网 表、可测性设计(Design For Test,DTF)等 逻辑综合 后端Backend/物理Physical/版图Layout设计 目标:从门级网表到可送交foundry生产流片的 GDSl文件 布局布线 关键步骤:布局规划(Floor Plan)、布局 (Placement)、布线(Routing、DRC(Design Ruler Check)LVS(Layout Versus 物理库 GDSII Schematics)、寄生参数提取、ERC (Electronic Ruler Check)STA(Static Timing Analysis)、电源布线和功率验证,线间 干扰的预防和修正等。 2021/1/13 ASIC Design,by Yan Bo 5ASIC Design, by Yan Bo 数字IC的前端和后端设计 前端Frontend/逻辑Logic circuit设计 – 目标:从高层行为级设计到可用于布局布线的门 级网表(gate netlist)文件 – 关键步骤:系统设计与功能划分、功能与时序验 证(Verification)、综合(Synthesis)得到门级网 表、可测性设计(Design For Test,DTF)等 后端Backend/物理Physical/版图Layout设计 – 目标:从门级网表到可送交foundry生产流片的 GDSII文件 – 关键步骤:布局规划(Floor Plan)、布局 (Placement)、布线(Routing)、DRC(Design Ruler Check) 、LVS ( Layout Versus Schematics ) 、寄生参数提取、ERC (Electronic Ruler Check) 、STA(Static Timing Analysis) 、电源布线和功率验证,线间 干扰的预防和修正等。 2021/1/13 5