正在加载图片...

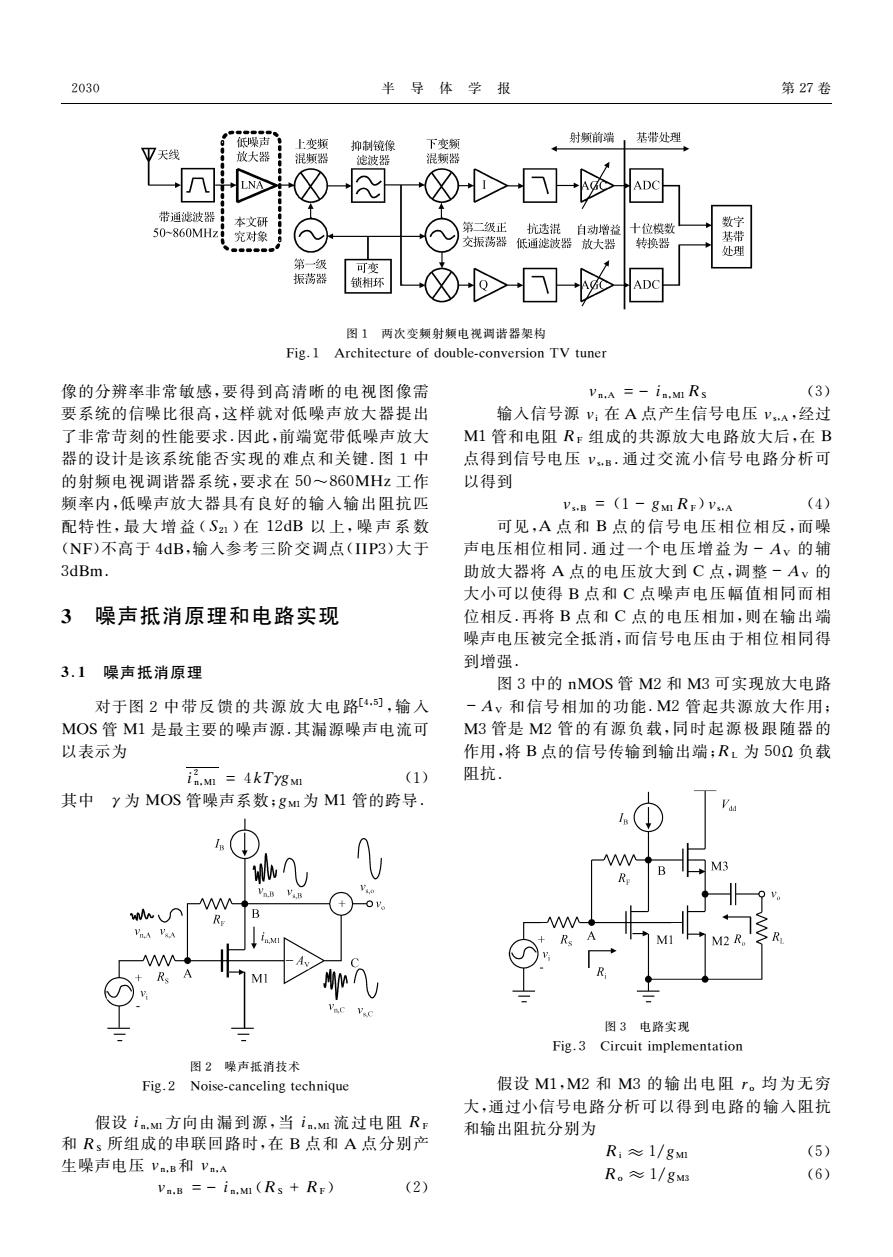

2030 半导体学报 第27卷 低噪声。 上变频 抑制镜像 下变频 射频前端, 基带处理 W天线 放大器 混频器 滤波器 混频器 NA 带通泷波器 本文研 50-860MHz 第二级正抗遗混自动增拉 十位棋数 究对象 交振荡器低通滤波器放大器 转换器 处理 第一级 可变 振荡器 锁相环 图1两次变频射频电视调谐器架构 Fig.I Architecture of double-conversion TV tuner 像的分辨率非常敏感,要得到高清晰的电视图像需 Vn.A =-in.MI Rs (3) 要系统的信噪比很高,这样就对低噪声放大器提出 输入信号源y:在A点产生信号电压VA,经过 了非常苛刻的性能要求.因此,前端宽带低噪声放大 M1管和电阻R:组成的共源放大电路放大后,在B 器的设计是该系统能否实现的难点和关键.图1中 点得到信号电压VB·通过交流小信号电路分析可 的射频电视调谐器系统,要求在50~860MHz工作 以得到 频率内,低噪声放大器具有良好的输入输出阻抗匹 Vs.B =(1-gM RF)V..A (4) 配特性,最大增益(S21)在12dB以上,噪声系数 可见,A点和B点的信号电压相位相反,而噪 (NF)不高于4dB,输入参考三阶交调点(IIP3)大于 声电压相位相同.通过一个电压增益为-Av的辅 3dBm. 助放大器将A点的电压放大到C点,调整-Av的 大小可以使得B点和C点噪声电压幅值相同而相 3噪声抵消原理和电路实现 位相反.再将B点和C点的电压相加,则在输出端 噪声电压被完全抵消,而信号电压由于相位相同得 3.1噪声抵消原理 到增强. 图3中的nMOS管M2和M3可实现放大电路 对于图2中带反馈的共源放大电路4可,输入 -Av和信号相加的功能.M2管起共源放大作用: MOS管M1是最主要的噪声源.其漏源噪声电流可 M3管是M2管的有源负载,同时起源极跟随器的 以表示为 作用,将B点的信号传输到输出端;RL为502负载 m=4kTY8如 (1) 阻抗. 其中y为MOS管噪声系数:g如为M1管的跨导. M2 图3电路实现 Fig.3 Circuit implementation 图2噪声抵消技术 Fig.2 Noise-canceling technique 假设M1,M2和M3的输出电阻r。均为无穷 大,通过小信号电路分析可以得到电路的输入阻抗 假设ia,M方向由漏到源,当in,M流过电阻R 和输出阻抗分别为 和Rs所组成的串联回路时,在B点和A点分别产 R:≈1/gm (5) 生噪声电压Vm,B和VA R。≈1/gMs (6) Va.B =-in.MI(Rs RF) (2)半 导 体 学 报 第27卷 图1 两次变频射频电视调谐器架构 犉犻犵.1 犃狉犮犺犻狋犲犮狋狌狉犲狅犳犱狅狌犫犾犲犮狅狀狏犲狉狊犻狅狀犜犞狋狌狀犲狉 像的分辨率非常敏感,要得到高清晰的电视图像需 要系统的信噪比很高,这样就对低噪声放大器提出 了非常苛刻的性能要求.因此,前端宽带低噪声放大 器的设计是该系统能否实现的难点和关键.图1中 的射频电视调谐器系统,要求在50~860犕犎狕工作 频率内,低噪声放大器具有良好的输入输出阻抗匹 配特性,最 大 增 益 (犛21 )在 12犱犅 以 上,噪 声 系 数 (犖犉)不高于4犱犅,输入参考三阶交调点(犐犐犘3)大于 3犱犅犿. 3 噪声抵消原理和电路实现 3.1 噪声抵消原理 对于图2中带反馈的共源放大电路[4,5],输入 犕犗犛管 犕1是最主要的噪声源.其漏源噪声电流可 以表示为 犻2 狀,犕1 =4犽犜γ犵犕1 (1) 其中 γ为 犕犗犛管噪声系数;犵犕1为 犕1管的跨导. 图2 噪声抵消技术 犉犻犵.2 犖狅犻狊犲犮犪狀犮犲犾犻狀犵狋犲犮犺狀犻狇狌犲 假设犻狀,犕1方向由漏到源,当犻狀,犕1 流过电阻 犚犉 和 犚犛 所组成的串联回路时,在 犅 点和 犃 点分别产 生噪声电压狏狀,犅和狏狀,犃 狏狀,犅 =-犻狀,犕1(犚犛 +犚犉) (2) 狏狀,犃 =-犻狀,犕1犚犛 (3) 输入信号源狏犻 在 犃 点产生信号电压狏狊,犃,经过 犕1管和电阻 犚犉 组成的共源放大电路放大后,在 犅 点得到信号电压 狏狊,犅.通过交流小信号电路分析可 以得到 狏狊,犅 = (1-犵犕1犚犉)狏狊,犃 (4) 可见,犃 点和 犅 点的信号电压相位相反,而噪 声电压相位相同.通过一个电压增益为-犃犞 的辅 助放大器将 犃 点的电压放大到 犆 点,调整-犃犞 的 大小可以使得 犅 点和 犆 点噪声电压幅值相同而相 位相反.再将 犅 点和 犆 点的电压相加,则在输出端 噪声电压被完全抵消,而信号电压由于相位相同得 到增强. 图3中的狀犕犗犛管 犕2和 犕3可实现放大电路 -犃犞 和信号相加的功能.犕2管起共源放大作用; 犕3管是 犕2管的有源负载,同时起源极跟随器的 作用,将 犅点的信号传输到输出端;犚犔 为50Ω 负载 阻抗. 图3 电路实现 犉犻犵.3 犆犻狉犮狌犻狋犻犿狆犾犲犿犲狀狋犪狋犻狅狀 假设 犕1,犕2和 犕3的输出电阻狉狅 均为无穷 大,通过小信号电路分析可以得到电路的输入阻抗 和输出阻抗分别为 犚犻 ≈1/犵犕1 (5) 犚狅 ≈1/犵犕3 (6) 2030