正在加载图片...

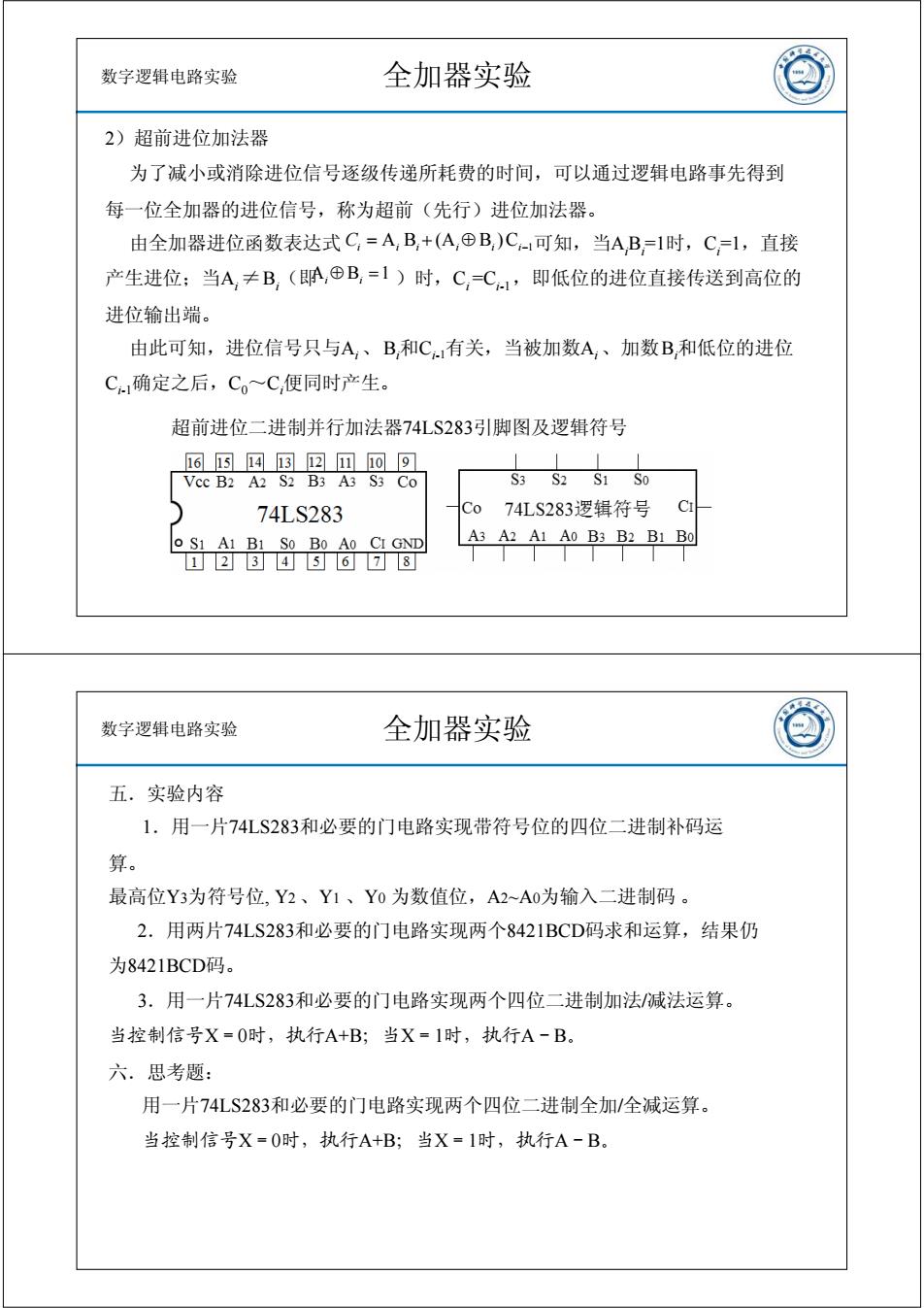

数字逻辑电路实验 全加器实验 2)超前进位加法器 为了减小或消除进位信号逐级传递所耗费的时间,可以通过逻辑电路事先得到 每一位全加器的进位信号,称为超前(先行)进位加法器。 由全加器进位函数表达式C,=A,B,+(A,⑧B,)C可知,当AB=1时,Cl,直接 产生进位;当A≠B,(即A®B,=1)时,C,=C,即低位的进位直接传送到高位的 进位输出端。 由此可知,进位信号只与A,、B,和C有关,当被加数A,、加数B,和低位的进位 C确定之后,Co~C,便同时产生。 超前进位二进制并行加法器74LS283引脚图及逻辑符号 6函网3回▣@9 Vcc B2 A2 S2 B3 A3 S3 Co S3 S2 S1 So 74LS283 Co 74LS283逻辑符号C o S1 A1 B1 So Bo A0 CI GND A3 A2 A1 A0 B3 B2 B1 Bo 23456⑦8 数字逻辑电路实验 全加器实验 五.实验内容 1.用一片74LS283和必要的门电路实现带符号位的四位二进制补码运 算。 最高位Y3为符号位,Y2、Y1、Y0为数值位,A2~A0为输入二进制码。 2.用两片74LS283和必要的门电路实现两个8421BCD码求和运算,结果仍 为8421BCD码。 3.用一片74LS283和必要的门电路实现两个四位二进制加法/减法运算。 当控制信号X=0时,执行A+B;当X=1时,执行A-B。 六.思考题: 用一片74LS283和必要的门电路实现两个四位二进制全加/全减运算。 当控制信号X=0时,执行A+B;当X=1时,执行A-B。数字逻辑电路实验 全加器实验 2)超前进位加法器 为了减小或消除进位信号逐级传递所耗费的时间,可以通过逻辑电路事先得到 每一位全加器的进位信号,称为超前(先行)进位加法器。 由全加器进位函数表达式 可知,当Ai Bi =1时,Ci =1,直接 产生进位;当Ai ≠Bi (即 )时,Ci =Ci-1,即低位的进位直接传送到高位的 进位输出端。 由此可知,进位信号只与Ai 、Bi 和Ci-1有关,当被加数Ai 、加数Bi 和低位的进位 Ci-1确定之后,C0~Ci 便同时产生。 Ci ii i i i = +⊕ A B (A B )C −1 AB1 i i ⊕ = 超前进位二进制并行加法器74LS283引脚图及逻辑符号 数字逻辑电路实验 全加器实验 五.实验内容 1.用一片74LS283和必要的门电路实现带符号位的四位二进制补码运 算。 最高位Y3为符号位, Y2 、Y1 、Y0 为数值位,A2~A0为输入二进制码 。 2.用两片74LS283和必要的门电路实现两个8421BCD码求和运算,结果仍 为8421BCD码。 3.用一片74LS283和必要的门电路实现两个四位二进制加法/减法运算。 当控制信号X=0时,执行A+B;当X=1时,执行A-B。 六.思考题: 用一片74LS283和必要的门电路实现两个四位二进制全加/全减运算。 当控制信号X=0时,执行A+B;当X=1时,执行A-B