正在加载图片...

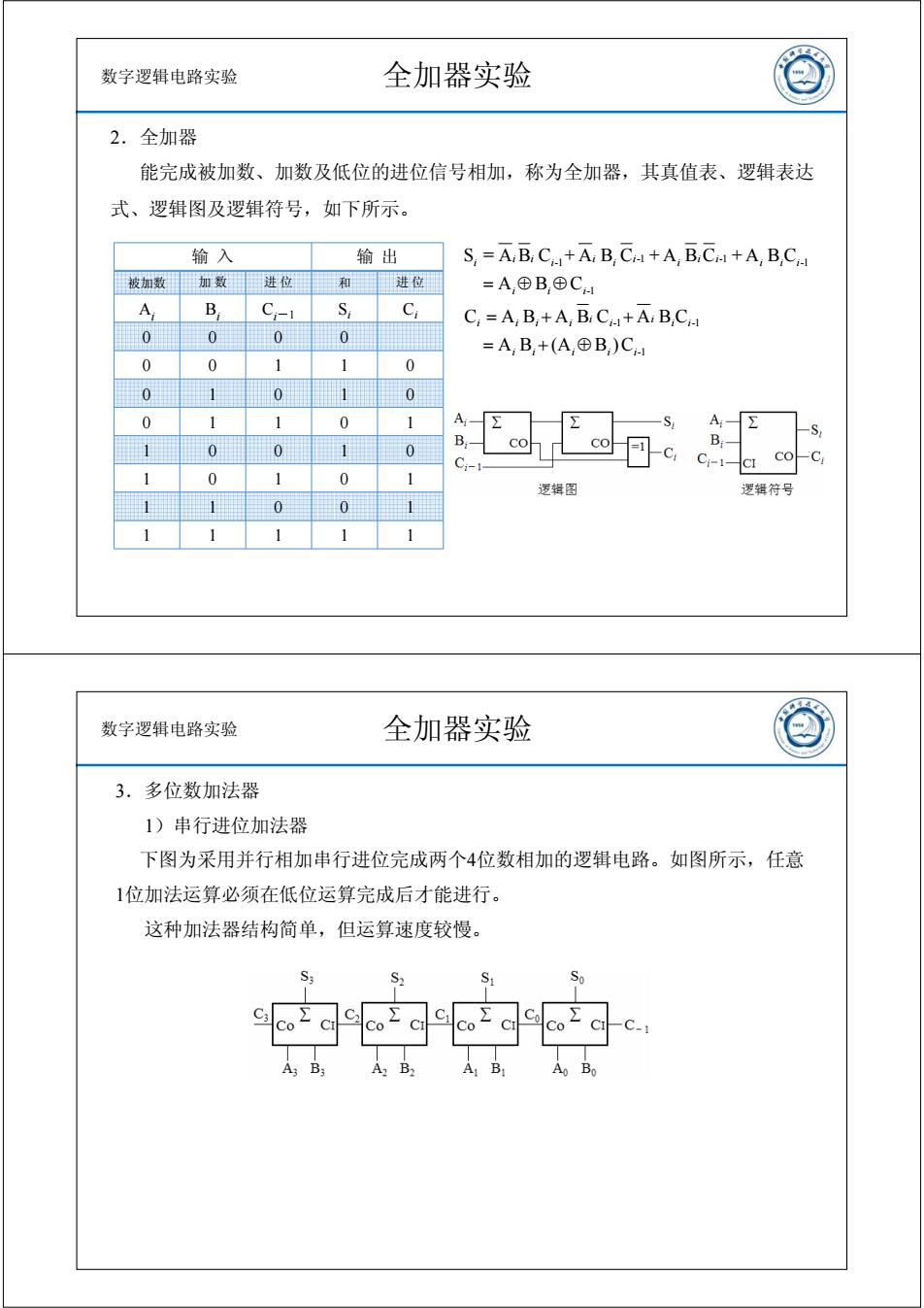

数字逻辑电路实验 全加器实验 2.全加器 能完成被加数、加数及低位的进位信号相加,称为全加器,其真值表、逻辑表达 式、逻辑图及逻辑符号,如下所示。 输入 输出 S,=A,B,C+A,B,C+A,B.C+A,B.C 被加数加数进位 和 进位 =A,⊕B,⊕C A B C S; C C=A,B,+A,B:C+A B,C 0 0 0 0 =A,B+(A,©B)C 0 0 1 1 0 0 1 0 0 0 1 1 0 1 N B co -S) 1 0 0 0 0 0 1 逻辑图 逻辑符号 0 0 数字逻辑电路实验 全加器实验 3.多位数加法器 1)串行进位加法器 下图为采用并行相加串行进位完成两个4位数相加的逻辑电路。如图所示,任意 1位加法运算必须在低位运算完成后才能进行。 这种加法器结构简单,但运算速度较慢。 Co C_ A B数字逻辑电路实验 全加器实验 2.全加器 能完成被加数、加数及低位的进位信号相加,称为全加器,其真值表、逻辑表达 式、逻辑图及逻辑符号,如下所示。 输入 输出 被加数 加 数 进 位 和 进 位 Ai Bi Ci-1 Si Ci 0 0 0 0 00110 0 1 0 1 0 01101 1 0 0 1 0 10101 1 1 0 0 1 11111 1 1 1 1 1 1 1 1 S =A B C +A B C +A BC +A BC ABC C A B A B C A BC A B (A B )C ii i i i- i- i i- i i i i ii i ii i i i i i i- i ii i i i i- = ⊕⊕ =+ + = +⊕ 数字逻辑电路实验 全加器实验 3.多位数加法器 1)串行进位加法器 下图为采用并行相加串行进位完成两个4位数相加的逻辑电路。如图所示,任意 1位加法运算必须在低位运算完成后才能进行。 这种加法器结构简单,但运算速度较慢